Ghodssi R., Lin P., MEMS Materials and Processes Handbook

Подождите немного. Документ загружается.

854 S.J. Cunningham a nd M. Kupnik

Fig. 11.21b. This process produced low-loss feedthroughs at <0.1 dB at 10 GHz.

Finally, the polyimide encapsulated, Kapton substrate passed an 85% RH, 85

◦

C,

10,000 h test with air bridges.

11.4 Direct Comparison of Wafer Bonding Techniques

The type of bonding that is used will be determined by many factors: materials,

surface roughness and topography, temperature or pressure limitations, and product

requirements. In Table 11.3, a summary of wafer bonding techniques is presented.

11.5 Bonding of Heterogeneous Compounds

The bonding of heterogeneous materials includes wafer bonding of lattice mis-

matched materials, which is important because these heterogeneous devices cannot

be formed by other methods. Wafer bonding enables the integration of GaAs/InP,

InP/Si [51], GaAs/Si, and GaAs/GaN. Eom et al. [52] have described the forma-

tion of YBa

2

Cu

3

. The integration of these heterogeneous structures has allowed the

production of light-emitting diodes, vertical cavity lasers, avalanche photodiodes,

vertical couplers, and heterojunction bipolar transistors (HBTs). It is possible to

wafer-bond GaAs to another GaAs wafer or other material [53–55], which increases

the technological opportunities. This provides the flexibility to design enhanced

optoelectronic systems. The bonding of wafers to sapphire has been described by

Kopperschmidt et al. [56] and the construction of strained layers is described by

Taraschi et al. [57–59].

The bonding of GaAs wafers has been described by Akatsu et al. [60], who have

pursued more moderate direct bonding conditions to improve the bonding process

for GaAs. In a typical direct bonding process, high anneal temperatures are used to

increase the bond strength between two wafers. But this approach with GaAs can

compromise the integrity of the interface such that gallium or arsenic oxides may

be enclosed by bubbles that form as part of the decomposition of absorbates. The

high temperatures have been between 400 and 975

◦

C for a few hours to 20 h in an

inert or reducing atmosphere. Another issue with the high anneal temperatures is

the thermal mismatch between dissimilar materials such as GaAs and silicon. The

high mechanical load will cause structural damage and make it difficult to scale the

process to whole wafers. Typical mechanical loads of up to 40 kg/cm

2

have been

used.

A major challenge for GaAs bonding is cleaning the surfaces because of the

complexity of removing the oxides of Ga and As at the same time. The native oxides

of Ga and As exist on the wafer surface when exposed to air and coexist with carbon

contaminants and absorbed water. The water can be removed by low-temperature

heating and the oxides can be desorbed above 580

◦

C. The carbon contaminants are

not removed by thermal cleaning but can be removed by atomic hydrogen in an ECR

(electron cyclotron resonance) plasma.

11 Wafer Bonding 855

Table 11.3 Wafer bonding methods, conditions and applications

Wafer bonding

method Bonding conditions

Advantages

disadvantages Applications

Direct bonding RT-1200

◦

C

No-small pressure

+ High bond strength

+ Hermetic

+Hightemperature

compatibility

– High surface flatness

requirements

–Hightemperature

incompatible with

integrated CMOS

process

SOI wafer fabrication

Heterogeneous

structures

Anodic bonding 150–500

◦

C

200–1500 V

Electrostatic pressure

No mechanical

pressure

+ High bondstrength

+ Hermetic

+ Resistant to high

temperature

– Bond temperature and

high voltage are not

compatible with CMOS

wafers

Sensor packaging and

fabrication

Solder bonding 150 – 450

◦

C

Low bond pressure

+ High bond strength

+ Hermetic

+ Compatible with CMOS

wafers

– Solder flux

Flip-chip bumping

Hermetic sealing

Eutectic bonding 200–400

◦

C

Low to moderate

bonding pressure

+ High bond strength

+ Hermetic

+ CMOS c ompatible

– Native oxide sensitivity

Hermetic sealing

Thermocompression

bonding and

metal–metal

bonding

350–600

◦

C

100–850 MPa (high

bond pressure)

+ Hermetic

+ CMOS c ompatible

– High bonding pressure

– High surface flatness

Hermetic sealing

Wire bonding

Flip-chip bumping

3-D ICs

Ultrasonic bonding RT – 250

◦

C

High bond pressure

+ CMOS compatibility

– Only small bond area

demonstrated

Wire bonding

Low temperature

melting glass

bonding

400–1100

◦

C

Low–moderate

bonding pressure

+ High bond strength

+ Hermetic

– CMOS compatibility

Hermetic sealing

Adhesive bonding RT–400

◦

C + High bond strength

+ Low bond temperature

+ Substrate material

diversity

+ CMOS c ompatible

– Not hermetic

– Temperature stability

3-D ICs

Temporary bonding

MEMS packaging

856 S.J. Cunningham a nd M. Kupnik

The cleaning of GaAs wafers begins with the desorption of arsenic oxides by

heating to produce a Ga-rich surface. The arsenic oxide can be removed by the heat-

ing but also by the hydrogen cleaning. The hydrogen cleaning follows the process

As

2

Ox + 2xH·→xH

2

O ↑+As

2

(1/2As

4

) ↑, where x = 1, 3, or 5 representing

the various arsenic oxides. The Ga oxide is decomposed in the following process

Ga

2

+4H·→Ga

2

O(↑) +2H

2

O ↑. The remaining Ga

2

O is volatile at temperatures

above 200

◦

C but temperatures above 350–400

◦

C are preferred so the Ga

2

O is reli-

ably desorbed. In Table 11.4, a preferred direct bonding process is provided. The

preferred process of Table 11.4 includes the thermal cleaning with atomic hydrogen

and a low bonding temperature of 150

◦

C. When the wafers were thermally cleaned

(400

◦

C for 30 min) in a H

2

or UHV (ultrahigh vacuum) process, the wafers had low

bond strength or formed no bond with a bonding temperature of 350

◦

C.

Table 11.4 GaAs direct bonding process

Process step Process parameters

Wafer cleaning Thermal and hydrogen clean >350

◦

C

Cleaning time 30 min

Bonding temperature 150

◦

C

Bonding force 0 N/m

2

Bond energy 0.7–1.0 J/m

2

11.6 Wafer Bonding Process Integration

11.6.1 Localized Wafer Bonding

A key requirement of the bonding process to achieve a strong and hermetic bond

is the temperature. In a conventional bonding process the entire wafers (substrate,

lid, and interface) are raised to a uniform temperature. The temperature depends

on the process: 1000

◦

C for silicon-to-silicon fusion bonding, 300

◦

C for silicon-to-

glass anodic bonding, 363

◦

C for Au–Si eutectic bonding, or 450

◦

C for glass frit

bonding. These temperatures are too high for many MEMS material systems or

when the MEMS process includes integrated electronics. The integration of MEMS

and CMOS using wafer bonding has been described by Farrens et al. [61], Lin et al.

[62], Parameswaran et al. [63], Sedkey et al. [64], Van der Groen et al. [65], Frazier

[66], and Ghodssi et al. [67]. This means the global temperature of the bonding

process needs to be lowered or that the high temperature needed for bonding should

remain localized to the bonding interface so that temperature-sensitive structures are

not heated to a high temperature. In this section, we discuss the processes that have

been developed with localized heating and bonding to encapsulate MEMS devices.

Cheng et al. [68–70] describe both direct and indirect localized heating and bonding.

In direct bonding, the heater material also acts as the bonding and sealing material

[71–74]. In indirect bonding, the heating element is preserved during the heating

11 Wafer Bonding 857

and bonding process because a separate material is used as the bonding and sealing

material [75].

Cheng et al. [68, 70] have demonstrated localized silicon fusion bonding between

an insulated silicon substrate and a glass wafer (7740 Pyrex). The insulated silicon

substrate will contain the MEMS devices and could contain integrated electronics.

Electrical and thermal isolation are provided on the silicon substrate by a nominal

0.8 μm silicon dioxide layer. For fusion bonding, polysilicon is used as the micro-

heater and seal material. It is nominally 1.0 μm thick, 5 μm wide, and forms a closed

ring that defines the bond region. Two electrical taps are made from the microheater

to provide connection to the current source. The microheater is provided an input

current of 31 mA to develop a local temperature of about 1300

◦

C, which is above

the Pyrex softening point of 820

◦

C and close to the polysilicon melting point. This

process takes about 5 min and is performed witha1MPapressureapplied to the

parts. In a conventional fusion bonding process, where t he entire substrate is heated,

the bonding temperature is typically over 1000

◦

C for approximately 2 h. In a sec-

ond experiment Cheng et al. [68] found that raising the local temperature to 1000

◦

C

for 30 min, when the current was 29 mA resulted in a bond of lower strength and

quality.

In addition, Cheng et al. [68, 70] demonstrated a localized Au–Si eutectic bond-

ing process between the insulated silicon device substrate and a silicon lid. In this

case, the microheater material was Au, and 5 μm wide and 0.5 μm thick. It is

provided a current of 0.27 A for 5 min, which raised the local temperature to an esti-

mated 800

◦

C. During the bonding process, the Au diffused into the silicon to form

the bond and seal. The diffusion and solubility of Au in Si increase with increasing

temperature. The local heating process provides a higher temperature (800

◦

C) than

a more conventional Au–Si eutectic process performed at about 410

◦

C for 20 min.

The local heating process was shown to provide a more uniform, higher strength,

and higher quality bond than the conventional process.

11.6.2 Through Wafer via Technology

Why are we discussing through wafer via technology in this chapter on wafer bond-

ing? The answer depends on the reason for using the wafer bonding process. If the

wafer bonding process is being utilized to fabricate a heterogeneous wafer stack,

such as SOI or InGaAs/Si, or to transfer one thin-film to another wafer or hetero-

geneous wafer stack then the through wafer via technology does not need to be

considered, which is not to say that the through wafer via technology does not apply

to these heterogeneous wafers. The through wafer via technology should be consid-

ered whenever electrical connections are required for a multitude of active electrical

devices. We discuss the important considerations when integrating wafer bonding

and through wafer vias (TWV), which have been referred to as TSV (through silicon

via, which is rather limiting) and TWI (through wafer interconnects).

Why are we developing through wafer interconnect technologies? One reason is

to increase the density of devices on the MEMS substrate. One of the reasons for

858 S.J. Cunningham a nd M. Kupnik

developing through wafer interconnects is to achieve high-density interconnections

with a smaller footprint. This is because the dies rapidly become bond pad limited

or wire bond limited, if all of the bond pads are placed at the perimeter of the die.

With the through wafer interconnects, the electrical connection can be made directly

to the bottom of the MEMS device for the purpose of actuation or to the RF ports of

the RF MEMS component. The die can now be directly bonded to a substrate using

a solder reflow or thermo-compression process.

Another case for through wafer interconnects was described in the Ford

Microelectronics process, which describes perimeter bond pads that are exposed

by wafer dicing following the wafer-level encapsulation process. The wafer saw

exposure of the bond pads is eliminated by using the through wafer interconnect

technology. A second reason is reliability. The through wafer interconnect process

is associated typically with a wafer-level encapsulated MEMS device. Because of

the through wafer interconnect process, the MEMS device is protected during any

and all backend processes, such as wafer saw, wafer grinding, plastic encapsulation,

flip-chip mounting and underfill, solder reflow, shipping, and handling. This means

fewer opportunities to introduce contaminants (e.g., photoresist protect films and

other particles).

As discussed previously, the electrical interconnects or transmission lines can be

fabricated across the wafer and pass through a space defined as the bond/seal region

between the substrate and the lid or can be fabricated through the wafer as described

in this section. The through wafer interconnects take on two basic configurations.

The first configuration fabricates the TWI through the substrate upon which the

MEMS devices are built. This process in theory can be implemented by fabricating

the TWI before or after the MEMS fabrication. The second configuration fabricates

the TWI through the lid wafer. In this latter case, the TWI can be fabricated before or

after the lid is bonded to the device wafer. Whether the TWIs are fabricated through

the lid or the substrate, there are many different ways to implement the various

processes.

Surface interconnects/transmission lines pose many challenges beyond the sim-

plicity of their deposition and patterning. The first challenge is topography created

by the interconnect that may have a thickness of 0.5 μm for a standard CMOS AlCu

layer. The topography poses greater challenges for the direct bonding methodologies

because these require low topography and low surface roughness. The topogra-

phy will need to be addressed by the deposition of a dielectric film to encapsulate

the electrical interconnect. In a subsequent step, a chemical-mechanical polish-

ing is performed to eliminate the topography of the interconnect. The next step

is the preparation of the polished surfaces and finally direct bonding of the wafers.

Because the interconnect will be encapsulated in a dielectric material for electri-

cal isolation from the bonded wafers, this will determine the selection of dielectric

materials and the selection of the direct bonding technique. The surface topogra-

phy is more easily addressed by wafer bonding with intermediate layers, which will

eliminate the need for planarization by CMP. If the intermediate layer is a dielectric,

such as a glass frit, polymer (BCB), or adhesive, the intermediate layer will provide

the dielectric isolation between the interconnect and the bonded wafer.

11 Wafer Bonding 859

If the intermediate layer bonding is based on a metal eutectic or a solder, the

topography will need to be addressed in a similar manner. Solder bonding will

accommodate the surface topography easily, but the solder will form an electri-

cal contact to the interconnect unless it is encapsulated in an insulating layer. In

some cases it may be desirable to form an electrical contact to the seal ring such as

grounding the seal ring for some RF applications. If electrical isolation is required,

the interconnects can be encapsulated in an insulating film that is planarized as we

described for the direct bonding process. This process sequence will be required for

intermediate bonding by eutectic formation, because the eutectics (e.g., Si–Au) do

not accommodate the surface topography. If the interconnect is encapsulated in the

dielectric it is still possible to form an electrical connection of the conductive seal

ring by forming a short via through the thin dielectric to the interconnect.

The second challenge for surface interconnects is the electrical isolation or con-

tact, which has been described in the previous paragraph as part of the solution to

bond over the surface topography.

The third challenge is the formation of an hermetic seal because it is possible the

interconnect will provide a leakage path, moisture, or gas. It is important that the

dielectric i solation layer, solder, or glass frit form a conformal coverage of the inter-

connect topography, which means an absence of voids parallel to the interconnect

sidewall between the sidewall and the intermediate layer.

The fourth challenge is the exposure of the electrical contact pads for wirebond-

ing or solder bumping. This process has been described earlier as part of the Ford

Microelectronics process. This involves providing a cavity on the bonded wafer that

aligns to the electrical pad on the base wafer. Once the bond is formed the pads can

be exposed by the use of a wet chemical etch, a plasma etch, or DRIE, or by saw

exposure. These have all been used successfully, but the DRIE and sawing enable a

well-controlled high-aspect-ratio exposure. The wet etch is usually isotropic which

leads to very large pad openings and therefore die.

We have described electrical interconnects that are patterned on the surface of

the wafer and through the bonded area and that are fabricated through the wafer. We

next describe the similar challenges that relate to TWIs that are fabricated through

the device wafer or through an encapsulation wafer. The first challenge of surface

interconnects is the surface topography, which is not a typical challenge for the

TWIs. The second challenge is the electrical isolation of the TWIs. The isolation

of the TWI from the bonded wafer or seal ring is easily accomplished by blanket

dielectric films that may not require CMP. If it is necessary to connect a TWI to a

conductive seal ring, this can be fabricated with a short damascene via described

above. The isolation of the TWI from the via sidewalls is often accomplished by

deposited dielectric that provides the best isolation for a greater thickness. Because

the dielectric constant (4 for silicon oxide) is relatively large, the coupling can

be high depending on the thickness. Air isolated TWIs have been developed, that

replace the silicon oxide with air that has a dielectric constant of approximately 1.

The air isolated TWIs will reduce parasitic capacitance coupling by a factor of 4.

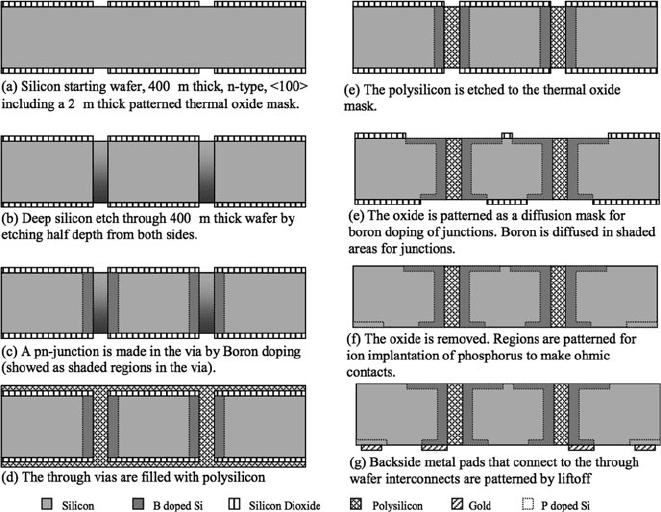

A through wafer interconnect process was developed at Stanford so that they

could create a high density array of cantilevers as demonstrated by Chow et al. [76].

860 S.J. Cunningham a nd M. Kupnik

Without the through wafer interconnects, the cantilever density is limited because of

the need for area t o place bond pads and route electrical interconnects. Additional

goals included flip-chip integration of MEMS device die and integrated circuit die,

low parasitic capacitance using reverse-biased PN junctions, and low resistance

achieved with high-conductivity polysilicon.

This process was demonstrated on 400 μm thick n-type, <100> silicon wafers.

A2μm thick thermal oxide is used as a mask on both s ides of the wafer for etch-

ing the through wafer vias (Fig. 11.22a). The deep silicon etch is performed by

etching halfway through the wafer from both sides. In this manner, it is possible to

achieve a via with a 20:1 aspect ratio (Fig. 11.22b). With the oxide mask remaining

in place, the silicon is boron doped to fabricate a pn-junction (Fig. 11.22c). Next,

the vias are filled with polysilicon (Fig. 11.22d) that is etched back to clear the

oxide via mask and the vias (Fig. 11.22e). The oxide is repatterned to form boron

doped junctions on the front and back surfaces of the wafer. After the oxide mask is

etched, a mask pattern is used to form isolated ohmic contacts by implanting phos-

phorus (Fig. 11.22f). The fabrication process is completed by liftoff patterning of

Au contacts on the doped junctions (Fig. 11.22g).

In this process, they were able to achieve a 0.05 pF parasitic capacitance with a

reverse-biased (10 V) pn-junction. This compares to 0.28 pF for a metal-insulator-

semiconductor (MIS) isolation system. The series resistance was 900 and the

leakage current was measured to be 7 nA.

Fig. 11.22 Through wafer interconnect fabrication process using isolated polysilicon vias

11 Wafer Bonding 861

A second through via process used a high-density low pressure (HDLP)

SF

6

/C

4

F

8

plasma to create via holes through a p-type, 4 in., 525 μm thick, 10

cm, double-side polished silicon wafer. The via holes were square with dimensions

of 30 μm/side, which resulted in an aspect ratio of 17.5:1. A 1 μm thick thermal

oxide was grown at 1100

◦

C for an isolation layer. A 1.5 μm thick low pressure

chemical vapor deposited (LPCVD) polysilicon was deposited as an adhesion layer

for a subsequent copper layer that had poor adhesion to the thermal oxide. Next a

250 nm CVD copper layer was deposited as a seed layer for the 6 μm thick electro-

plated copper. The through wafer interconnect resistance was further reduced by the

6 μm thick electroplated copper with a sheet resistance of 2.8 m/cm. This process

resulted in vias with ultralow resistance of 50 m/via.

Following the thick Cu deposition, a 7 μm thick photoresist (Shipley PEPR 2400)

was electroplated for the subsequent patterning of the Cu and polysilicon. The Cu

and polysilicon were wet etched and dry etched in SF

6

plasma, respectively. Finally

the electroplated photoresist was removed to expose the isolated vias.

The process used to develop through wafer interconnects for MEMS applications

is based on etching high-aspect-ratio holes through the silicon wafer, depositing an

insulation layer, and depositing a conductive layer. The insulation layer will provide

electrical isolation of the conductive vias from the silicon wafer.

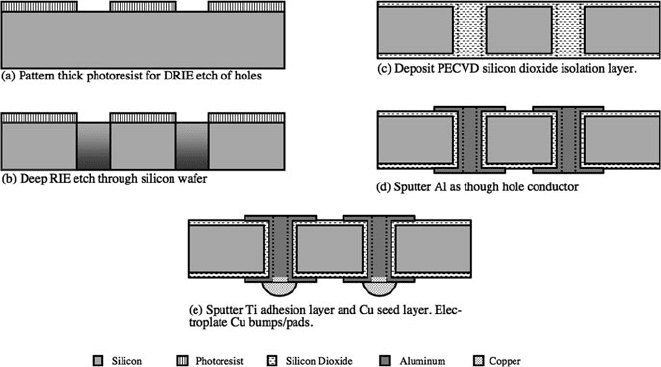

It was demonstrated in a process with 50, 75, 100, and 200 μm diameter vias

through a 525 μm thick 4 in. p-type, <100> silicon wafer. The vias were pat-

terned with a thick photoresist (AZ 4620 at 20 μm thick, and AZ 400 K developer)

(Fig. 11.23) and etched with a deep inductively coupled plasma etcher (Fig. 11.23b).

Then PECVD silicon dioxide was selected for the isolation layer (Fig. 11.23c). It

was deposited by sputtering because of the improved step coverage. The silicon

Fig. 11.23 Through wafer via process

862 S.J. Cunningham a nd M. Kupnik

dioxide was deposited to approximately 7000 Å, which is difficult to measure on

the sidewalls because of the surface roughness.

The conductive layer was demonstrated by two approaches. In the first approach,

a thin aluminum was sputtered from both sides of the wafer to achieve 1 μmon

the surface and approximately 2000 Å on the sidewall (Fig. 11.23d). In the sec-

ond approach, copper was electroplated as the conductor. This required 1500 Å

of titanium to be deposited first as an adhesion layer between the copper and the

silicon dioxide. The copper and titanium patterning was completed by etching in

H

2

O(80%) +H

2

SO

4

(10%) +H

2

O

2

(10%) and in H

2

O(90%) +HF(10%) to remove

the copper and titanium, respectively (Fig. 11.23e).

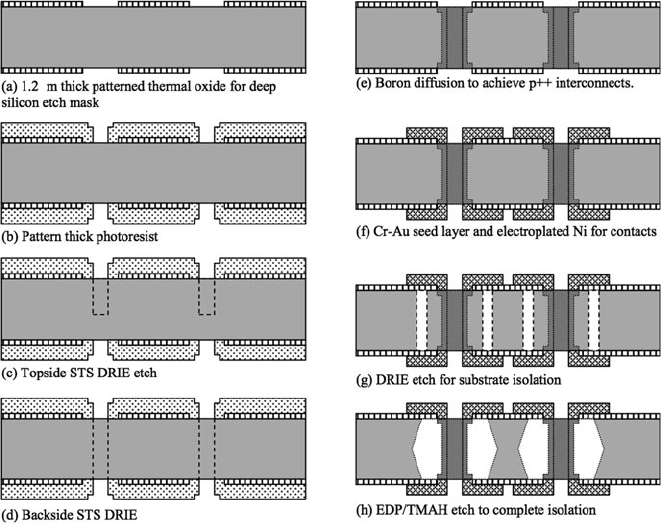

The primary goal of the next process (Fig. 11.24) was to improve the resistance

and parasitic capacitance of through wafer interconnects. The improvements are

in direct comparison to the dielectric isolated metal or polysilicon and to the pn-

junction, reverse-biased through wafer interconnects. The improvements will come

from air gap isolated interconnects.

The process begins in a typical fashion for etching deep high-aspect-ratio vias

through a silicon wafer. First, a 1.2 μm thermal oxide is grown and patterned to

be used as deep silicon etch mask (Fig. 11.24a). Also, the thermal oxide provides

isolation between the metallized via and the silicon substrate. In addition, a thick

Fig. 11.24 AirisolationTWIprocess

11 Wafer Bonding 863

photoresist (16 μm AZ9260) is deposited and patterned as the deep silicon etch

mask (Fig. 11.24b). Similar to other processes, the deep RIE is performed from the

topside and backside to define a high-aspect-ratio through wafer via (Fig. 11.24c,d).

The topside and backside etches were both targeted for 150 min to etch 250 μm

deep. Following the via etch, the thick photoresist is stripped.

The via interconnects are fabricated by doping the via silicon with boron during

a 6 h diffusion process that produces a 12–15 μm p++ region (Fig. 11.24e). The

next steps are associated with fabricating metal electrical contacts to the p++ inter-

connect (Fig. 11.24f). First, a Cr–Au seed layer is deposited for electroplating an

8–10 μm thick Ni contact layer. An alternate DRIE is performed to create isolation

between the p++-doped interconnect and the substrate (Fig. 11.24g). The isolation

is enhanced by an anisotropic wet silicon etch (EDP, TMAH, or KOH) to complete

the air gap isolation (Fig. 11.24h).

The University of Michigan design/process achieved a 27 series resistance

(this compared to calculated 4. series resistance that was attributed to necking of

the doped interconnect) and a 10 fF parasitic capacitance. The parasitic capacitance

is dominated by the Ni contact frames that couple to the silicon substrate through

the 1.2 μm thick oxide.

11.7 Characterization Techniques for Wafer Bonding

The characterization of the wafer bond is either destructive or nondestructive.

Nondestructive techniques include imaging techniques to examine the bond inter-

face or to evaluate voids in the bond interface that are distributed across the wafer.

Destructive techniques include cross-section analysis and bond strength evalua-

tion. The nondestructive techniques can be used as an in-process or end-of-line

evaluation. The destructive techniques are used at end-of-line. The assessment of

bond quality includes defect rate, bond strength, stresses [77], bond energies [78],

hermeticity (if used for packaging), materials, and harsh environments [79].

The nondestructive imaging techniques include optical microscopy, infrared

microscopy, acoustic microscopy [80], white light interferometry, secondary ion

mass spectroscopy (SIMS), transmission electron spectroscopy (TEM), multiple

internal reflection spectroscopy [81], and X-ray topography. Optical microscopy

will require one of the wafers to be optically transparent so that defects, voids

[82, 83], and contaminations can be identified through one wafer to the interface.

Optical microscopy is an efficient and inexpensive means of inspection. The infrared

imaging mounts the bonded wafers (transparent to IR such as silicon) above an IR

source and in the path of an IR-sensitive camera. Interfacial bond defects will show

up as changes in contrast in the IR image and appear to have a “Newton’s rings”

pattern. The resolution of this technique is limited to about

1

/

4

of the wavelength of

the I R source. For the typical source this resolution is several mm. This technique

will not identify voids that are identified by other techniques. IR imaging resolution

is further limited by high doping levels, IR absorbing films, and by rough surfaces.