Ghodssi R., Lin P., MEMS Materials and Processes Handbook

Подождите немного. Документ загружается.

1054 M.A. Huff et al.

may perform the fabrication of microelectronics on substrates and then send the

substrates to a MEMS foundry that performs the MEMS fabrication.

The business benefits of such an approach can be quite significant. First, it avoids

the huge development costs associated with developing a standalone microelectron-

ics process. Second, it avoids the problem of matching the production capacity for

microelectronics with that of the MEMS devices, which can be difficult. Third,

it allows continuous access to state-of-the-art microelectronics process technolo-

gies without incurring the enormous development and capital costs that this would

involve.

Given the difficulty, cost, and risk associated with the approach of complete

customization it should be obvious that the first step of any MEMS development

activity should be to determine if an existing process technology can be used or

leveraged (by leveraging we mean to make relatively simple modifications or to

use any portions of an existing process technology) because this will often be

the most efficient and effective approach available. Nevertheless, the leveraging

of existing process technologies in commercial MEMS foundries has frequently

not been a viable option for designers. There are several reasons for this, includ-

ing: (1) most MEMS process technologies in existence were developed by captive

foundries that are not interested in making their capabilities available to outside enti-

ties; (2) MEMS is a relatively new field and has an enormous range of applications

and therefore the number of existing process technologies available is quite limited;

and, (3) most MEMS process technologies in existence were not designed with the

intent to be generic for a range of applications, but instead were developed and opti-

mized for a single device and application area. Historically, the leveraging of an

existing process sequence requires that the intended application be closely aligned

to the original or else the development of a customized process sequence will be

warranted.

We now discuss some of the more detailed technical challenges that arise related

to MEMS process integration.

14.5.1 Topography

In standard front-line CMOS electronics fabrication, thicknesses of the material

layers are very thin, usually on the order of nanometers to tens of nanometers

in thickness. As a consequence, topographies are small and photoresist thick-

nesses can be correspondingly thin. In fact, the thicknesses of photoresists scale

to some degree with the resolution of the linewidths: thinner photoresists must

be used to obtain smaller resolution linewidths. MEMS structures, on the other

hand, often tend to be comparatively thick. This causes photolithographic con-

straints on the device’s planar dimensions and limits the layer-to-layer alignment

accuracy that can be achieved. For example, if one tries to embed MEMS fab-

rication steps into a microelectronics fabrication process sequence to create an

integrated MEMS process sequence, the inherent constraints of the MEMS pro-

cessing steps will add constraints to the electronics processing steps that would

14 MEMS Process Integration 1055

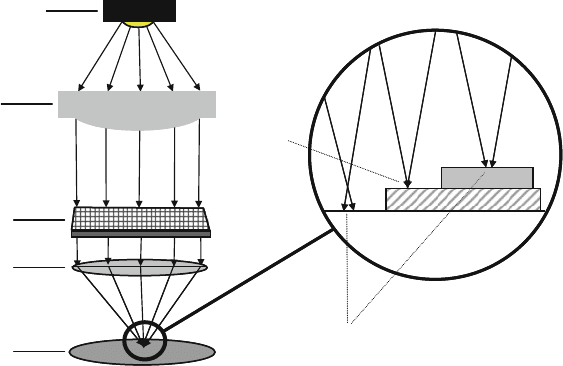

Light Source

Collimator

Mask

Reduction Optics

Wafer

In Focus

Out of Focus

Fig. 14.3 Illustration of how various regions of the photolithographic pattern can be in or out

of focus based on the topography of the substrate surface (Reprinted with permission, copyright

MEMS and Nanotechnology Exchange)

not otherwise occur in the microelectronics process sequence. This is demon-

strated in the illustration below (Fig. 14.3), which shows a projection optical system

being used for photolithography on a wafer. As can be seen in the insert to the

right, even though the mask image is in focus in certain locations, other loca-

tions on the wafer surface are out of focus and this is due to the topology of the

surface.

In addition, the alignment structures typically used in an electronics process are

generally insufficient for the alignment needs of the MEMS layers, so additional

alignment strategies must be designed into the integrated process flow. For exam-

ple, many MEMS processes will pattern and etch the backside of the wafer for a

subsequent through-wafer etching process that requires special alignment marks.

Another common mistake for deep anisotropic etches (e.g., deep RIE) is that any

alignment marks in the silicon can be easily erased during processing. Therefore,

care must be taken to ensure that alignment marks in the silicon will either survive

the etch or the alignment marks are made in a different material layer that will not

be etched.

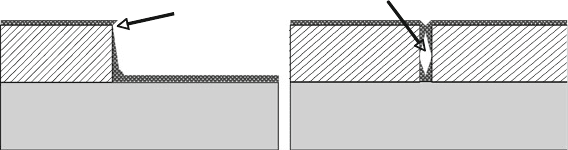

The large topology seen in MEMS fabrication also causes problems with conti-

nuity of layers after thin-film depositions. At the edge of high topology structures

where there is a large dropoff, the material layer after thin-film deposition may be

thinner than in the field regions (Fig. 14.4a). At worst case, there may even be a

discontinuity in the layer across large variations of topography. Additionally, it can

be difficult to obtain a conformal and continuous coverage of a thin film deposition

in the deep high-aspect-ratio trenches that are frequently seen in MEMS fabrication

(Fig. 14.4b).

1056 M.A. Huff et al.

Breakin Thin Film

Void

(a) (b)

Fig. 14.4 Illustration of the problems caused in thin-film deposition during MEMS fabrication

due to the large topography

14.5.2 Material Compatibility

A more difficult process integration challenge is material compatibility. The impor-

tance of this issue is perhaps best illustrated in the case of integrated MEMS

process technologies. Standard CMOS electronics fabrication uses a very limited

set of materials whose electrical properties are very well known. On the other

hand, one of the great strengths of MEMS fabrication is the availability of an

extremely broad and diverse range of material types. The introduction of atypical

materials into a CMOS electronics flow can have dramatic and unforeseen con-

sequences. A classic example is the use of gold. In the MEMS context, gold can

have extremely useful material properties; very high electrical conductivity, very

high thermal conductivity, good surface-to-surface bonding capability, and excel-

lent chemical inertness. However, it does not adhere well to silicon dioxide and it

can poison transistor devices (it is a rapidly diffusing element that causes deep level

traps and degrades the minority carrier lifetime). Therefore, most CMOS foundries

would not permit wafers that have gold on them to be processed on any of the

equipment used for microelectronics fabrication. Moreover, most CMOS foundries

would also not allow wafers that had been processed on equipment that had ever

touched wafers having gold on them to be processed on any of the equipment used

for microelectronics fabrication. This example also illustrates the importance of

partitioning or segregating the process sequence between processing tools used for

microelectronics fabrication from those used for MEMS fabrication (see discussion

below).

Material compatibility is an extremely important issue for nonintegrated MEMS

process sequences as well. Perhaps the most obvious example of this is when the

existing materials on the substrate are modified or destroyed during subsequent pro-

cessing steps to which the materials on the substrate are exposed. For example,

any aluminum metal (commonly used as an electrical interconnect material layer

in microfabrication) that is exposed to potassium hydroxide (KOH) (an often-used

anisotropic wet chemical etchant for MEMS bulk micromachining) will result in the

aluminum being destroyed. Therefore, either another metal, such as gold, or another

etchant solution, such as tetramethylammonium hydroxide (TMAH), or a protective

layer must be used in the process sequence.

14 MEMS Process Integration 1057

It should also be noted that material compatibility issues can be extremely subtle

and difficult to uncover and understand. As an example, a MEMS process sequence

may call for the deposition of a layer of LPCVD silicon nitride over a previously

deposited PECVD glass layer. However, this may result in the blistering of the sili-

con nitride layer due to the outgasing from the CVD glass layer. The solution may

be to anneal the CVD glass layer at a temperature in excess of the silicon nitride

deposition (in fact, it is advisable to perform the anneal at a temperature higher

than any subsequent processing steps in the entire process sequence) in order to

densify and outgas the glass material prior to the deposition of the silicon nitride

layer. As another example, thin-film deposited gold does not adhere well to silicon

dioxide layers. Instead, a thin adhesion l ayer such as chrome needs to be deposited

prior to the gold deposition. As these examples demonstrate, given the enormous

range and diversity of materials and processes used in MEMS, successful handling

and management of process compatibility issues in process integration can be very

challenging.

14.5.3 Thermal Compatibility

Thermal budget, which refers to the temperature level and length of time that a

substrate is exposed to during processing, must also be addressed in MEMS process

integration because it has an enormous impact on the resultant material properties.

Management of the thermal budget is often extremely critical for integrated MEMS

processes. The thermal budget must be carefully controlled in order to maintain

appropriate doping levels in, for example, the CMOS channel. Also, the temperature

of any subsequent processing of microelectronics wafers with metallization must be

performed at low temperatures.

In MEMS fabrication, on the other hand, long, high-temperature annealing steps

are often required to control morphologies of polycrystalline materials or reduce

built-in residual stresses and stress gradients within material layers. Therefore, any

integration of MEMS and electronics process steps requires careful consideration

of the thermal requirements of the transistors and MEMS structures as well as the

materials used to implement them. These requirements often severely restrict the

order in which materials can be deposited in an integrated MEMS process flow. For

example, the use of many metals (as circuit interconnects or as MEMS structural

layers) must occur after any processing steps requiring high-temperature processing.

Thermal compatibility issues are also very important in nonintegrated MEMS

process sequences. As was described above, the properties of MEMS materials on

a substrate can be significantly modified by the subsequent steps in the process

sequence. For example, a thin-film layer of gold that is directly deposited onto sili-

con that is subsequently heated above the gold–silicon eutectic temperature, which

is about 360

◦

C, will alloy with the underlying silicon and appear to have disap-

peared. The gold does not disappear per se, but instead diffuses into the silicon. The

effects of thermal budget are perhaps the most significant determinant of many of

the most important resultant material properties, such as residual stress in a thin-film

used in the implementation of a MEMS device.

1058 M.A. Huff et al.

14.5.4 Circuit/MEMS Partitioning of Fabrication

How the processing steps in a MEMS process sequence are partitioned is very

important. Depending on the restrictions of each individual item of equipment, loca-

tion within a foundry, or from foundry to foundry, there are often issues such as

wafer cleanliness and cross-contamination when transferring wafers among tools

and foundries that must be addressed.

Many MEMS processes are not considered to be compatible with most micro-

electronics processes. As discussed above, MEMS uses a much broader and diverse

(i.e., different) spectrum of materials than microelectronics fabrication and some

of the materials often used in MEMS are known to pose contamination problems

for integrated circuits (e.g., gold). In addition, during processing MEMS wafers

can generate particulates that can degrade the yield of microelectronics processes.

For example, a MEMS process technology may involve the etching of silicon or

some other material to create very thin membranes across the surface of the wafer.

These membranes may be extremely fragile and susceptible to breakage during

subsequent processing. They may even break during normal wafer handling in the

cleanroom. The breakage of membranes on the MEMS wafers would likely create a

large amount of particulate contamination that would be very problematic for wafers

undergoing integrated circuit fabrication. For example, a large amount of particulate

matter on t he surface of the wafer would seriously degrade the yield of any subse-

quent photolithographic process step, and this degradation would increase as the

linewidth resolution is decreased. As a general rule, the process restrictions for inte-

grated circuits will always be more restrictive than for MEMS. Consequently, the

processing equipment used for MEMS fabrication is frequently physically separated

from the equipment used to make integrated circuits for most integrated MEMS

process sequences.

Many microelectronics foundries, as discussed above, are operated as continu-

ous flow manufacturing environments wherein every wafer is processed according

to exactly the same ordered sequence of steps from start to finish. This coupled

with the highly strict controls on contamination and particulates dictates that the

wafers cannot easily be removed from a manufacturing line, have one or more

MEMS processing steps performed, and then reinserted into the integrated circuit

processing line. In contrast, the customized nature of MEMS processing sequences

requires that some wafers are processed according to one process sequence, another

group of wafers are processed according to a different process, and so on. This cus-

tomization usually requires that the wafers jump from one type of process and the

associated equipment tool to another. This has a large impact on the partitioning of

the process and equipment for an integrated MEMS process. Due to the concerns of

contamination and particulates from MEMS processing steps as well as the restric-

tive nature of integrated circuit fabrication, it should be obvious that often the most

practicable approach for integrated MEMS manufacturing is to perform the micro-

electronics fabrication first (i.e., start fabrication within facilities having the strictest

restrictions) and then transfer the wafers to a less restricted foundry (i.e., a MEMS

foundry) wherein the remaining portion of the fabrication is completed.

14 MEMS Process Integration 1059

14.5.5 Tooling Constraints

MEMS fabrication often poses many unique challenges and constraints with respect

to the tooling of the processing equipment used. For example, it is not uncom-

mon in MEMS fabrication to process nonstandard wafers including wafers that are

much thinner or thicker than a standard wafer, wafers that have holes etched through

them, wafers that have extremely fragile structures on their surface, wafers that have

features on both sides of the s ubstrate, wafers that have enormous topology (see dis-

cussion above), or wafers that have nonstandard s hapes (e.g., square or rectangular)

or sizes. MEMS-processed wafers are often micromachined in such a way that the

mechanical stiffness and robustness of the wafer is compromised. Moreover, some

of the micromachined areas create “stress risers” that when combined with the crys-

talline nature of most semiconductor wafers pose significant risk of fracture. This

applies to integrated or nonintegrated MEMS.

Also, much of the semiconductor processing equipment in a modern foundry is

highly automated. For example, a typical foundry processing tool will have a load

lock mechanism wherein a cassette of wafers is placed, a robotic arm that takes the

wafers from the cassette and places them one at a time in a process chamber, and a

wafer chuck that applies a vacuum to the wafer inside the process chamber to hold

it securely prior to the processing step being performed. The attempt to process a

wafer that has previously undergone MEMS (or any micromachining) processing

on such a system without ensuring that the tool will not damage the wafer and vice

versa may result in a catastrophic outcome. For example, a process sequence may

require that a DRIE etch be performed entirely through the whole wafer. However,

inasmuch as many DRIE process tools use backside helium cooling, a through-

wafer etch would result in the helium leaking into the process chamber unless some

remedy were employed. Most often, the device wafer that is being etched is mounted

to another (called handle) wafer while the t hrough wafer is being performed. The

device wafer is then carefully removed from the handle wafer (one hopes) without

breaking it.

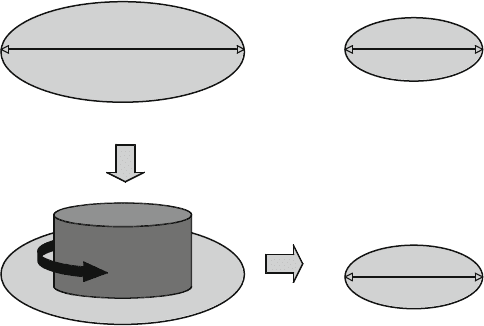

There is often a specific tooling compatibility issue that arises in the case of inte-

grated MEMS process technologies. Most state-of-the-art CMOS foundries produce

microelectronics on wafers that are 300 mm in diameter. In contrast, many of the

specialized MEMS processes are performed on tools that can only accommodate

up to 200 mm diameter substrates, with 150 mm equipment being more common.

Clearly, this presents a problem on how to process a wafer on both CMOS and

MEMS equipment. One solution (which only works for the case where the CMOS

fabrication is performed prior to the MEMS fabrication) is to core out the middle

of the CMOS wafer with a core diameter matched to the MEMS process tools, and

then perform the MEMS fabrication on the cored-out substrate (Fig. 14.5).

Although this may be the best available solution to overcoming this tooling prob-

lem, it does have several disadvantages. A large number of CMOS die will be

unusable and thrown away (essentially the CMOS die within an annular ring having

an outer diameter of the CMOS wafer and an inner diameter equal to the coring

diameter). Also, the wafer coring process removes the beveling of the wafer edges

1060 M.A. Huff et al.

300 mm

150 mm

Typical MEMS Wafer

Typical CMOS Wafer

Coring of CMOS Wafer

150 mm

Cored CMOS Wafer Ready

for MEMS Processing

Fig. 14.5 Coring of CMOS wafer so that it can be processed on MEMS equipment

which help protect against wafer breakage. In short, a MEMS fabricator cannot just

use t he items of equipment that are specified in a process sequence without resolving

the constraints that process equipment tooling presents.

14.5.6 Circuit/MEMS Physical Partitioning

The physical partitioning or separation and location of the MEMS device(s) on the

substrate is also an important consideration. The most important question that must

be answered is whether to develop an integrated or nonintegrated MEMS process

sequence. This decision must be carefully and thoroughly researched and depends

on many factors, some of which are relatively easy to obtain or estimate, whereas

others will require a fair amount of speculation. Some of the factors that must be

considered include: comparing the development cost and time associated with inte-

grating or not integrating MEMS with microelectronics, comparing performance

levels of both approaches to the performance requirements of t he product, compar-

ing the manufacturing costs of both approaches, comparing the capital investments

that would be r equired in both approaches, determining whether there are existing

foundries and process technologies from which to leverage for either approach, the

cost and difficulty of packaging with respect to both approaches, and so on.

In some situations the integration of MEMS with electronics is necessary. We

review a few examples below, such as Texas Instruments’ DLP technology, in which

this is certainly the case given the huge number of mirrors that have to be inde-

pendently controlled. Usually the most prudent approach for integrated MEMS is

to fabricate the microelectronics first and then the MEMS. However, even in the

cases where the microelectronics are fabricated first, the metallization, materials

14 MEMS Process Integration 1061

constraints, dimensions, doping profiles, and the like, of the electronics will place

severe limits on the type of MEMS fabrication that can be performed as well as the

materials that can be employed. Moreover, it will also restrict the substrate material

to whatever the electronics are made from. However, it is often a better choice to

go with a nonintegrated approach wherein the MEMS are fabricated on one sub-

strate and the microelectronics are fabricated on another. Often the two die, the

CMOS die and the MEMS die, are packaged together in what is called a hybrid

package and electrically connected inside the package using wire-bonding or a sim-

ilar technology. The advantages of a nonintegrated approach from the standpoint of

reduced development time, development cost, and risk can be dramatic. However,

there are other, perhaps less obvious, advantages as well. For example, the nonin-

tegrated approach of MEMS fabrication will allow much more design and process

freedom than can be achieved in the integrated MEMS approach. In addition, the

yields of hybrid MEMS can be increased due to the fact that “known good CMOS

and MEMS die” can be preselected for the hybrid package.

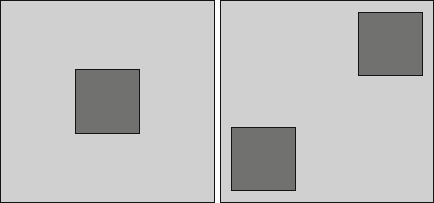

Partitioning as it relates to where the MEMS is located on the die or wafer is

also an important consideration. That is, care must be taken in locating the MEMS

device(s) on the substrate. As an example, consider the limitations concerning par-

titioning of a MEMS device on a die as illustrated in Fig. 14.6. I n this figure (both

left and right) we portray a die (shown in light gray) containing both microelec-

tronics and MEMS on the same substrate wherein the die is larger than the area

consumed by the MEMS sensor device (shown in dark gray). The MEMS device

may be a sensor that is designed and built to be highly sensitive to strains. (Even

if it is not designed as a stress sensor, virtually all MEMS devices are affected by

stress.) When the MEMS die is attached to a package using any common die-attach

technology (e.g., epoxy, solder, etc.), stresses will be applied to the die and these

stresses will likely result in a nonuniform stress field across the die that varies from

the center to the edge of the die. Consequently, it will be a prudent design choice

to locate the MEMS device on the die wherein these die-attach induced stresses

are more uniform, that is near the center of the die (Fig. 14.6, left), as opposed to

MEMS

MEMS

MEMS

Fig. 14.6 Plan view of two integrated MEMS device die. The one on the left has the MEMS device

in the center of the die where the packaging and die attach stresses will be uniformly distributed

to the MEMS sensor. The die on the right has the MEMS devices at the edge of the die and more

prone to the effect of any packaging and die attach stresses

1062 M.A. Huff et al.

locating the MEMS device at the edge of the die (Fig. 14.6, right). As this example

demonstrates, both partitioning and packaging should always be addressed as early

as possible in any MEMS device development effort.

14.5.7 Die Separation, Assembly and Packaging

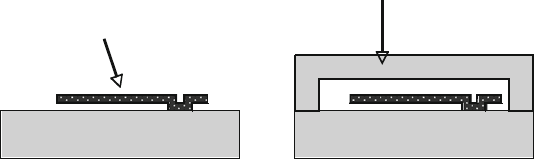

How the wafers with MEMS devices are to be diced, handled, assembled, and pack-

aged also poses challenges for MEMS developers. Often MEMS devices are located

on the surface of the wafer and are extremely fragile once they are released and free

to move (Fig. 14.7a). The standard method in the semiconductor industry of dic-

ing wafers into die using a high-speed diesaw, wherein pressurized water is sprayed

at the location of the cutting action, may not be suitable for a wafer with MEMS

devices. In such situations, some other method to separate the die must be devised,

such as laser cutting. Alternatively, an increasingly popular method is to enclose the

MEMS device inside a sealed cavity using what is termed wafer-scale packaging,

as shown in Fig. 14.7b. This process is performed at the wafer level (i.e., before

die separation) and completely protects the MEMS device during subsequent die

separation, assembly, and packaging procedures. However, this will require the pro-

cess to be designed and developed such that the MEMS device and potentially any

microelectronics are not degraded during the process, and space must be dedicated

on the die to allow the bonding of the capping wafer and the more complex sawing

operation.

Fragile MEMS device

Enclosure that protects MEMS device

(a) (b)

Fig. 14.7 Illustration of fragile MEMS device on the top surface of the wafer that could be broken

during die separation and assembly processes

Automated pick-and-place operations are commonly used in the semiconductor

industry to t ransport the die from a diced wafer to a package or other intermediate

container. Usually they are composed of a movable tube within which a vacuum is

applied to create a suction effect to hold the die on the end of the tube. These types

of assembly machines may not be suitable for die containing MEMS inasmuch as

the mechanical forces (i.e., contact and vacuum pressure from the tube being placed

in contact with the die) may damage or destroy the MEMS devices. Therefore, the

location of the MEMS devices on the die will need to be considered beforehand.

14 MEMS Process Integration 1063

A solution may involve locating the MEMS devices on the die where the wand will

not contact during pick-and-place operations. The disadvantage of this is that it may

require the die to be larger (thereby resulting in a higher cost). Another alternative

may be to use a protective enclosure such as the wafer-scale packaging discussed

above and shown in Fig. 14.7b.

MEMS packaging tends to be much more complex and challenging than that

used in microelectronics, but it must be considered as part of the process integra-

tion effort as well. Although microelectronics are usually sealed within a hermetic

package and completely isolated from the environment with only the electrical leads

penetrating from inside the package to the outside world, a MEMS package must

not only protect the die, but simultaneously must allow the die to interact with the

environment outside of the package in some limited fashion and provide for the

device output signal to be conveyed to the outside world. For example, a MEMS

pressure transducer package must have one or more ports whereby the pressure to

be measured can be applied through the package to the sensor die and also sev-

eral electrical leads from t he die to outside the package. The pressure sensor die is

relatively fragile, therefore the package must also adequately protect the die from

damage during handling and while in use.

Although the microelectronics industry has a standard set of off-the-shelf pack-

aging technologies, the enormous diversity of MEMS device types and applications

combined with the different ways in which the devices interact with the environment

means that MEMS packaging, like the MEMS devices themselves, also tend to be

very customized (and can also be very costly) [1]. Furthermore, the package must

take the output leads, which are usually electrical, from the MEMS device and route

them to the outside of the package in a standardized format that can be connected

to a larger system. Another complication that frequently arises in MEMS packag-

ing that can be illustrated in the example of the pressure sensor is that the pressure

sensor device is highly sensitive to strain, and consequently any strain built into the

sensor as a result of encapsulating a package around the sensor must be appropri-

ately managed. The complexities of MEMS packaging coupled with the fact that

there exists no standard or universal package for MEMS die, often results in the

packaging being one of the most expensive cost elements in MEMS device produc-

tion. Even the use of a conventional package may place many restrictions on the

design of the MEMS device as well as the process sequence used to implement it.

Ultimately, the decisions about die separation, assembly, and packaging of

MEMS devices involve a complex interplay of technical and business analysis and

advisably all should be carefully addressed in concert with the device design and

process sequence early in any development effort.

14.6 How Is Process Integration Performed?

The development of a MEMS process sequence is very hard work and to be suc-

cessful at this endeavor requires the careful balance of creative ideas tempered with

objective and judicious decision making, plus some amount of good fortune (i.e.,