Зайцев А.П. Общая электротехника и электроника. Учебное пособие: Часть II

Подождите немного. Документ загружается.

161

Пока преобразуемое напряжение Uзад меньше выходного напряжения

ЦАП U

цап, на выходе КН напряжение имеет уровень логической 1 и им-

пульсы от синхрогенератора СГ через схему И поступают на вход счетчика

СТ2, который перед началом преобразования должен быть обнулен. СТ2

преобразует последовательность импульсов U

сч в двоичный код, а ЦAП

преобразует этот код в аналоговый сигнал U

цап. Когда выполнится усло-

вие U

цап=>Uзад, на выходе КН установится логический 0, схема И не бу-

дет пропускать импульсы от синхрогенератора (конец преобразования).

Код на выходе СТ2 в этот момент времени будет соответствовать значе-

нию U

зад. Процесс преобразования периодически повторяется.

Если суммирующий счетчик заменить реверсивным, то метод можно

существенно улучшить. В этом случае появляется возможность непре-

рывно отслеживать изменяющееся входное напряжение и сократить время

преобразования. Блок-схема такого АЦП представлена на рис. 9.55, а диа-

граммы, поясняющие его работу, приведены на рис. 9.56.

Рис. 9.55

В схеме применяется компаратор с двумя выходами Н и L (по существу,

два отдельных компаратора КН1 и КН2). Логическая 1 на выходе Н озна-

чает, что напряжение с выхода ЦАП превышает аналоговое входное U

зад

по крайней мере на некоторую величину Q. Логическая 1 на выходе L оз-

начает, что выход ЦАП по

крайней мере на Q ниже входного напряжения.

Появляется «мертвая зона» шириной 2Q, в которой ни на одном из выхо-

дов компаратора нет логической 1. Если U

зад принимает постоянное зна-

чение, то при достижении U

цап напряжения «мертвой зоны» реверсивный

счетчик блокируется по обоим входам и фиксирует код преобразуемого

напряжения. Признаком окончания преобразования является условие:

Н=0, L=0.

СТ2

ЦАП

.

.

.

СГ

ЦАП

U

ЗАД

U

АЦПВыход

КН2

КН1

+

−

H

L

162

Рис. 9.56

Сигнал окончания преобразования можно сформировать комбинацион-

ной логической схемой (рис. 9.57) и использовать его для управления бу-

ферным регистром или иным устройством, воспринимающим код преобра-

зуемого напряжения.

Если преобразуемое напряжение U

зад уменьшилось до уровня Uзад2

(рис. 9.57), то выходное напряжение ЦАП снижается до напряжения

«мертвой зоны» со своего предыдущего уровня, «отслеживая» таким об-

разом изменения входного напряжения АЦП.

При вхождении Uцап в «мертвую зону» (окончание преобразования)

снова будет выполнено условие Н=0, L=0.

Рис. 9.57

Компаратор с двумя выходами может быть выполнен по схеме рис.

9.58. Напряжения U

зад и Uцап подаются одновременно на разноименные

входы компараторов напряжения КН1 и КН2, а смещение Q – на инверти-

рующие входы. Диоды VD1 и VD2 осуществляют развязку между инвер-

ЦАП

U

зад1

U

зад2

U

Сложение

0 Лог.

0 Лог.

1 Лог.

1 Лог.

H

L

2Q

2Q

Вычитание

163

тирующими и неинвертирующими входами КН1 и КН2. За счет смещения

образуется «мертвая зона» шириной 2Q (в КН1 Q прибавляется к U

цап, а в

КН2 Q прибавляется к U

зад).

Рис. 9.58

Во многих случаях входное аналоговое напряжение от одного преобра-

зования к следующему может сильно изменяться. Это особенно верно,

если АЦП используется для последовательного преобразования сигналов

от многих датчиков через мультиплексор. Более того, в некоторых случа-

ях требуется осуществить преобразование со строгой периодичностью за

фиксированное время.

Этим условиям удовлетворяет АЦП поразрядного уравновешивания

(АЦП последовательного приближения), блок-схема которого представ-

лена на рис. 9.59. Согласно методу последовательных приближений, по-

следовательно подбираются значения битов выхода АЦП, все ближе при-

ближающихся к входному аналоговому напряжению по их эквиваленту в

аналоговой форме. Аналоговый эквивалент напряжения формирует ЦАП.

Схема содержит регистр испытуемого числа на JK-триггерах, ЦАП

преобразуемого числа, дешифратор, двоичный счетчик, компаратор КН,

синхрогенератор СГ и логические элементы.

По синхроимпульсу SBROS (начало преобразования) происходит

сброс двоичного счетчика и сброс регистра. Предустановка старшего бита

регистра испытуемого числа в 1 осуществляется по сигналу SET 1. По-

скольку у обнуленного счетчика выходной код X

1

Х

О

имеет значение

00, то у дешифратора активным (единичным) будет выход 0, подключен-

ный на один из входов первого элемента И и установочный вход второго

слева триггера регистра.

Преобразование начинается со старшего бита. Так как в начале преоб-

разования в триггере старшего бита регистра установлена 1 (выход a3), то

на выходе ЦАП будет напряжение, равное весу старшего разряда разряд-

ной сетки АЦП. Это напряжение сравнивается компаратором КН с преоб-

разуемым напряжением U

зад. Если при этом Uцап>Uзад, то на выходе КН

ЦАП

U

зад

U

164

формируется логический 0, а на выходе инвертора логическая 1. В резуль-

тате схемой И на входе 1К триггера старшего бита будет установлен сбра-

сывающий единичный сигнал.

По заднему фронту синхроимпульса от СГ разряд a3 сбросится в 0,

разряд a2 установится в 1, счетчик на выходе будет иметь код 01, а выход

1 дешифратора станет активным.

Рис. 9.59

Если при сравнении старшего бита U

цап<Uзад, то на выходе КН будет

сформирована логическая 1 и будет заблокирован сброс старшего бита,

а АЦП перейдет к уравновешиванию следующего бита и т.д. Процесс

уравновешивания будет окончен, когда будут последовательно опробова-

ны все разряды сетки, начиная со старшего бита.

Функцию переключателя разрядов выполняют совместно счетчик и

дешифратор, причем счетчик последовательно формирует увеличиваю-

щийся на 1 код, в результате чего выходы дешифратора последовательно с

Ц А П

СГ

числ

а

оиспытуемог

Регистр

регистра

логика

Входная

Дешифратор

Счетчик

КН

165

частотой импульсов СГ принимают активное состояние и последовательно

устанавливают разряды регистра в пробное единичное состояние.

После четвертого импульса СГ счетчик имеет выходной код 100 (в

старшем разряде X2 устанавливается единица переноса), что является при-

знаком окончания преобразования. Единица переноса после инвертиро-

вания схемой НЕ блокирует схему И, и процесс преобразования прекра-

щается до прихода очередного импульса «начало преобразования».

На рис. 9.60 приведены диаграммы сигналов некоторых узлов АЦП.

На рис. 9.60 импульс «начало преобразования» обозначен как U

н.

Uн

Uсг

0

1

2

3

t

Рис. 9.60

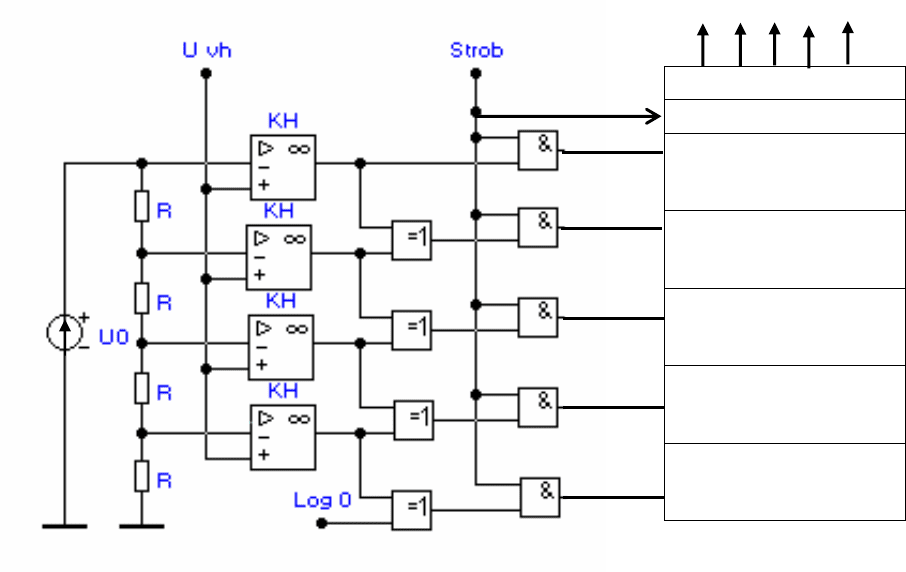

На рис. 9.61 приведена блок-схема АЦП параллельного действия. Ос-

новными элементами схемы являются многозвенный резисторный дели-

166

тель напряжения на резисторах R, компараторы напряжения КН, схемы

«исключающее ИЛИ» и «И», матрица ПЗУ и выходной регистр. В нижней

ячейке матрицы ПЗУ записано двоичное число 00....0, в следующей - чис-

ло, увеличенное на 1 и т.д. В верхней ячейке значение числа равно 11...1.

Количество ячеек памяти определяется разрядностью

n АЦП и равно 2

n

.

Такое же количество требуется и элементов других типов.

Выходной регистр

a4 a3 a2 a1 a0

0 0 1 0 0

ячейка 4 ПЗУ

0 0 0 1 1

ячейка 3 ПЗУ

0 0 0 1 0

ячейка 2 ПЗУ

0 0 0 0 1

ячейка 1 ПЗУ

0 0 0 0 0

ячейка 0 ПЗУ

Рис. 9.61

Эталонное напряжение U0, соответствующее максимальному значе-

нию преобразуемого напряжения U

vh, равномерно делится на резисторах R

делителя напряжения, падение напряжения

∆U0 на каждом резисторе со-

ответствует цене одной дискреты АЦП.

Если U

vh = 0, то на выходах всех компараторов установятся уровни

логического 0, соответственно на входах и выходах всех, кроме нижней

схемы «исключающее ИЛИ», также установятся нулевые уровни напря-

жения. Так как на один из входов нижней схемы «исключающее ИЛИ»

постоянно подается логическая 1, а на втором входе установлен логиче-

ский 0 с выхода КН, то на ее выходе формируется логическая 1. По стро-

бирующему импульсу Strob происходит считывание содержимого нижней

ячейки и запись в выходной регистр.

Если U

vh > 0, то в соответствии со значением Uvh определенное число

нижних компараторов на выходах установит единичные уровни, а ос-

тальная (верхняя) часть компараторов на выходах будет иметь нулевой

уровень. Таким образом, на входах одной из схем «исключающее ИЛИ»,

167

находящейся на границе групп компараторов с различными уровнями вы-

ходных напряжений, будет иметь место комбинация логический 0 и логи-

ческая 1, а на ее выходе установится логическая 1. На выходах остальных

схем «исключающее ИЛИ» установятся логические 0, т.к. на их входах

будут действовать одноименные сигналы. В итоге будет сформирован

сигнал для выборки только одной ячейки П3У и именно той, в которой

записано двоичное число, соответствующее U

vh.

Дешифратор табличного типа на основе матрицы ПЗУ и остальная

часть АЦП могут иметь интегральное исполнение, и поэтому сложность

устройства не является препятствием для практического применения тако-

го АЦП параллельного действия.

9.10 ЗАПОМИНАЮЩИЕ УСТРОЙСТВА С ПРОИЗВОЛЬНЫМ

ДОСТУПОМ

9.10. 1 Оперативные запоминающие устройства

ЗУ с произвольным доступом – это такое 3У, в котором информация,

записанная в ячейках памяти, может быть непосредственно считана.

Время, необходимое для выборки данной ячейки, оказывается примерно

тем же, что и для любой другой ячейки. Идентифицирующий фиксиро-

ванный номер в двоичном коде называется адресом ячейки.

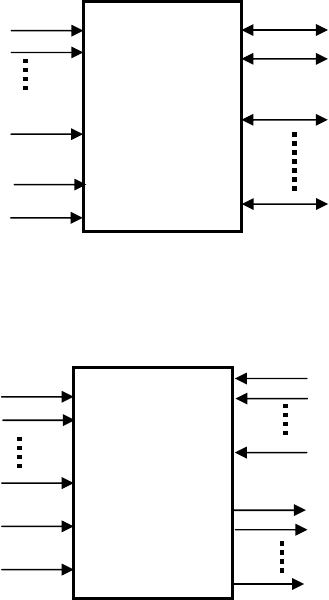

Существует довольно много разновидностей модулей памяти с набо-

ром внешних сигналов, однако большинство модулей можно отнести к од-

ной из двух основных моделей (рис. 9.62).

Разновидности модулей отличаются друг от друга организацией вход-

ных и выходных шин данных. Общим для модулей является управление

режимами работы. Если сигнал «Запись» имеет значение логической «1»,

то разрешена запись информации в модуль памяти, а при нулевом значе-

нии сигнала разрешено чтение информации. Сигнал «Выборка модуля»

разрешает или запрещает работу модуля.

Внутренняя организация 3У с произвольным доступом может харак-

теризоваться одномерной и двумерной адресацией.

Пример ЗУ с одномерной адресацией и с раздельными

линиями вход-

ных и выходных данных для двух четырехразрядных слов приведен на рис.

9.63.

Слово информации хранится в линейке горизонтально расположенных

запоминающих элементов 1bitRAM, причем каждый элемент предназна-

чен для хранения одного бита информации. Каждая из выходных линий

selectwrd дешифратора адреса формирует сигнал выборки слова для опре-

деленной линейки (строки) запоминающих элементов.

Линейка представляет собой ячейку памяти, имеющую свой адрес.

Запись или чтение информации осуществляется словом по сигналу R/W

168

Линии адреса Линии входных

и выходных данных

Запись

Выборка

модуля (ВК)

а)

Линии адреса Линии входных

данных

Запись Линии выходных

Выборка данных

модуля (ВК)

б )

Рис. 9.62

(этот сигнал соответствует сигналу «Запись»). Режим записи или чтения

устанавливается соответствующим уровнем сигнала R/W (Write/Read).

Число ячеек памяти может быть достаточно большим. Разрядность ад-

ресного кода, поступающего на входы дешифратора адреса, определяется

как n=lоgN, где N - емкость ЗУ в словах.

В оперативных запоминающих устройствах (ОЗУ) запоминающий эле-

мент выполнен на основе асинхронного RS-триггера (рис. 9.64).

При значении сигналов «R/W»=1 и «BK»=1 конъюнкторы 1 и 2 от-

крыты для записи бита входных данных по входу «input» в RS-триггер.

При этом конъюнктор 3 закрыт инверсией сигнала «R/W», и триггер за-

крыт для чтения. При сочетании сигналов «BK»=1 и «R/W»=0 открывает-

ся конъюнктор 3 и закрываются конъюнкторы 1 и 2. На линии «out» появ-

ляется (читается) бит выходной информации, записанный ранее в триггер.

Для уменьшения нагрузки на выход триггера предназначен элемент

ИЛИ, через который, кроме того, проходит выходной сигнал «out» от

другого запоминающего элемента столбца ЗУ.

МОДУЛЬ

ПАМЯТИ

[

]

МОДУЛЬ

ПАМЯТИ

[

]

]

169

Недостаток рассмотренной схемы ЗУ произвольного доступа с одно-

мерной адресацией связан с большим количеством выходов адресного

дешифратора при значительной емкости ЗУ.

Рис. 9.63

Для уменьшения количества выходных линий адресных дешифраторов

ЗУ выполняют с двумерной адресацией (рис.9.65). Выходные линии одно-

го дешифратора будут служить для выбора строки матрицы памяти, а дру-

гого – для выбора столбца.

Рис. 9.64

170

В каждом запоминающем элементе ЗУ должна выполняться операция

И над сигналами линий выборки строки и столбца. Эта операция обеспе-

чивает логическую 1 только для одного элемента, находящегося на пересе-

чении выбранных строки и столбца, и логический 0 для остальных элемен-

тов. Остальные управляющие, входные и выходные линии на рис. 9.65 не

показаны.

Аналогичные двумерные матрицы нужны и для всех остальных разря-

дов в словах. Матрицы можно считать лежащими в параллельных плоско-

стях. Оба дешифратора работают сразу на все плоскости, все биты ячейки

адресуются одновременно.

Адреса

строк

n/2

n/2

Адреса столбцов

Рис. 9.65

На рис. 9.66 приведена схема наращивания разрядности и числа ячеек

ЗУ. На схеме предполагается, что каждый из запоминающих элементов

представляет собой отдельную микросхему с разрядной матрицей, коли-

чество запоминающих элементов которой определяет число разрядов адре-

са А1.

ЗЭ ЗЭ ЗЭ

ЗЭ

ЗЭ

ЗЭЗЭЗЭ

ЗЭ

Д

е

ш

и

ф

р

а

т

о

р

с

т

р

о

к

Дешифратор столбцов