Зайцев А.П. Общая электротехника и электроника. Учебное пособие: Часть II

Подождите немного. Документ загружается.

121

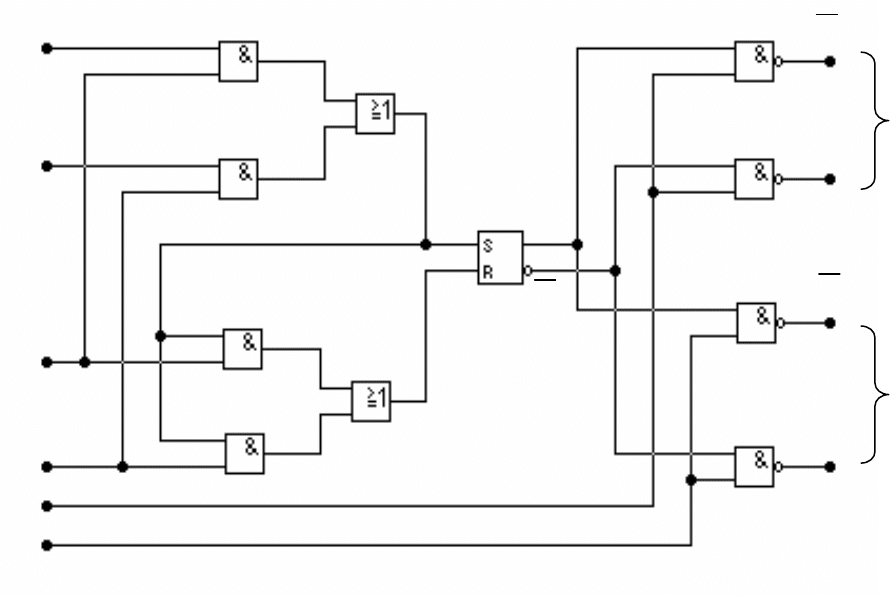

Из логики функционирования схемы следует, что сигналы С1 и С2

должны быть парафазны для исключения одновременного приема с двух

направлений.

Сигналы С

3 и С4 независимы друг от друга и принимают соответст-

вующие значения в зависимости от порядка работы выходов.

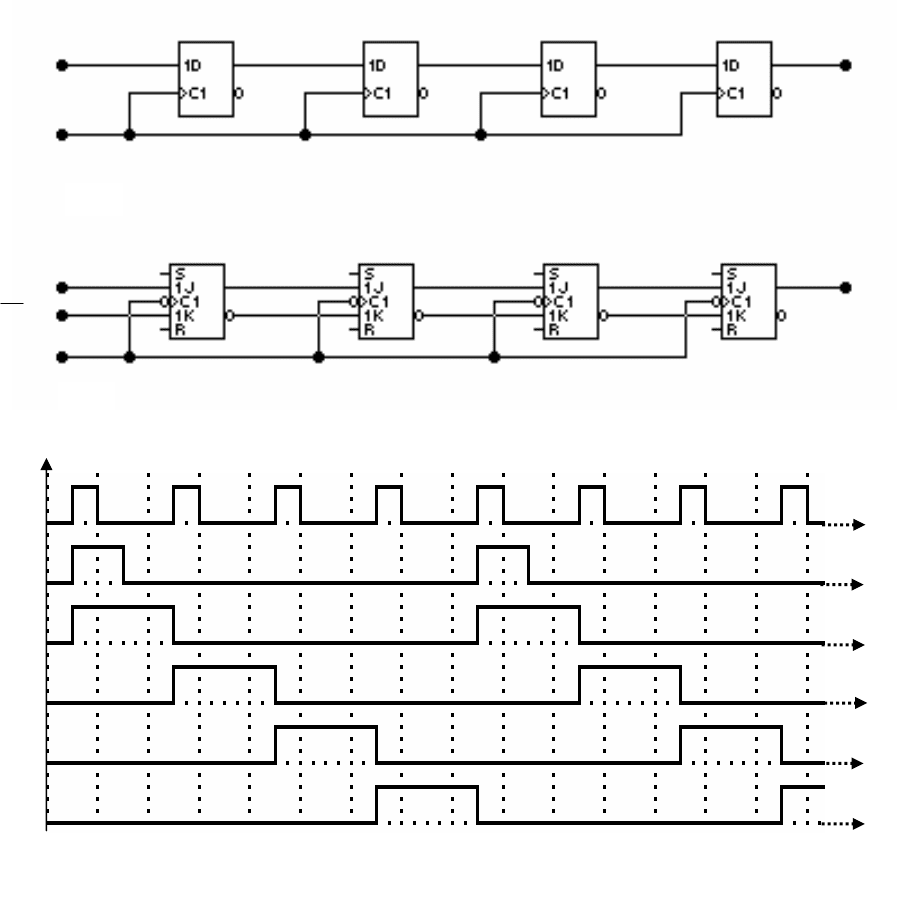

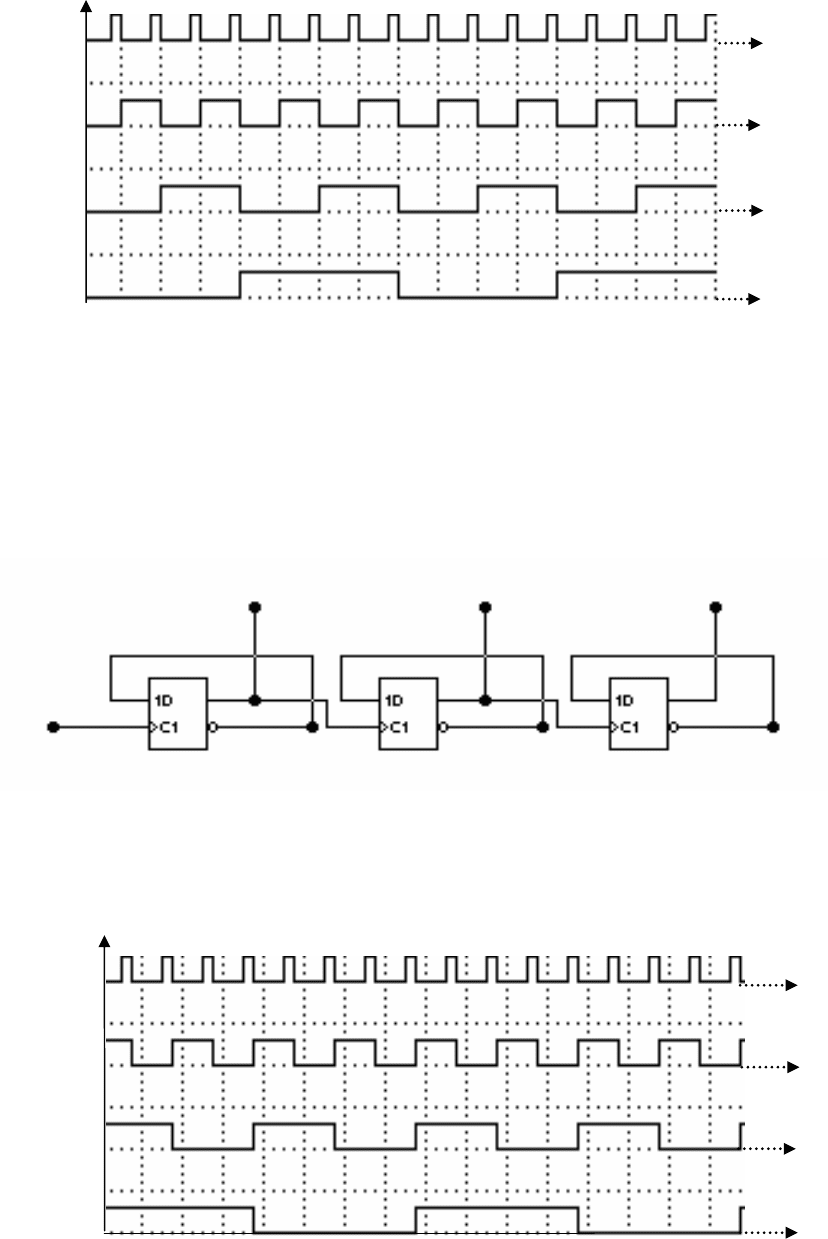

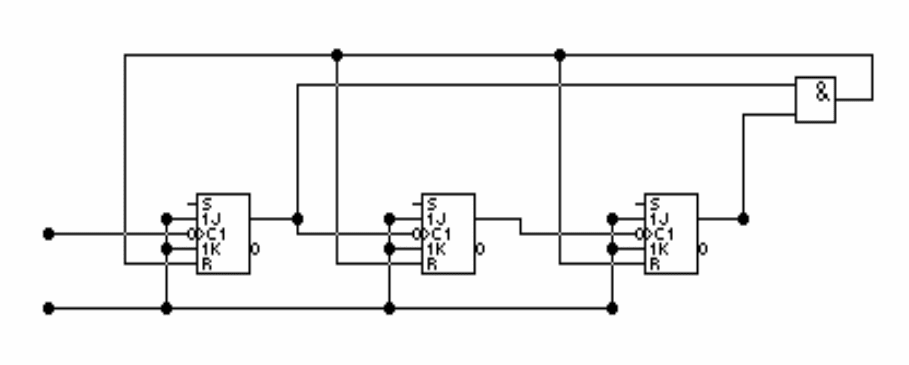

Последовательные (сдвигающие) регистры – это цепочка вза-

имосвязанных разрядных схем. На рис. 9.14 представлены структуры сдви-

гающих вправо регистров на различных типах триггеров.

1

1

2

2

Рис. 9.13

Схема на триггерах типа D экономична по числу связей. Парафазные

связи в схемах на триггерах RS и JК могут обеспечить более высокую по-

мехоустойчивость регистра. Если внешний вход однофазный, то при по-

мощи инвертора образуют парафазный вход.

В сдвигающем регистре нельзя применять простые тактируемые триг-

геры, управляемые уровнем, поскольку пока действует сигнал «сдвиг»,

передача данных из разряда в разряд будет проходить безостановочно. При

использовании двухступенчатых триггеров положительный полутакт сиг-

нала Uс позволяет входным ступеням триггеров принять информацию от

соседних триггеров, но далее процесс не распространяется. При смене по-

ложительного полутакта Uс на нулевой новая информация появится в вы-

ходных ступенях, но далее не пройдет, так как прием информации вход-

ными ступенями заблокирован, и произойдет сдвиг слова на один разряд.

j

a

j

b

Q

Q

Q

Q

Q

Q

1

С

2

С

3

С

4

С

122

На рис. 9.14, в представлены временные диаграммы процессов в трех

разрядах сдвигающего регистра. Единичный входной импульс U

ВХ по пе-

реднему фронту тактового импульса U

с записывается в выходную ступень

первого триггера. Второй тактовый импульс осуществляет запись единич-

ного входного импульса из первой ступени во вторую и т.д. Таким об-

разом, с очередным тактовым импульсом информация продвигается на

один разряд вправо.

1 2 3 4 5 6 7 8

U

c

U

вх

Q

1

Q

2

Q

3

Q

4

t

в

Рис. 9.14

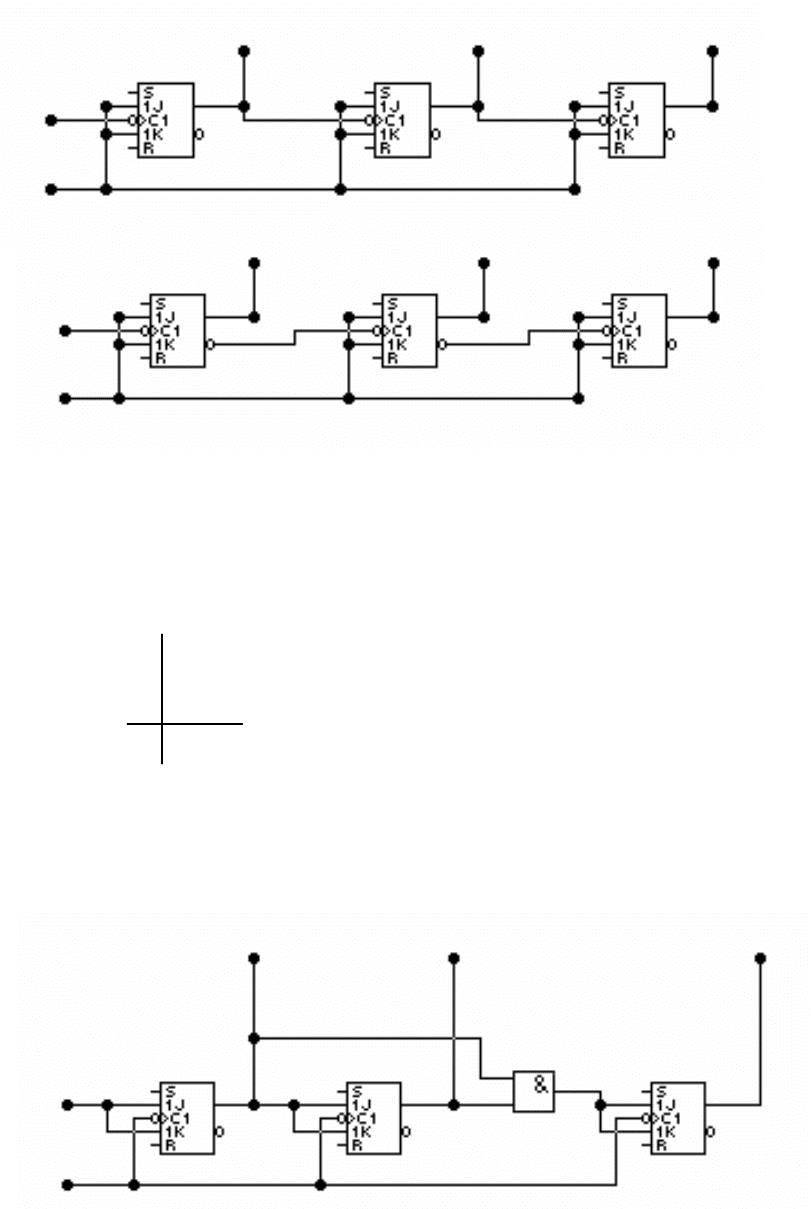

В структурах регистров с реверсивным сдвигом имеются связи тригге-

ров с обоими соседними разрядами (левым и правым). По сигналам «вле-

во» и «вправо» активизируются лишь одни из этих связей и блокируются

другие (рис. 9.15). С триггеров берутся инверсные сигналы, так как венти-

ли И-ИЛИ-НЕ обладают инвертирующими свойствами.

а

б

вх

U

вх

U

c

U

c

U

вх

U

1

Q

1

Q

2

Q

2

Q

3

Q

3

Q

4

Q

4

Q

а)

б)

в)

123

Вход и выход у сдвигающих регистров являются последовательными,

но вместе с этим в схеме могут быть и параллельные входы и выходы. В

этом случае регистры являются последовательно-параллельными и преоб-

разуют последовательный код в параллельный путем приема последова-

тельного кода и затем его параллельной выдачи, либо наоборот.

Последовательный регистр сдвига, с работой которого мы познако-

мились, обладает двумя недостатками: он позволяет вводить только по

одному биту информации на каждом тактовом импульсе и, кроме того,

каждый раз при сдвиге информации в регистре вправо теряется крайний

правый информационный бит.

Вых.2 Вх.2

Влево

Вх.1

Вправо

Сдвиг

Рис. 9.15

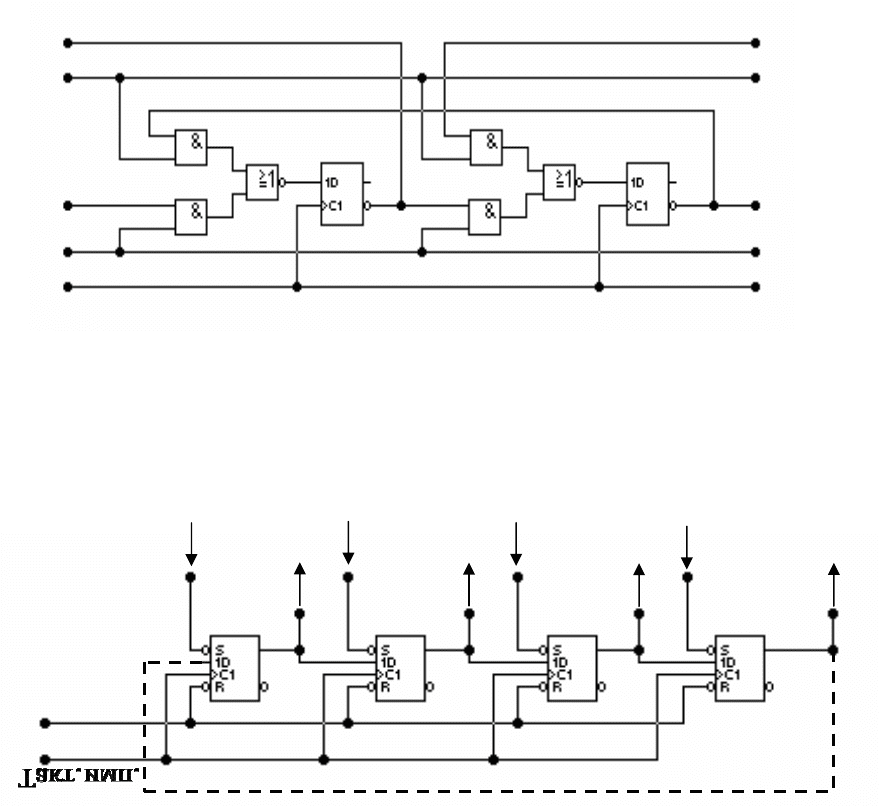

На рис. 9.16 показана схема, которая позволяет осуществлять одно-

временную параллельную загрузку 4 бит информации.

A B C D

Рис. 9.16

Входы A, В, С, D в этом регистре являются информационными вхо-

дами. Эту схему можно снабдить еще одной полезной характеристикой –

возможностью кольцевого перемещения информации, когда данные с

выхода устройства возвращаются на его вход и не теряются. Это может

быть достигнуто введением обратной связи с выхода последнего тригге-

ра на вход D первого триггера (пунктирная линия). Благодаря этой цепи

a

Q

b

Q

c

Q

d

Q

Сброс

Вых.1

124

обратной связи введенная в регистр информация будет циркулировать по

регистру сдвига. Сигналом очистки регистра (установки его выходов в со-

стояние 0000) является уровень логического нуля на входах R всех триг-

геров. Входы параллельной загрузки данных A, В, С, D связаны со вхо-

дами S предварительной установки триггеров. Если на один из входов по-

дать логический нуль, то на соответствующем выходе будет установлена

логическая единица.

Подача тактовых импульсов на входы С всех триггеров приводит к

сдвигу информации в регистре вправо (кольцевое перемещение информа-

ции).

Для поочередной работы на общую для нескольких регистров магист-

раль в режиме разделения времени их выходы часто содержат специаль-

ные элементы с тремя состояниями: «1», «0» и «отключено» (отключение

от нагрузки). В состоянии «отключено» выход элемента не потребляет и

не отдает тока в нагрузку. Если в каждый момент времени лишь один из

подключенных к магистральной шине регистров активен, а все остальные

отключены, то обеспечивается нормальный режим разделения времени.

9.5 ДВОИЧНЫЕ И ДВОИЧНО-КОДИРОВАННЫЕ СЧЕТЧИКИ

Специфической для счетчиков является микрооперация инкремента-

ции, т.е. изменения содержимого на единицу. Кроме того, ими выполня-

ются и такие микрооперации как установка в исходное состояние, хране-

ние, выдача слов.

Счетчики характеризуются, прежде всего, модулем счета (емкостью)

М. После каждых М сигналов счетчик возвращается к началу цикла счета.

По значению модуля счета различают двоичные (М=2

n

), двоично-

кодированные (с произвольным модулем, но кодированием состояний

двоичными кодами), счетчики с одинарным кодированием и др.

По направлению счета делятся на суммирующие (прямого счета), вы-

читающие (обратного счета) и реверсивные.

По способу организации межразрядных связей различают счетчики с

последовательным, параллельным и комбинированным переносами.

Основными режимами работы счетчиков являются регистрация числа

поступивших сигналов и деление частоты.

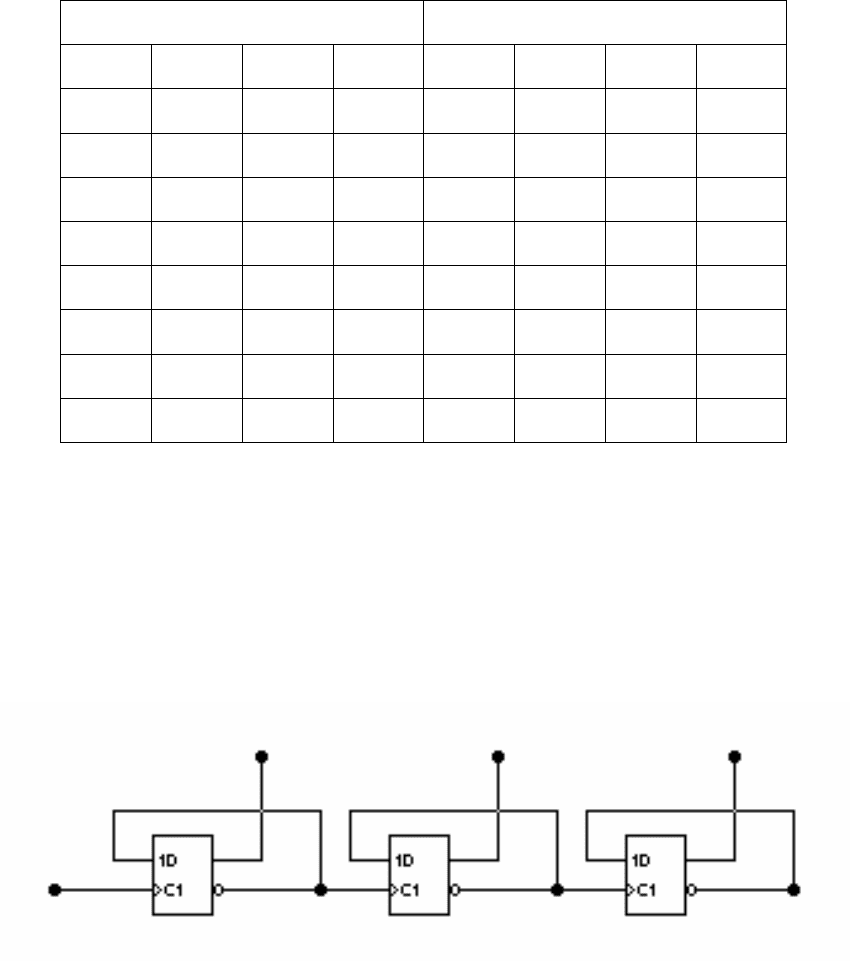

Структуры двоичных счетчиков можно получить, рассмотрев особен-

ности последовательности двоичных чисел. Рассмотрим последователь-

ность двоичных чисел от 0 до 7 в возрастающем порядке (табл. 9.4). Из

таблицы видно, что триггер младшего разряда а

0 переключается от каждого

входного сигнала ( 0 и 1 чередуется). В столбце следующего разряда 0 и 1

чередуются парами, затем четверками и т.д.

Частота переключений каждого последующего триггера уменьшается

вдвое по сравнению с частотой переключения предыдущего. Следователь-

125

но, счетчик можно построить как цепочку последовательно включенных

счетных триггеров, каждый из которых обладает свойством деления часто-

ты на 2. Это утверждение справедливо как для суммирующего, так и для

вычитающего счетчиков.

Таблица 9.4

Прямой счет Обратный счет

а

2

а

1

а

0

Nдес а

2

а

1

а

0

Nдес

0 0 0 0 1 1 1 7

0 0 1 1 1 1 0 6

0 1 0 2 1 0 1 5

0 1 1 3 1 0 0 4

1 0 0 4 0 1 1 3

1 0 1 5 0 1 0 2

1 1 0 6 0 0 1 1

1 1 1 7 0 0 0 0

Для установления вида связей между триггерами для той или иной

схемы снова обратимся к таблице. Из таблицы прямого счета видно, что

соседний старший разряд изменяет состояние при переходе соседнего

младшего разряда из 1 в 0, значит, суммирующий счетчик может пред-

ставлять собой цепочку из триггеров с инверсным динамическим управ-

лением (рис.9.17).

Рис. 9.17

Для построения двоичных счетчиков пригодны двухступенчатые и ди-

намические D- и JK-триггеры, на основе которых выполняются счетные

Т-триггеры.

Если перенести точку съема сигналов с прямых выходов триггеров на

инверсные, то получим эквивалент на счетных триггерах с прямым дина-

мическим управлением.

0

a

1

a

2

a

вх

U

126

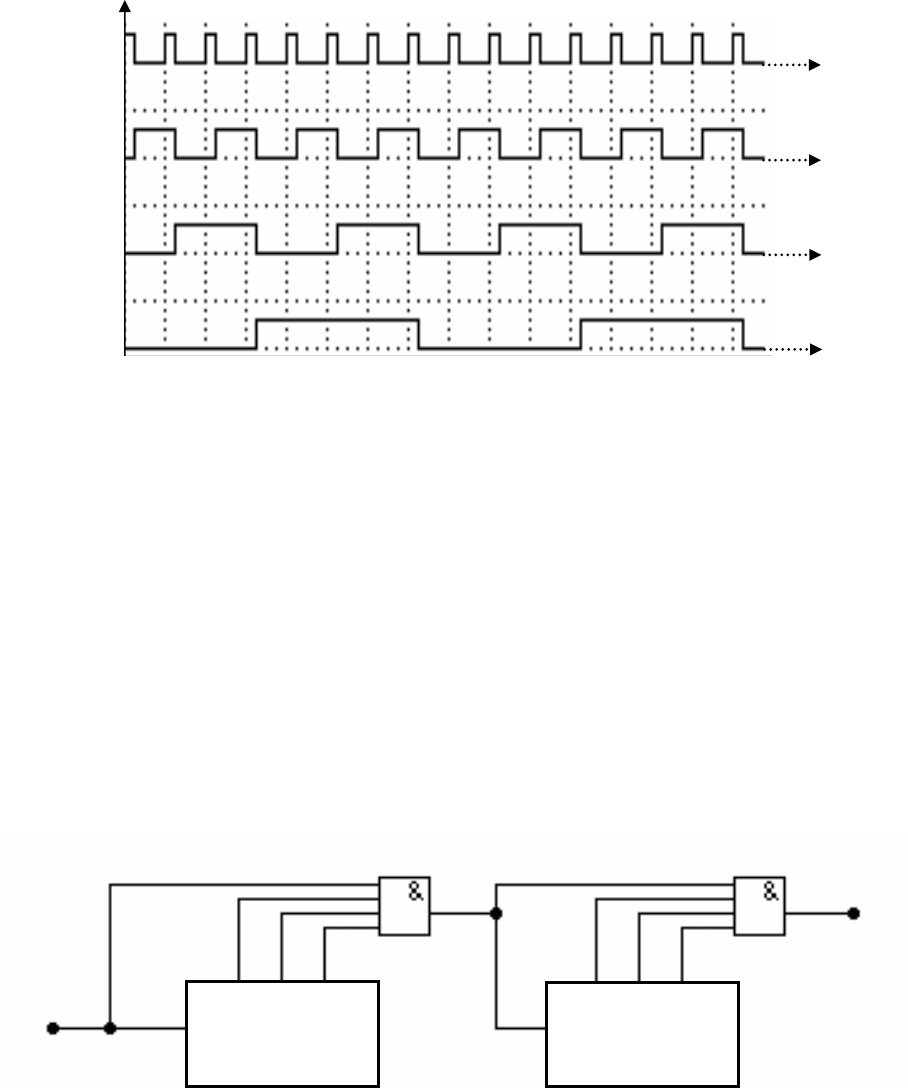

На рис. 9.18 показаны диаграммы изменения во времени входного и

выходных сигналов счетчика.

Рис. 9.18

Согласно таблице обратного счета, последующие разряды изменяют

состояние при переходе предыдущего разряда с 0 на 1. Поэтому схема

вычитающего счетчика представляет собой цепочку из счетных триггеров

с прямым динамическим управлением (рис. 9.19).

Другой вариант вычитающего счетчика получают, используя инверс-

ные выходы и триггеры с инверсным динамическим управлением.

Рис. 9.19

На рис. 9.20 приведены диаграммы вычитающего трехразрядного

счетчика. Предполагается, что счет осуществляется с момента времени, ко-

гда вычитающий счетчик имеет единичное состояние по всем разрядам.

Рис. 9.20

0

a

1

a

2

a

вх

U

t

t

t

t

вх

U

0

a

1

a

2

a

t

t

t

t

вх

U

0

a

1

a

2

a

127

Двоичные счетчики прямого и обратного счета могут быть выполнены

также на JK-триггерах (рис. 9.21,

а, б), если их перевести в режим счетных

триггеров подачей сигналов уровня логической единицы одновременно на

входы J и K.

Рис. 9.21

Рассмотренные ранее счетчики называются последовательными. Па-

раллельные счетчики (синхронные, с параллельным переносом) имеют

максимальное быстродействие, поскольку в них все разряды переключа-

ются одновременно. Рассмотрим пример:

1 1 0 1 1 1

+

1

1 1 1 0 0 0

Наблюдение за процессом прибавления 1 к двоичному числу показыва-

ет, что результат от исходного числа отличается только в младших разря-

дах. Изменение состоит в инвертировании состояний младших разрядов.

Параллельный счетчик содержит разрядные триггеры с конъюнктора-

ми, анализирующими состояние предыдущих разрядов (рис. 9.22).

Рис. 9.22

вх

U

вх

U

0

a

0

a

1

a

1

a

2

a

2

a

1 Лог.

1 Лог.

вх

U

0

a

1

a

2

a

1 Лог.

а)

б)

128

На рис. 9.23 показаны диаграммы сигналов параллельного счетчика.

Рис. 9.23

При поступлении входного сигнала переключаются только те триггеры,

для которых все предыдущие были в единичном состоянии, что и требует-

ся согласно примеру.

Трудности реализации многоразрядных параллельных счетчиков свя-

заны с ростом числа входов у конъюнкторов по мере увеличения разрядно-

сти счетчика и ростом нагрузки на выходы триггеров.

В связи с этими ограничениями широкое распространение получили

счетчики с групповой структурой (с комбинированным переносом), в ко-

торых счетчик разбивается на группы, внутри которых реализуется ка-

кой-либо вид переноса, а между группами осуществляется межгрупповой

перенос (рис. 9.24). Разрядность групп может быть снижена до пределов, в

которых можно организовать параллельный перенос.

Рис. 9.24

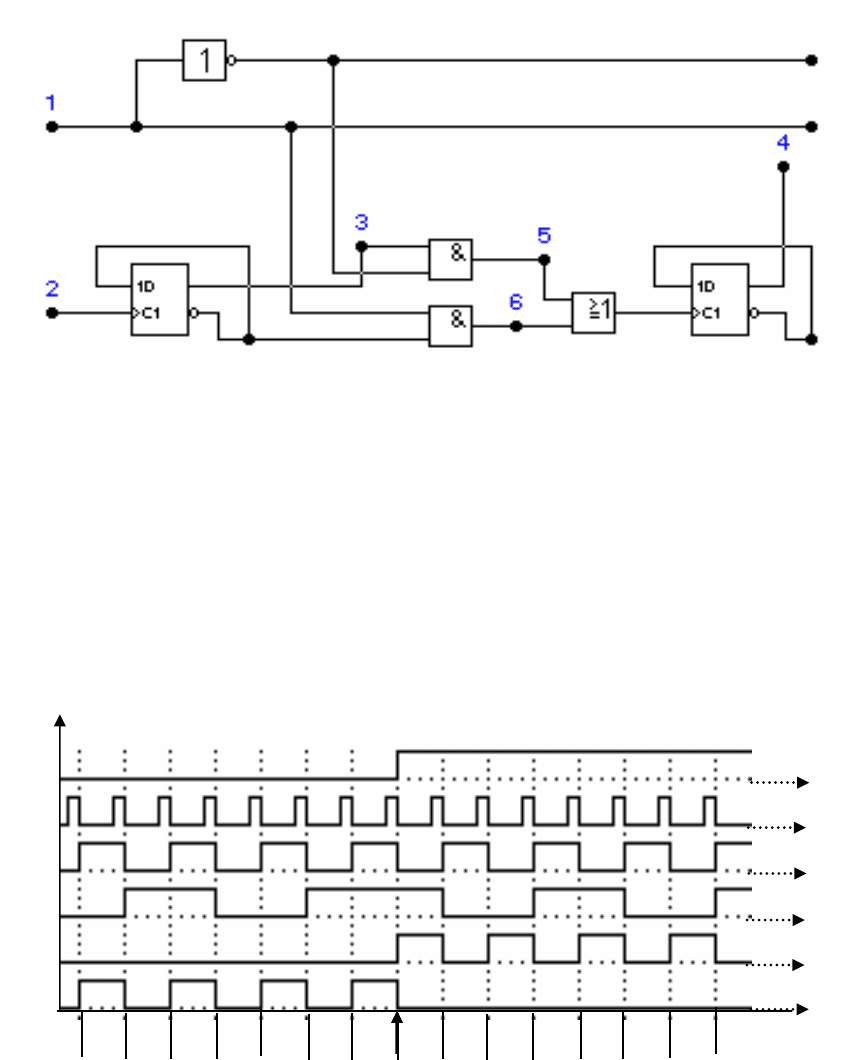

Реверсивные счетчики наиболее часто реализуются переключением

межразрядных связей. Счетчики прямого и обратного счета различаются

лишь точкой съема сигнала, подаваемого с предыдущего разряда на после-

дующий.

вх

U

0

a

1

a

2

a

t

t

t

t

Синхронный

счетчик

Синхронный

счетчик

вх

U

рр

2

a

1

a

0

a

3

a

4

a

5

a

129

Если управляющий сигнал перестраивает межразрядные связи, перено-

ся точку съема сигнала с одного выхода триггера на другой, то реализуется

схема реверсивного счетчика (рис. 9.25).

Рис. 9.25

На рис. 9.26 показаны диаграммы сигналов реверсивного счетчика в

различных точках схемы.

На диаграммах момент переключения с прямого счета на обратный

обозначен через t

п. В момент переключения содержимое счетчика состав-

ляло в десятичном эквиваленте 3 (нижняя строка). Как видно из диаграмм,

до этого момента счетчик работал в режиме прямого счета, а после – в ре-

жиме обратного счета.

1

2

3

4

5

6

0 1 2 3 0 1 2 3 2 1 0 3 2 1 0

tп

Рис. 9.26

В некоторых случаях требуется, чтобы коэффициент пересчета был ра-

вен не 2

n

, а другому числу. Построение таких схем возможно при исполь-

зовании обратной связи. Обратная связь посылает дополнительные им-

t

t

t

t

t

t

130

пульсы с какого-либо старшего разряда счетчика на младший, т.е. вводит

иную закономерность в подсчете импульсов (рис. 9.27).

Рис. 9.27

Отношение числа импульсов NC на входе счетчика к числу импульсов

N

Q на выходе старшего разряда за время цикла работы счетчика называют

коэффициентом пересчета K

СЧ. Если на вход счетчика подавать периодиче-

скую последовательность импульсов определенной частоты, то на выходе

счетчика частота импульсов старшего разряда будет в K

СЧ раз меньше. По-

этому счетчики называют делителями частоты, а K

СЧ – коэффициентом де-

ления.

Для построения счетчика с K

СЧ=5 необходимо, чтобы после пятого со-

стояния счетчика во время счета импульсов (0, 1, 2, 3, 4) он переходил не к

числу 5, а к числу 0. В двоичном коде это означает, что от числа 100 необ-

ходимо перейти к числу 000, а не к 101. Изменение естественного порядка

счета обеспечивается введением дополнительных связей между триггера-

ми через двухвходовый элемент И (рис. 9.27).

При счете от 0 до 4 суммирующий счетчик работает в обычном поряд-

ке. Счет происходит по отрицательному фронту импульсов U

вх на счетном

входе. Как только счетчик попадает в нерабочее состояние (в нашем слу-

чае 101), на выходах первого и третьего триггеров устанавливаются сигна-

лы единичного уровня. Эти сигналы поступают на входы схемы И. На вы-

ходе схемы И формируется короткий сигнал единичного уровня, который

по сбрасывающим входам R-триггеров установит счетчик в нулевое со-

стояние. Новый цикл счета начнется с приходом очередного импульса на

счетный вход.

Процессы, протекающие в счетчике, поясняют диаграммы рис. 9.28. Из

диаграмм видно, что процесс сброса счетчика занимает конечное время,

поэтому непосредственно перед сбросом счетчика на выходе первого триг-

гера появляются короткие импульсы. Данный выход нельзя использовать

в качестве источника тактовых импульсов для других устройств.

вх

U

0

a

1

a

2

a

R

U

1 Лог.