Ghodssi R., Lin P., MEMS Materials and Processes Handbook

Подождите немного. Документ загружается.

594 D.W. Burns

Table 8.25 Ion-implanted silicon etch stops and processes

Material

Etch rate

reduction Etchant Remarks and references

1 Silicon (Si),

(100),

implanted

boron (B)

EDP, KOH, N

2

H

4

,

NH

4

OH, TMAH

Implanted boron etch stop; see Table 8.23 [475, 477]

2 Silicon (Si),

(100),

implanted

oxygen (O)

EDP, KOH(33 wt%),

KOH-IPA

Implanted oxygen etch stop (SiO

2

); implanted O

+

with heated

substrate (550

◦

C plus self-heating); 1.1 × 10

18

cm

−2

dosage at

100 keV for 60-min etch stop in EDP; 1.2 × 10

18

cm

−2

dosage for

60-min etch stop in KOH-IPA; no postimplant anneal [478]

3 Silicon (Si),

(100),

implanted

nitrogen (N)

EDP, KOH(33 wt%),

KOH-IPA

Implanted nitrogen etch stop (Si

3

N

4

); implanted N

+

with heated

substrate (550

◦

C plus self-heating); 1.0 × 10

18

cm

−2

dosage at

200 keV for 60-min etch stop in EDP or KOH-IPA;

1.1 × 10

18

cm

−2

dosage for 60-min etch stop in KOH etchant (33

wt%); no postimplant anneal; high-temperature anneal needed for

additional epi depositions; etch-rate reductions seen at

5.0 ×10

16

cm

−2

N at 120 keV with or without annealing [478, 479]

4 Silicon (Si),

(100)

3.5E20 cm

–3

(C)

5.0E20 cm

–3

(C)

1.5E21 cm

–3

(C)

4.0E21 cm

–3

(C)

0.02

0.01

0.001

0.0002

Ethylenediamine:

pyrocatechol:

pyrazine:H

2

O

1000 mL:160 g:

6 g:133 mL

85

◦

C; EDP etchant, type S; implanted carbon etch stop (SiC);

implanted C

12

with nonheated substrate; 35 keV; 850

◦

C

postimplant anneal [480]

5 Silicon (Si),

(100)

3.0E20 cm

–3

(C)

2.5E21 cm

–3

(C)

4.5E21 cm

–3

(C)

8.0E21 cm

–3

(C)

2.0E22 cm

–3

(C)

0.5

0.1

0.01

0.001

0.0001

KOH:H

2

O

800 g:1000 mL

85

◦

C; KOH etchant (45 wt%); implanted carbon etch stop (SiC);

implanted C

12

with nonheated substrate; 35 keV; 850

◦

C

postimplant anneal [480]

8 MEMS Wet-Etch Processes and Procedures 595

during the elevated temperatures associated with epi growth and that a satisfactory

seed layer for the epi deposition exists at the implanted surface.

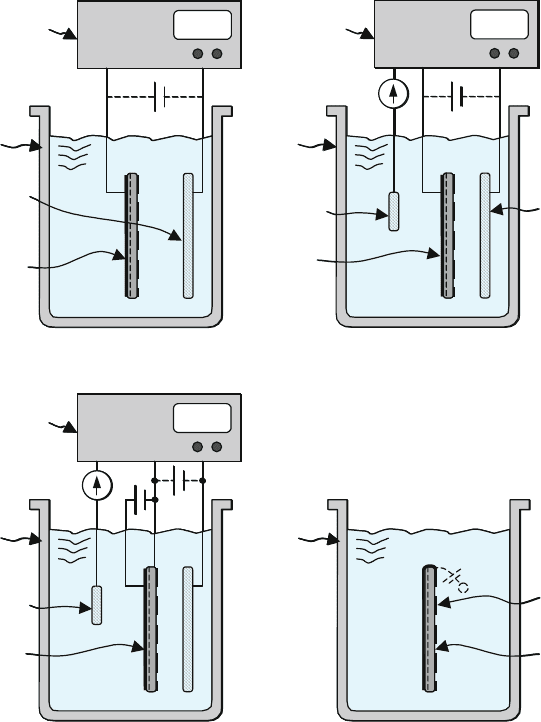

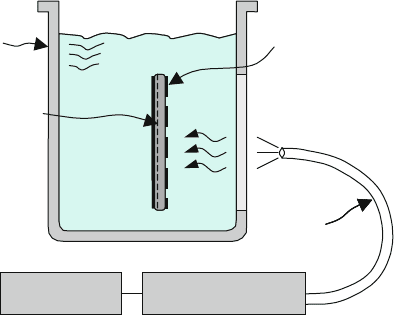

8.6.5 Electrochemical Etching and Electrochemical Etch Stops

Although applicable to nearly any metal or semiconductor material, electrochemical

etching techniques generally require external voltage supplies, monitors, reference

electrodes, and one or more electrical connections to each wafer, which diminish

their utility in favor of simple immersion in selective wet chemical etchants or use of

dry-etching systems. However, in situations where a well-defined etch stop is needed

between n-doped and p-doped material, the additional efforts may be worthwhile.

An example is bulk-micromachined pressure sensors that use a low-doped n-type

diaphragm with p-type piezoresistors.

Electrochemical etch stops can provide suitable stopping capability for wafers

with an internal p–n junction, such as a lightly doped epitaxially deposited n-type epi

layer on top of a p-type substrate. The doping requirements for the p

–

and n

–

sides

are much reduced from heavy p

++

etch stops and allows for piezoresistors and active

devices. Accommodations must be made to provide good electrical contact to the

internal junction, while protecting the connections from inadvertent exposure to the

etchant. When etching at an elevated temperature, reverse leakage currents increase

and can lessen the voltage drop across the diode. High current levels present during

portions of the etch may cause variations in voltage across the wafer and prevent

the etch from stopping near the junction, requiring metal backing plates, metallized

pathways, or regions on the wafer with very low sheet resistance to circumvent.

Two-, three-, four-, and zero-electrode configurations with intrinsic galvanic cou-

ples are possible for silicon etching. Two-electrode configurations require a voltage

be applied across the n-epi and a reference electrode placed in the etchant as seen

in Fig. 8.13a, although this approach is intolerant of leaky junctions and may fail

to etch or fail to stop the etch where desired. The three-electrode configuration

uses a reference electrode such as a platinum sheet, mesh, or wire, in addition to

connections to the n-epi and counterelectrode as seen in Fig. 8.13b. By setting a

potentiostat so that the current through the reference electrode is zero, the interface

potential between the reference electrode and the etchant is stable and less subject

to variations in leakage currents or s horting in the sample, resulting in a more con-

sistent etch stop. The four-electrode configuration requires an additional connection

to the p-type substrate as seen in Fig. 8.13c and is more tolerant of substrate leak-

age, although it requires the most connections and external monitoring. As the etch

nears completion, the current changes dramatically, bubble formation at the silicon

surface or near the counter electrode stops, a smooth surface becomes visible, and

the wafer can be withdrawn and rinsed. A zero-terminal configuration is illustrated

in Fig. 8.13d. This configuration self-generates the required galvanic potentials by

incorporating, for example, thin-film platinum on the front and/or back of a wafer

with sufficient area to stop the etch as an internal p–n junction is reached. Internal

596 D.W. Burns

Etch

Bath

Etchant

Counter

Electrode

(Cathode)

Wafer

Electrode

(Anode)

d) Zero-Terminal Configuration

Etch

Bath

Etchant

Counter

Electrode

Wafer

Electrode

Potentiostat

a) Two-Terminal Configuration

Etch

Bath

Etchant

Reference

Electrode

Wafer

Electrode

Potentiostat

I = 0

c) Four-Terminal Configuration

Etch

Bath

Etchant

Reference

Electrode

Counter

Electrode

Wafer

Electrode

Potentiostat

b) Three-Terminal Configuration

I = 0

Etch

Bath

Etchant

Counter

Electrode

(Cathode)

Wafer

Electrode

(Anode)

d) Zero-Terminal Configuration

Etch

Bath

Etchant

Counter

Electrode

(Cathode)

Wafer

Electrode

(Anode)

d) Zero-Terminal Configuration

Etch

Bath

Etchant

Counter

Electrode

Wafer

Electrode

Potentiostat

a) Two-Terminal Configuration

Etch

Bath

Etchant

Counter

Electrode

Wafer

Electrode

Potentiostat

a) Two-Terminal Configuration

Etch

Bath

Etchant

Reference

Electrode

Wafer

Electrode

Potentiostat

I = 0

c) Four-Terminal Configuration

Etch

Bath

Etchant

Reference

Electrode

Wafer

Electrode

Potentiostat

I = 0

c) Four-Terminal Configuration

Etch

Bath

Etchant

Reference

Electrode

Counter

Electrode

Wafer

Electrode

Potentiostat

b) Three-Terminal Configuration

I = 0

Fig. 8.13 Electrochemical etch stops require a predefined voltage across an internal p–n junc-

tion in a substrate. As a silicon wafer is etched and exposes a biased junction, the exposed n-type

material is anodized and the etch rate slows appreciably. In a two-electrode configuration (a), one

electrical connection is made to the wafer (anode or working electrode) and another to a counter-

electrode (cathode) in the etchant, and connected to an external voltage supply and current monitor.

A three-electrode configuration (b) adds a reference electrode near the working electrode, and the

counter and reference electrodes are connected to a potentiostat to monitor the process. Voltage

adjustments are made so that no current flows through the reference electrode. A four-electrode

configuration (c) has a second connection to the wafer where it can set the potential on the sub-

strate being etched in addition to the stop layer. A zero-terminal configuration (d) has a sizable

platinum film on the wafer that serves as a galvanic cell to self-bias and passivate the n-type layer

when it becomes exposed. Not shown are provisions for ohmic contact and protection for select

portions of the wafer

8 MEMS Wet-Etch Processes and Procedures 597

ohmic connections and fixtures or passivation layers to protect portions of the wafer

during etching are needed.

Judicious selection of applied voltages, current density, and etchant concentra-

tion can have a major impact on the electrochemically etched result, such as the

production of an electropolished surface or porous silicon. As in anisotropic etching

of silicon substrates with chemical etchants, the structures may become increasingly

fragile as the silicon is removed. The etchants are generally anisotropic although the

techniques work with certain isotropic etchants. The electrochemical etch stop gen-

erally applies to p-type substrates with an n-epi layer on top, however, a technique

referred to as pulsed-potential anodization (PPA) allows the etching of n-substrates

while stopping on a p-type layer [481]. Etch rates and etch stop ratios for various

etchants and configurations are listed in Tables 8.26 and 8.27. The interested reader

may consult some of the many excellent papers and books written on the subject [1,

2, 4, 78, 454].

Table 8.26 Electrochemical silicon etchants and etch processes

Material

Etch rate

(Å/s) Etchant Remarks and references

1 Silicon (Si),

(100) n

–

substrate

4.6 KOH:H

2

O

110 g:1000 mL

21

◦

C; KOH etchant (10 wt%) (2 M); 2-terminal

configuration; substrate etch rate before

application of anodization potential: ∼4.6 Å/s;

substrate etch rate with anodization potential:

∼0.009 Å/s (500:1); substrate set slightly

higher than t he passivation potential (–0.7 to

–1.1 V with respect to (wrt) a standard

calomel electrode(SCE)) where anodization

current is minimum; etch ratio degrades to

100:1 at +5 V; etch rate degrades further to

30:1 with illumination [447, 482]

2 Silicon (Si),

(100) p

–

substrate

4.6 KOH:H

2

O

110 g:1000 mL

21

◦

C; KOH etchant (10 wt%) (2 M); 2-terminal

configuration; substrate etch rate before

application of anodization potential: ∼4.6 Å/s;

substrate etch rate with anodization potential:

∼0.019 Å/s (250:1); substrate set slightly

higher than t he passivation potential (–0.7 to

–0.9 V wrt SCE) where anodization current is

minimum; etch ratio degrades to 9:1 at +5 V;

illumination has little effect on etch rate ratio

[447, 482]

8.6.6 Photoassisted Silicon Etching and Etch Stops

Photoassisted etching, also referred to as photoelectrochemical etching, allows

the selective etching and nonetching of silicon, and depends upon doping, light

intensity, and p–n regions within the silicon. The phenomenon is often observed

598 D.W. Burns

Table 8.27 Electrochemical etch stops and processes

Material

Etch rate

ratio Etchant Remarks and references

1 Silicon (Si), (100) p

–

substrate (stops on

n-diffusion)

3000:1 Ethylenediamine:

pyrocatechol:H

2

O

75mL:12g:24mL

105–115

◦

C; EDP etchant; 2-terminal configuration; Pt counterelectrode; +0.6 V

applied to n-layer; etch rate of 210–290 Å/s prior to stopping on n-type layer; etch

rate of passivated layer <0.1 Å/s after stopping [483]

2 Silicon (Si), (100) or

(111) n

+

substrate

(stops on n

–

epi)

HF(49%):H

2

O

1:9

Room temperature; DHF etchant (9:1); 2-terminal configuration; etches n

+

(111) at

550 Å/s; Pt counterelectrode; +6.0 V applied to

n

+

> 4 × 10

18

cm

−3

;n

−

< 2 × 10

16

cm

−3

; avoid illumination [484–486]

3 Silicon (Si), (100) p

–

or

p

+

substrate (stops on

n

–

implant)

HF(49%):H

2

O

1:9

Room temperature; DHF etchant (9:1); 2-terminal configuration; etches p

–

at

250 Å/s; +1.5 V applied ohmically to p

–

substrate wrt Pt counterelectrode;

n

−

<∼ 1 × 10

16

cm

−3

[487]

4 Silicon (Si), (100) p

+

substrate (stops on n

–

epi)

HF(49%):

H

2

SO

4

(96%):H

2

O

1:1:5

25–66

◦

C; HF-sulfuric e tchant; 2-terminal configuration; +0.5 V applied t o n-epi wrt

Pt counterelectrode; remove any brownish build-up with HF:HNO

3

(3:97) [488]

5 Silicon (Si), (100) p

–

substrate (stops on n

–

diffusion)

KOH:H

2

O

250 g:1000 mL

75

◦

C; KOH etchant (20 wt%); 2-terminal configuration; doping-selective etching

(DSE); 1.9 V applied to n-type region wrt Pt counterelectrode in solution (between

passivation potentials of n-type and p-type material); etches n-type material

selectively; topside or bottom side etching; technique may apply to n

+

onn[489]

6 Silicon (Si), (100) p

–

substrate (stops on n

–

epi)

90:1 KOH:H

2

O

665 g:1000 mL

60

◦

C; KOH etchant (40 wt%); 3-terminal configuration; n-type diaphragms on

p-type substrate; substrate etch rate before stop ∼55 Å/s; diaphragm e tch rate

after stop ∼0.6 Å/s; potentiostat connected to n-epi and set to –0.6 V or higher

(more positive than the oxide formation potential for n-type Si) wrt SCE;

p-substrate ideally floats to open circuit potential (OCP); SCE voltage set for 0

current through the SCE by adjusting the Pt counterelectrode voltage; current

through counter electrode is ∼0 mA while etching (for low-leakage diodes);

current increases when etch stop occurs and diminishes after anodic passivation;

sensitive to diode and parasitic leakages; avoid illumination [490, 491]

8 MEMS Wet-Etch Processes and Procedures 599

Table 8.27 (continued)

Material

Etch rate

ratio Etchant Remarks and references

7 Silicon (Si), (100) p

–

substrate (stops on n

–

diffusion or p

++

or

both)

KOH:H

2

O

1000 g:1000 mL

88

◦

C; KOH etchant (50 wt%); 3-terminal configuration (no reference electrode);

capacitive electrochemical etch stop (CECES); etches p-substrate 280 Å/s; +4.0 V

for 3 ms then 0.0 V for 0.3 ms applied to n-region via 200 k on-chip resistors

wrt p

++

substrate connections; Pt counterelectrode in solution also connected to

resistors; timing parameters based on resistor parameters, etched area, and

nonetched areas [492]

8 Silicon (Si), (100) n

–

substrate (stops on p

–

epi)

KOH:H

2

O

250 g:1000 mL

60

◦

C; KOH etchant (20 wt%); 3-terminal configuration; pulsed-potential

anodization (PPA); etches n-type regions selectively over p-type regions; apply

+2 V for 1 s to p-type layer, then apply 0 V for ∼30 s and repeat; modest

reduction in etch rate from rate at open circuit potential; avoid illumination [481]

9 Silicon (Si), (100) p

–

substrate (stops on

inverted p

–

substrate)

KOH:H

2

O

500 g:1000 mL

70

◦

C; KOH etchant (30 wt%); 3-terminal configuration;

metal-insulator-semiconductor (MIS) etch stop; homogenous p-type substrate

with 1000 Å gate oxide; +1.2 V applied to substrate contacts wrt Pt

counterelectrode in solution; +5 V gate voltage results in ∼1 µm-thick features

[493]

10 Silicon (Si), (100) p

–

substrate (stops on n

–

epi)

90:1 KOH:H

2

O

665 g:1000 mL

60

◦

C; KOH etchant (40 wt%); 4-terminal configuration; n-type diaphragms on

p-type substrate; substrate etch rate before stop ∼55 Å/s; diaphragm e tch rate

after stop ∼0.6 Å/s; potentiostat connected to p-substrate and set to –1.5 V (near

open-circuit potential) wrt standard calomel electrode (SCE); n-epi set to +1.5 V

wrt p-substrate; SCE voltage set for 0 current through the SCE by adjusting the Pt

counterelectrode voltage; current through counter electrode is ∼0mAwhile

etching (for low-leakage diodes); current increases when etch stop occurs and

diminishes after anodic passivation; less sensitive to diode leakages than

3-terminal configuration [490, 494]

11 Silicon (Si), (100) p

–

substrate (stops on n

–

epi)

>380:1 N

2

H

4

:H

2

O

1:1

90

◦

C; 50:50 hydrazine etchant; 2-terminal configuration; etches p-substrate at

530 Å/s; etches n-type layer after anodic passivation at <1.4 Å/s; Pt

counterelectrode; n-type layer biased a t +5.0 V wrt counterelectrode; 3000 Å

oxide mask over Al pads; bubbling stops when etch is completed [495, 496]

600 D.W. Burns

Table 8.27 (continued)

Material

Etch rate

ratio Etchant Remarks and references

12 Silicon (Si), (100) p

–

substrate (stops on

n-epi)

TMAH(25 wt% in

H

2

O)

80

◦

C; TMAH etchant (25 wt%); 0-terminal configuration; intrinsic galvanic cell

(IGC) etch stop; Au (2000 Å) on Cr (600 Å) with sufficient area connected to

n-epi generates internal biasing when immersed in solution [497–499]

13 Silicon (Si), (100) p

–

substrate (stops on

n-well diffusion)

TMAH(25 wt% in

H

2

O), with and

without IPA

80

◦

C; TMAH etchant (25 wt%) with 0 and 17% (by volume) IPA added; 3-terminal

and 4-terminal configurations (–1.5 V on p-substrate and +1.0 V on n-bridges);

Ag/AgCl reference electrode; Pt c ounterelectrode; reflux condenser; bubbling N

2

;

sealed wafer chuck; dip in DHF etchant prior to etching; etch in darkness; IPA has

little effect [500]

14 Silicon (Si), (100) p

–

substrate (stops on n

–

Si)

varies Aqueous alkali

(CsOH, KOH,

LiOH, NaOH,

RbOH) and others

Results vary or are unknown [501]

8 MEMS Wet-Etch Processes and Procedures 601

while etching oxide with buffered hydrofluoric acid above heavily n-doped regions

in silicon; oxide above p

+

regions will clear whereas oxide above the n

+

regions may

not. Extinguishing incident light during the last portions of the etch can diminish

or eliminate the effect [502]. Moderate levels of incident light on n-type mate-

rial in HF solutions, for example, will cause anodization and etching without any

substantial heating of the substrate. Broadband or narrowband light with energies

above the bandgap may be applied to the etched side of the wafer, although the

light can alternatively be applied to the opposite side of the wafer as generated car-

riers propagate through the wafer to the etch interface. In another configuration,

internal p–n junctions are forward biased with the application of light as in a solar

cell. Combined with judicious selection of the fraction of etched area and junction

area, p-type portions in an n-type substrate are selectively etched or preferentially

anodized and the process is stopped on the n-type material as the metallurgical junc-

tion is r eached [503]. Autogenerated potentials from thin-film metallization on the

wafer combined with external illumination allow connection-free etching of an n-

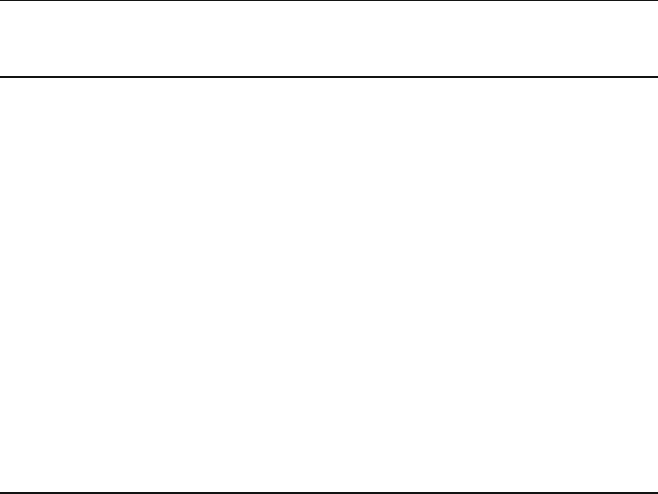

type substrate while stopping on a diffused p-layer [504], as illustrated in Fig. 8.14.

Although generally requiring no external electrical connections, electrical connec-

tions to the wafer and a potentiostat can provide the user with fuller control over

the etch process. Use of light along with external electrical connections and volt-

age control allows the production of microporous (nanoporous), mesoporous, and

macroporous silicon. Examples of photoassisted etching processes are found in

Table 8.28. Photoassisted etch stops are found in Table 8.29. Further discussions

and details may be found in the associated references and reviews [78].

Etch

Bath

Etchant

Light Source

Light

Pipe

Patterned

Wafer

PN

Junction

Modulator

Fig. 8.14 Photoassisted etch

stops use external light to

generate a photovoltage

across an internal p–n

junction and slow down the

etch rate as the junction is

exposed by the e tchant. If

passivation around the wafer

provides inadequate

protection against the etchant,

a fixture may be used

8.6.7 Thin-Film Etch Stops

Thin-film etch stops combine a deposited or otherwise formed etch-resistant layer

with a selective etchant to allow partial removal of a substrate or an adjacent film and

602 D.W. Burns

Table 8.28 Photoassisted silicon etchants and etch processes

Material

Etch

rate

(Å/s) Etchant Remarks and references

1 Silicon (Si),

(100) n

–

substrate

150–

200

HF(49%):

H

2

O

1:4

Room temperature; DHF etchant (4:1);

0-terminal configuration; photoassisted

etching (nonthermal); n-type 3E-15 cm

–3

substrate; 10 W/cm

2

optical power (UV

laser) [505]

2 Silicon (Si),

(100),

8–15 cm

415 HF(49%):

H

2

O

2:3

Room temperature; DHF etchant (3:2);

2-terminal configuration; photo-induced

preferential anodization; 500 mW/cm

2

HeNe laser source; Pt and Au

counterelectrodes; 1500:1 selectivity

enhancement over dark conditions

(0.3 Å/s) [506]

3 Silicon (Si),

(100), 2–6

cm

HF(49%):

H

2

O

1:9

15

◦

C; DHF etchant (9:1); 2-terminal

configuration; photoassisted etching;

macroporous silicon; +2 V applied to n

+

ion-implanted layer on wafer backside; Pt

wire counterelectrode; added 0.1 mM of

Triton X-100 surfactant; modulated light

intensity produced modulated pore size

with depth [507, 508]

stop automatically on the etch-stop layer. The thin film etches slowly or negligibly

in the etchant, and can simultaneously serve as a passivation layer or a hard mask.

The thin film can become free-standing, extremely fragile, and prone to buckling if

not in tension as the substrate is etched, requiring careful handling during rinsing

and subsequent handling steps.

Endpoints can be visibly detected if the etch stop material is transparent. Silicon

dioxide and silicon nitride are transparent and have high selectivity to many of

the anisotropic silicon etchants, although the oxide is generally under severe com-

pression and may distort appreciably when etched free. Although some metals

are sufficiently resistant to extended time in silicon etchants, the use of dielec-

tric thin-film stops additionally provide electrical isolation f or buried traces and

active devices while protecting the devices during the etch. Double layers of thin-

film etch stops can reduce the detrimental effects of defects such as pinholes.

The etch-stop layer may be built in, such as a buried oxide layer in an SOI

wafer. Thin-film etch stops generally allow multiple wafers to be chemically etched

simultaneously in a batch format, as illustrated in Fig. 8.15. Table 8.30 presents

some thin-film etch stops and their etch rates in some common anisotropic silicon

etchants.

8 MEMS Wet-Etch Processes and Procedures 603

Table 8.29 Photoassisted etch stops and processes

Material

Etch

rate

ratio Etchant Remarks and references

1 Silicon (Si),

(100) p

–

epi buried

layer (stops

on n

+

substrate

and n

–

surface

features)

HF(49%):H

2

O

1:4

Room temperature; DHF etchant (4:1);

0-terminal configuration;

photo-induced preferential anodization

(PIPA); forward-biased p–n junctions

to generate photocurrent; n-type

1 × 10

18

cm

−3

substrate; p-type

1 × 10

18

cm

−3

buried layer; n-type

1 × 10

15

cm

−3

beams; 30 mW/cm

2

Xenon lamp; no metal electrodes;

10 Å/s l ateral porous silicon formation

rate; remove oxidized porous silicon

layer with HF after 1000

◦

Cwet

oxidation; 20 µmwide,1µm-thick

beams formed [503]

2 Silicon (Si),

(100) n

–

substrate

(stops on

p

–

diffusion)

HF(49%):H

2

O

1:9

Room temperature; DHF etchant (9:1);

3-terminal configuration; photoassisted

etching of n-regions (1 × 10

15

cm

−3

)

around and below 3.3 µm-thick p-type

diffused structures; +4.0 V wrt SCE

applied to n-substrate via ohmic

contact; p

–

regions biased at –4.3 V wrt

n-substrate; 2 W/cm

2

illumination; etch

rate ∼400 Å/s for lower bias (+1.5 V

SCE); clear porous silicon layer with

HF:HNO

3

:Acetic 3:16:1 for 5 s or with

25 wt% KOH for 30 s at room

temperature [509, 510]

3 Silicon (Si),

(100) n

–

substrate

(stops on

p

–

epi or

diffusion)

KOH:H

2

O

500 g:1000

mL

60–75

◦

C; KOH etchant (30 wt%) (7 M);

0-terminal configuration; photovoltaic

electrochemical etch stop (PHET);

p-type diffusions (e.g., p-well); uses

topside illumination and Pt film

connected to n-regions for

electrochemical cell; no electrical

connections needed to the wafer;

restrictions on etch-stop area [504]

8.6.8 Examples: Wet Chemical and Electrochemical Etch Stops

8.6.8.1 Example 1: Anisotropic Silicon Etching of an SOI Wafer

An 8000 Å silicon nitride layer and a 1.2 µm-thick thermal oxide on the backs

and fronts of double-sided polished SOI wafers are patterned etched with large