Wilamowski B.M., Irwin J.D. The Industrial Electronics Handbook. Second Edition: Industrial Communication Systems

Подождите немного. Документ загружается.

24-2 Industrial Communication Systems

real-time.Ethernet.[KG04,EI03,F05]),.this.chapter.focuses.solely.on.protocols.that.have.already.been.

stan

dardized

.by.the.ARI

NC

.com

mittee.

In

.Sect

ion

.24.2.of.this.chapt

er,

.the.main.evol

ution

.of.avio

nics

.syst

ems

.and.the.stan

dardization

.unde

r-

taken

.by.ARIN

C

.are.brie

y

.revi

ewed.

.e.clas

sic

.avio

nics

.cont

ext

.is.pres

ented

.in.Sect

ion

.24.3.and.inte

-

grated

.modu

lar

.avio

nics

.conc

epts

.are.outl

ined

.in.Sect

ion

.24.4

.

.ARIN

C

.629.proto

cols

.for.cont

rolling

.

acce

ss

.to.a.mult

iplexed

.data.bus.are.desc

ribed

.in.Sect

ion

.24.5

.

.Sect

ion

.24.6.is.devo

ted

.to.the.pres

entation

.

of.ARIN

C

.664.avio

nics

.full

-duplex

.Ether

net

.mech

anisms.

.End-

to-end

.dela

y

.anal

ysis

.meth

ods

.are.sum-

m

arized

.in.Sec

tion

.24.

7.

24.2 avionics Systems Evolution and arINC Context

Avionics.is.the.generic.name.given.to.the.electronic.systems.installed.in.an.aircra..It.includes,.for.

exam

ple,

.the.calc

ulators

.and.thei

r

.sow

are,

.the.sens

ors

.and.actu

ators,

.and.all.the.comm

unication

.link

s

.

betw

een

.thes

e

.elem

ents.

.Each.func

tion

.of.an.airc

ra

.is.impl

emented

.thro

ugh

.a.give

n

.avio

nics

.syst

em:

.

comm

and

.cont

rols,

.autop

ilot,

.navi

gation,

.info

rmation

.disp

lay,

.and.cabi

n

.mana

gement.

.In.the.1950

s,

.

avio

nics

.were.very.simpl

e

.stan

dalone

.syst

ems

.in.whic

h

.each.func

tion

.was.exec

uted

.using.a.singl

e

.calc

u-

lator.

.Mode

rn

.avio

nics

.bega

n

.in.the.1960

s

.with.the.repl

acement

.of.anal

og

.devi

ces

.by.thei

r

.digi

tal

.equi

v-

alents.

.Sinc

e

.then

,

.the.comp

lexity

.of.avio

nics

.has.cont

inually

.incr

eased:

.More.and.more.anal

og

.devi

ces

.

are.beco

ming

.outd

ated

.and.requ

ire

.new.digi

tal

.repl

acements,

.and.new.func

tions

.are.cont

inuously

.bein

g

.

adde

d.

.ese.func

tions

.bene

t

.from.impr

ovements

.in.elec

tronics

.and.hard

ware

.exec

ution

.and.comm

u-

nication

.arch

itectures.

.ey.can.be.answ

ers

.to.the.new.need

s

.inhe

rent

.in.the.evol

ution

.of.civi

l

.avia

tion

.

or.simpl

y

.bett

er

.answ

ers

.to.exis

ting

.prob

lems,

.like.the.y-by

-wire

.comm

and

.syst

em.

.A.few.fact

s

.clea

rly

.

illu

strate

.the.grow

th

.of.the.role.of.avio

nics

.in.civi

lian

.airc

ra:

.From.1983.(A31

0)

.to.1993.(A34

0),

.the.

numbe

r

.of.onbo

ard

.avio

nics

.syst

ems

.incr

eased

.by.almo

st

.50%.(fro

m

.77.to.115)

,

.whil

e

.total.proc

essing

.

powe

r

.was.mult

iplied

.four

fold,

.from.60.to.250.Mips

.

.Desig

ning

.and.manu

facturing

.new.civi

lian

.airc

ra

.

has.led.to.an.incr

ease

.in.the.numbe

r

.of.embed

ded

.syst

ems

.and.func

tions

.and.cons

equently,

.an.incr

ease

.

in.com

munication

.nee

ds

.[CC

93].

Avionics

.syst

ems

.are.subje

ct

.to.volu

me

.and.weig

ht

.limi

tations

.and.must.also.oper

ate

.corr

ectly

.even.

in.seve

re

.cond

itions:

.heat

,

.vibr

ations,

.elec

tromagnetic

.inte

rferences,

.etc..Howe

ver,

.the.main.char

acter-

istics

.lie.in.the.safe

ty

.leve

l

.they.requ

ire.

.Foll

owing

.ARP.4754.[SAE9

6],

.syst

ems

.are.clas

sied

.acco

rding

.

to.the.eects.of.their.failure:.catastrophic,.hazardous,.major,.minor,.or.no.eect..For.example,.a.system.

is.clas

sied

.as.“cat

astrophic”

.if.its.fail

ure

.can.lead.to.the.total.loss.of.an.airc

ra.

.e.segr

egation

.of.crit

i-

cal

.func

tions

.lead

s

.to.a.dist

ributed

.arch

itecture

.with

out

.any.cent

ralized

.cont

rol:

.the.syst

ems

.coop

erate

.

thro

ugh

.data.exch

ange

.than

ks

.to.data.buse

s.

.Typi

cally,

.clas

sic

.avio

nics

.uses.piec

es

.of.equi

pment

.that.can.

be.seen.as.hard

ware

.and.sow

are

.blac

k

.boxe

s,

.whic

h

.are.each.resp

onsible

.for.one.give

n

.func

tion.

.e.

physi

cal

.devi

ces

.adopt.a.stan

dardized

.modu

le

.form

,

.call

ed

.line.repl

aceable

.unit

s

.(LRU

).

.ese.modu

les

.

inco

rporate

.memo

ry

.and.proc

essing

.reso

urces

.and.prov

ide

.a.stan

dardized

.appl

ication

.inte

rface

.(API

)

.

to.thes

e

.reso

urces.

.is.stan

dardization

.ease

s

.main

tenance

.acti

vity,

.since.any.piec

e

.of.equi

pment

.can.be.

easil

y

.repl

aced

.by.anot

her

.LRU,.prov

ided

.the.appr

opriate

.code.has.been.load

ed.

.New.conc

epts

.base

d

.on.

bett

er

.shar

ing

.of.exec

ution

.and.comm

unication

.reso

urces

.were.prop

osed

.in.the.1990

s.

.IMA.intr

oduced

.

the.den

ition

.of.a.gene

ric

.plat

form

.call

ed

.“cab

inet”

.comp

osed

.of.stan

dard

.exec

ution

.and.tran

smission

.

modu

les,

.call

ed

.line.repl

aceable

.modu

les

.(LRM

);

.this.will.be.pres

ented

.in.Sect

ion

.24.3

.

.e.glob

al

.IMA.

arch

itecture

.is.thus.comp

osed

.of.modu

les

.hous

ed

.in.cabi

nets

.dist

ributed

.thro

ughout

.the.airc

ra,

.lead

-

ing

.to.new.int

racabinet

.and.int

ercabinet

.com

munication

.nee

ds.

Aeronautical

. Radi

o

. Inco

rporated

. (ARI

NC)

. prov

ided

. lead

ership

. in. deve

loping

. spec

ications

. and.

stan

dards

.for.avio

nics

.equi

pment.

.Most.of.the.prop

osed

.spec

ications

.and.stan

dards

.were.deve

loped

.

and.main

tained

.by.the.Airl

ines

.Elec

tronic

.Engi

neering

.Comm

ittee

.(AEE

C)

.comp

rising

.membe

rs

.that.

repr

esent

.airl

ines,

.gove

rnments,

.and.ARIN

C.

.ARIN

C

.stan

dardized

.the.trad

itional

.ARIN

C

.429.mono

-

emitter

.data.bus.[ARI

01],

.whic

h

.has.been.wide

ly

.used.in.clas

sic

.avio

nics

.arch

itectures

.cont

ext.

.e.ARIN

C

.

629.mult

iplexed

.data.bus.[ARI

99]

.was.desig

ned

.with.IMA.in.mind

.

.IMA.itse

lf

.is.comp

osed

.of.two.

© 2011 by Taylor and Francis Group, LLC

Embedded Networks in Civilian Aircraft Avionics Systems 24-3

ARINC.standards:.ARINC.651.for.the.description.of.the.modular.hardware.architecture.[ARI91].and.

ARINC.653.for.the.modular.soware.architecture.[ARI97]..More.recently,.the.ARINC.664.has.provided.

an.answer.to.the.problem.of.increased.communication.by.multiplexing.huge.amounts.of.communica-

tion

.data.over.a.full-duplex.switched.Ethernet.network.[ARI02,ARI03]..It.has.become.the.reference.

communication.technology.in.the.context.of.civilian.aircra.avionics.since.it.provides.a.backbone.

network.for.the.avionics.platform.

24.3 Classic avionics and arINC 429

ARINC.429.is.the.earliest.and.most.commonly.used.standard.for.civilian.aircra.avionics.and.has.

been.installed.on.the.majority.of.Airbus.and.Boeing.aircra..It.employs.a.unidirectional.data.bus.

standard.known.as.the.Mark.33.digital.information.transfer.system.(DITS)..Messages.are.transmit-

ted

.over.two.twisted.pairs.by.the.owner.of.the.bus.to.other.system.units.at.a.bit.rate.of.either.12.5.

or.100.kbps..e.specication.denes.electrical.transmission.characteristics.and.protocol.data.unit.

features.[ARI01].

e

.ARINC.429.protocol.implements.a.mono-emitter.broadcast.bus.with.up.to.20.receivers..Messages.

sent.by.the.sole.transmitter.consist.of.a.single.32.bits.data.word..e.label.eld.of.the.word.denes.the.

type.of.data.that.is.contained.in.the.rest.of.the.word..ARINC.429.data.words.use.ve.primary.elds:.

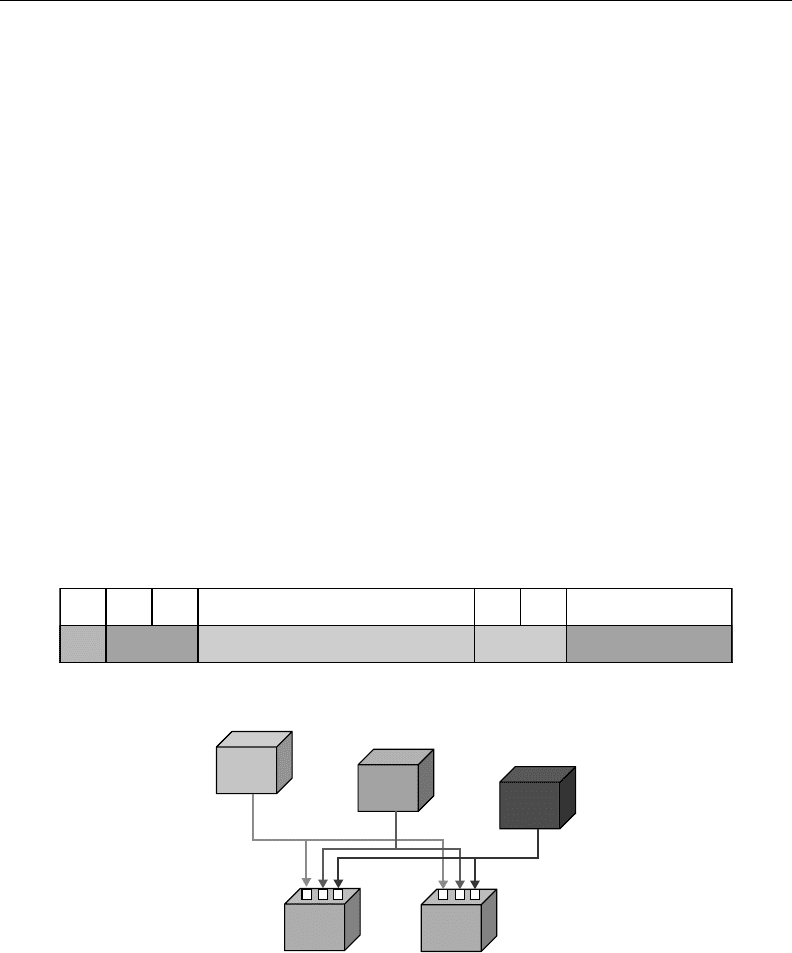

parity,.SSM,.data,.SDI,.and.label..As.represented.in.Figure.24.1,.the.ARINC.429.data.word.is.composed.

as.follows:.bit.32.is.the.parity.bit;.bits.31.and.30.contain.the.sign/status.matrix.(SSM).eld.that.contains.

equipment.conditions,.operational.modes,.or.validity.of.data.content;.bits.29.through.11.contain.the.

data;.bits.10.and.9.provide.a.source/destination.identier.(SDI);.and.bits.8.through.1.contain.a.label.

identifying.the.data.and.associated.parameters.

e

.label.is.an.important.part.of.the.message..It.is.used.to.identify.the.transmitted.data.and.to.deter-

mine

.the.data.type..e.emitter.broadcasts.the.data.(with.a.given.periodicity).on.the.bus.and.does.not.

know.which.equipment.will.receive.a.given.instance.of.data..Each.receiver.lters.the.data.according.to.

the.label.of.each.data..e.SDI.is.used.to.identify.the.receiver.to.which.the.data.is.destined..If.a.given.

label.can.be.sent.on.dierent.data.buses,.it.can.also.be.used.to.identify.the.source.of.the.transmission.(as.

units.are.assigned.digital.identication.numbers.called.equipment.id).

ARINC

.429.is.confronted.with.an.increasing.number.of.intercommunicating.avionics.functions..e.

(point.to.multi-point.and.unidirectional).characteristics.of.the.ARINC.429.protocol.mean.that.the.avi-

onics

.system.must.include.an.ARINC.429.bus.for.each.communication.path.as.depicted.in.Figure.24.2..

32 31 30

P SSM

29 11

10 9

8 1

Data SDI Label

FIGURE 24.1 ARINC.429.data.word.

G1 G2

F2

F1

F3

FIGURE 24.2 Classic.avionics.architecture.

© 2011 by Taylor and Francis Group, LLC

24-4 Industrial Communication Systems

Moreover,.an.ARINC.429.transmitter.can.transmit.to.a.maximum.of.20.receivers..While.the.ARINC.

429.data.bus.provides.high.determinism,.point-to-point.wiring.has.become.a.major.problem.in.systems.

composed.of.multiple.emitting.units.

24.4 Integrated Modular avionics

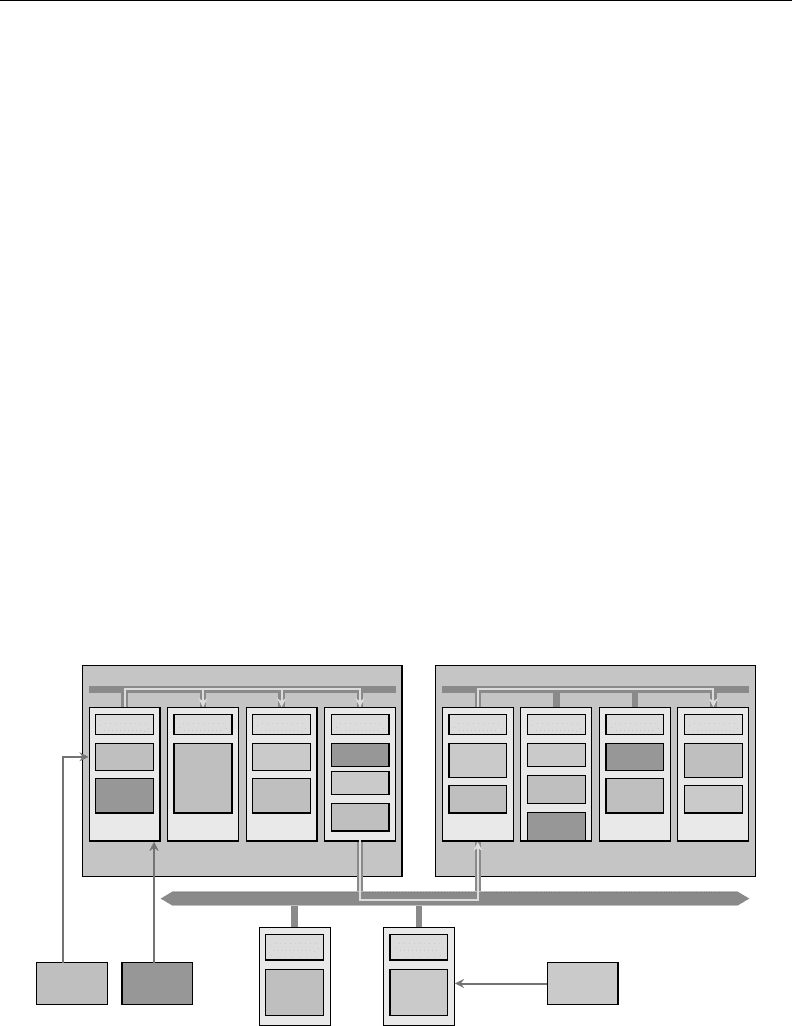

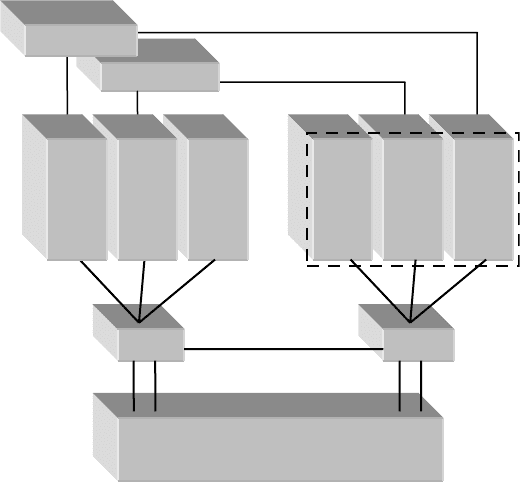

e.IMA.concept.has.introduced.the.sharing.of.execution.and.communication.resources..IMA.hard-

ware

.architecture,. as.described. in. the. standard.ARINC.651.[ARI91],.is.represented. in.Figure.24.3..

Execution.and.communication.resources.are.described.as.standard.LRMs.that.are.installed.in.common.

cabinets..ree.types.of.modules.have.been.designed:.core.modules.for.application.execution,.input–

output

.modules.for.communications.with.non-IMA.equipment.(existing.LRUs),.and.gateway.modules.

for.communicating.among.cabinets..e.ARINC.659.back.plane.data.bus.standard.has.been.used.for.

communication.between.modules.hosted.in.the.same.cabinet.[ARI93]..Communication.among.cabinets.

needs.new.aircra.data.buses.such.as.ARINC.629.[ARI99].

ARINC

.653.[ARI97].describes.how.many.avionics.subsystems.can.share.the.execution.resources.of.

an.IMA.architecture..In.an.ARINC.653.environment,.an.avionics.subsystem.is.no.longer.implemented.

on.a.dedicated.CPU.or.LRU.but.is.viewed.as.a.partition,.to.which.is.assigned.a.time.window.to.execute.

its.code.on.a.shared.core.processing.module.(CPM)..Each.partition.becomes.a.virtual.CPU.or.LRU..

A.robust.partitioning.concept.is.introduced.to.guarantee.isolation.between.subsystems.running.on.the.

same.execution.computer..Spatial.isolation.is.guaranteed.by.protecting.the.address.space.of.each.parti-

tion

.(for.example,.by.a.memory.management.unit)..Temporal.isolation.is.based.on.the.static.allocation.

of.CPU.time.to.each.partition..Time.partitioning.guarantees.that.each.user.partition.obtains.a.slice.of.

time.for.execution.as.determined.by.the.integrator.as.a.worst-case.execution.time.(easier.to.evaluate.for.

systems.that.have.mostly.periodic.processes)..e.main.objective.is.to.guarantee.that.an.avionic.subsys-

tem

.running.in.a.given.partition.will.have.no.eect.on.other.subsystems.running.in.other.partitions..

Partitions.communicate.with.each.other.by.exchanging.messages.through.communication.ports..Two.

types.of.communication.ports.can.be.used:.sampling.ports.(periodic.data—only.the.last.value.of.data.

is.stored).and.queuing.ports.(all.the.values.of.data.are.stored)..A.logical.channel.concept.is.used.to.link.

communicating.ports.(multicast.scheme—1.emitter.and.N.receivers).independently.of.the.underlying.

data.bus.or.network.stack..Mechanisms.are.needed.in.order.to.schedule.inputs–outputs.according.to.the.

needs.of.each.partition.(for.example,.port.sizes.and.depths.must.be.determined.on.a.worst.case.commu-

nication

.basis)..In.conclusion,.the.ARINC.653.interface.between.application.soware.and.the.run-time.

Backplane Backplane

F1 F3

F1

F1

F3

F1

F2

F3

F1

F2

F3

F1

F

3

F1

F2

Eq F3

ARINC 429

API

F3

Aircraft data bus

F1

API

Eq F2 Eq F1

ARINC 429

F1

APEX/C APEX/C APEX/C APEX/C APEX/C APEX/C APEX/C APEX/C

F2

FIGURE 24.3 IMA.avionics.architecture.

© 2011 by Taylor and Francis Group, LLC

Embedded Networks in Civilian Aircraft Avionics Systems 24-5

executive.called.application.executive.(APEX).is.an.important.step.in.developing.avionics.applications.

with

out

.kno

wing

.the.cha

racteristics

.of.the.tar

get

.pro

cessing

.and.com

municating

.arc

hitecture.

e

.rst.exam

ples

.of.IMA.impl

ementation,

.such.as.the.Boei

ng

.777.airp

lane

.info

rmation

.mana

gement

.

syst

em

.(AIM

S)

.show.many.pote

ntial

.bene

ts:

.adapt

ability

.(tha

nks

.to.the.modu

larity

.of.the.arch

itecture,

.

it.is.easy.to.con

gure

.the.airc

ra

.for.a.give

n

.missi

on),

.main

tainability

.(the.stan

dardization

.of.the.mod-

u

les

.simpl

ies

.the.main

tenance),

.cost.redu

ctions

.(easi

er

.main

tenance

.and.hard

ware

.evol

ution

.cut.down.

cost

s),

.and.a.decr

ease

.in.weig

ht

.and.volu

me

.(few

er

.devi

ces

.are.need

ed

.than.with.prev

ious

.arch

itectures).

.

Consi

dering

.thes

e

.bene

ts,

.Airb

us

.chos

e

.the.IMA.arch

itecture

.for.the.A380

,

.and.Boei

ng

.reus

ed

.the.

IMA.conc

epts

.for.the.787.airc

ra.

.Sinc

e

.the.arch

itecture

.is.inde

pendent

.of.the.chos

en

.comm

unication

.

meth

od

.used

,

.we.will.pres

ent

.in.foll

owing

.sect

ions

.the.ARIN

C

.629.mult

iplexed

.data.bus,.whic

h

.was.

chos

en

.for.the.Boei

ng

.777.AIMS.and.the.ARIN

C

.664.or.AFDX

,

.whic

h

.was.chos

en

.as.the.basis.of.the.

IMA.arc

hitecture

.of.the.A38

0.

24.5 arINC 629 Multiplexed Data Bus

Development.of.the.ARINC.629.[ARI99].multiplexed.data.bus.began.when.avionics.systems.designers.real-

ized

.that.the.ARIN

C

.429.sing

le

.tran

smitter/multiple

.recei

ver

.conc

ept

.coul

d

.not.cope.with.the.incr

easing

.

amou

nt

.of.inte

rsystem

.data.tran

sfer

.requ

ired

.for.evol

ving

.comm

ercial

.airc

ra.

.e.prim

ary

.advan

tages

.of.

a.mult

i-transmitter

.data.bus.such.as.the.ARIN

C

.629.incl

ude

.the.abil

ity

.to.move.more.data.betw

een

.LRUs.

at.high

er

.rate

s

.usin

g

.fewe

r

.wire

s.

.Also.they.are.gene

rally

.more.reli

able

.and.prov

ide

.an.arch

itecture

.allo

w-

ing

.the.inte

gration

.of.comp

lex

.syst

ems.

.Howe

ver,

.mult

itransmitter

.buses.have.been.main

ly

.used.in.the.

cont

ext

.of.mili

tary

.airc

ra.

.e.MIL-

STD-1553

.data.bus.stan

dard

.[MIL

78]

.has.been.deve

loped

.for.mili

tary

.

and.spac

e

.syst

ems.

.It.impl

ements

.a.bus.arch

itecture

.in.whic

h

.all.the.devi

ces

.atta

ched

.to.the.bus.are.capa

ble

.

of.recei

ving

.and.tran

smitting

.data

.

.Howe

ver,

.it.uses.a.comm

and/response

.(cen

tralized)

.mecha

nism

.that.

does.not.sati

sfy

.the.term

inal

.inde

pendence

.needed.for.cert

ication

.of.comm

ercial

.airc

ra.

.More

over,

.clas

-

sic

.Ethe

rnet

.arch

itecture

.and.its.rand

om

.CSMA

-CD

.mediu

m

.acces

s

.cont

rol

.mecha

nism

.cann

ot

.guar

antee

.

peri

odic

.tra

c.

.e.digi

tal

.auto

nomous

.term

inal

.acces

s

.comm

unication

.(DAT

AC)

.proj

ect

.enge

ndered

.

the.ARIN

C

.629.[ARI

99],

.an.avio

nics

.indu

stry

.digi

tal

.comm

unications

.stan

dard,

.whic

h

.was.chose

n

.as.the.

prim

ary

.digi

tal

.comm

unication

.syst

em

.on.the.Boei

ng

.777.

is

.stan

dard

.allo

ws

.the.tran

smission

.of.mess

ages

.at.a.2.Mbps.seri

al

.data.rate.on.twis

ted

.pair.cond

uctors.

.

A.mess

age

.has.vari

able

.leng

th

.and.is.comp

rised

.of.up.to.31.word.stri

ngs.

.Each.word.stri

ng

.has.vari

able

.leng

th

.

and.cont

ains

.a.16.bit.labe

l

.word.and.up.to.256.data.word

s

.(eac

h

.16.bit.word.is.actu

ally

.tran

smitted

.with.

3.addi

tional

.bits.of.sync

hronization

.and.a.pari

ty

.bit)

.

.Each.LRU.comm

unicating

.on.the.ARIN

C

.629.data.bus.

cont

ains

.a.term

inal

.cont

roller,

.whic

h

.impl

ements

.the.bus.prot

ocol

.acce

ss

.logi

c

.that.dete

rmines

.when.the.ter-

m

inal.will.transmit..e.terminal.listens.to.the.bus.and.waits.for.series.of.quiet.periods,.one.of.unique.dura-

tion

.befo

re

.tran

smitting

.(CSM

A

.like.mech

anism

.+.TDMA.like.allo

cation

.by.the.den

ition

.of.preas

signed

.

wait

ing

.time

s).

.Only.one.term

inal

.is.allo

wed

.to.tran

smit

.at.a.time

,

.and.once.a.term

inal

.has.tran

smitted,

.it.

must.wait.befo

re

.it.tran

smits

.agai

n

.to.give.time.to.all.othe

r

.term

inals

.whic

h

.want.to.tran

smit

.on.the.bus..

e.ARI

NC

.629.sta

ndard

.sup

ports

.two.alt

ernative

.data.lin

k

.lev

el

.pro

tocols,

.the.basi

c

.pro

tocol

.(BP

)

.and.the.

comb

ined

.prot

ocol

.(CP)

,

.whic

h

.canno

t

.coex

ist

.on.the.same.bus.due.to.funda

mental

.die

rences.

24.5.1 Basic Protocol

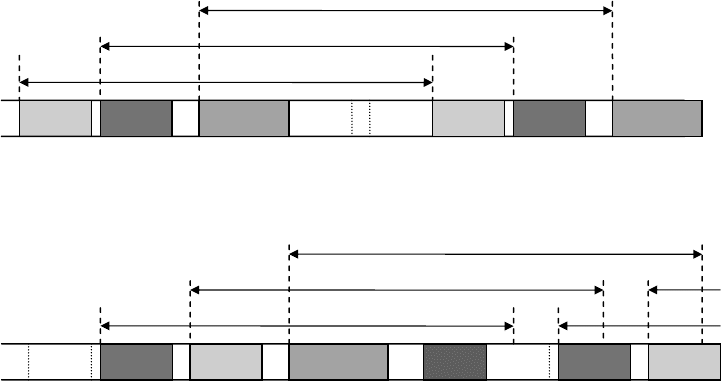

e.BP.provides.an.equal.priority.access.to.the.bus.for.each.terminal,.giving.the.opportunity.to.transmit.

peri

odic

.data

.

.Howe

ver,

.as.show

n

.in.Figu

re

.24.4

,

.if.the.cycl

e

.is.too.shor

t

.to.tran

smit

.the.data.from.all.

term

inals,

.the.bus.auto

matically

.lose

s

.this.peri

odic

.beha

vior

.in.favo

r

.of.an.aper

iodic

.mode.wher

e

.

all.mess

ages

.are.tra

nsmitted,

.wit

hout

.dat

a

.los

s.

For

.a.give

n

.term

inal

.i.(fro

m

.a.set.of.n.conn

ected

.to.the.bus)

,

.TGi.repr

esents

.the.uniq

ue

.time.(ter

mi-

nal

.gap)

,

.duri

ng

.whic

h

.a.term

inal

.must.wait.aer.bus.acti

vity

.befo

re

.star

ting

.its.own.tran

smission.

.For.

all.n.term

inals,

.TI.repr

esents

.a.comm

on

.time.inte

rval

.(tra

nsmit

.inte

rval),

.sepa

rating

.two.succ

essive

.

© 2011 by Taylor and Francis Group, LLC

24-6 Industrial Communication Systems

transmissions.of.each.terminal..Finally,.the.synchronization.gap.(SG).is.a.common.quiet.time,.longer.

than.any.individual.TG,.which.is.used.to.synchronize.all.the.terminals.at.the.beginning.of.a.new.cycle.

ese

.three.timers.are.used.at.each.terminal.in.the.following.manner:

•

. e.TI.timer.starts.immediately.every.time.the.terminal.begins.transmitting.

•

. e.SG.timer.starts.immediately.every.time.the.bus.is.sensed.quiet..is.timer.may.be.reset.before.

it.has.elapsed.if.any.activity.is.detected.on.the.bus..is.timer.does.not.aect.periodic.mode.but.in.

aperiodic.mode,.aer.it.has.elapsed.we.know.that.all.the.terminals.have.had.transmit.access.to.the.

bus.(as.SG.timer.is.greater.than.each.TGi.timer).and.so.a.new.cycle.can.begin.

•

. A.TGi.timer.will.start.aer.SG.has.elapsed..It.also.starts.immediately.every.time.the.bus.is.sensed.

quiet..is.timer.may.also.be.reset.before.it.has.elapsed.if.any.bus.activity.is.detected.

If

.all.three.timers.have.elapsed,.the.local.terminal.begins.transmitting..As.all.TGi.are.dierent,.only.

one.terminal.will.be.allowed.to.transmit.aer.any.quiet.time..In.aperiodic.mode,.the.terminals.are.

scheduled.in.ascending.order.of.their.TGs.

e

.assignment.of.timer.values.is.done.on.a.per-system.basis.and.must.address.a.trade-o.between.

bus.cycle.time.(all.terminals.transmit.exactly.once.within.a.cycle).and.terminal.transmission.frequency.

(all.terminals.must.be.allowed.to.transmit.at.a.frequency.suitable.for.data.update.rate.requirements).

24.5.2 Combined Protocol

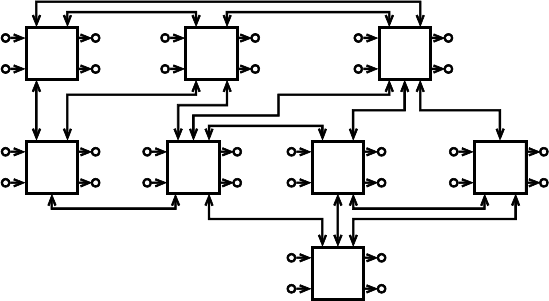

e.CP.has.been.proposed.for.combining.periodic.and.aperiodic.data.transmission..As.shown.in.Figure.24.5,.

three.levels.of.transmission.are.handled:.level.one.for.periodic.transmissions,.level.two.for.shorter.(and.higher.

priority).aperiodic.transmissions,.and.level.three.for.longer.(and.lower.priority).aperiodic.transmissions.

As

.with.BP,.each.terminal.has.a.unique.preassigned.TG..e.transmit.interval.(TI).is.only.applicable.dur-

ing

.the.rst.periodic.transmission.in.each.cycle;.for.all.other.terminals,.a.concatenation.event.(CE).forces.

all.unelapsed.TI.timers.to.be.canceled..is.has.the.eect.of.compressing.periodic.transmissions.at.the.start.

of.each.cycle.(separated.only.by.TG.delays)..Two.types.of.SGs.are.dened:.the.periodic.synchronization.gap.

(PSG),.which.is.used.for.cycle.level.synchronization;.and.the.aperiodic.synchronization.gap.(ASG),.which.is.

needed.to.handle.transition.in.a.cycle.between.levels.1.and.(and.between.levels.2.and.3)..In.order.to.guarantee.

Basic protocol : periodic mode (when TI is sufficiently large)

Basic protocol : aperiodic mode (when TI is too small)

M1

TG

2

TG

3

M2 M3

TG

1

SG

M1

TG

2

TG

3

M2

TI (terminal 1)

TI (terminal 2)

Free

space

TI (terminal 3)

M3

M1

TG

2

TG

4

M2

TG

1

SG

M1

TG

2

TG

3

M2

TI (terminal 1)

TI (terminal 2)

TI (terminal 3)

M3

SG

M4

TG

1

FIGURE 24.4 ARINC.629.basic.protocol.

© 2011 by Taylor and Francis Group, LLC

Embedded Networks in Civilian Aircraft Avionics Systems 24-7

a.xed.cycle.duration.(needed.for.level.1.periodic.transmissions),.an.aperiodic.time-out.(AT).is.used.to.avoid.

transmission.of.aperiodic.data.that.could.make.the.cycle.overow..Level.3.aperiodic.messages.are.allowed.to.

span.multiple.cycles.(backlog.messages.have.a.higher.priority.than.current.cycle.level.three.messages)..Level.

2.aperiodic.messages.must.be.transmitted.in.the.current.cycle.otherwise.they.are.lost;.the.transmit.interval.

must.be.calculated.so.as.to.give.enough.space.for.both.levels.1.and.2.messages.

e

.assignment.of.timer.values.is.similar.to.BP.mode:.ASG.is.equivalent.to.SG.(greater.than.each.TGi).

and.PSG.must.be.greater.than.ASG.(the.standard.denes.PSG.as.ve.times.the.selected.ASG).

In

.conclusion,.implementing.an.ARINC.629.data.bus.requires.the.development.of.a.global.avionics.

system.communication.scheme.in.order.to.guarantee.deterministic.transmission.ordering.for.critical.

data..BP.delivers.true.real-time.behavior.for.systems.requiring.periodic.and.xed.length.messages.(peri-

odic

.mode)..Variable.length.periodic.messages.or.aperiodic.messages.result.in.variable.length.cycles.

(aperiodic.mode)..CP.protocol.oers.stable.periodic.response.time.for.systems,.which.require.some.

combination.of.periodic.and.aperiodic.transmissions.(with.no.interference.of.aperiodic.messages.on.

periodic.messages)..However,.taking.into.account.sporadic.or.aperiodic.messages.can.lead.to.an.under-

utilization

.of.the.data.bus..In.fact,.the.main.drawback.of.the.ARINC.629.has.been.the.cost.of.interfacing.

an.ecient.but.complex.avionics-specic.communication.protocol.

24.6 arINC 664: avionics Full-Duplex Ethernet

Avionics.full-duplex.Ethernet.(AFDX).is.part.of.the.ARINC.664.standard.and.is.based.on.classic.switched.

Ethernet.technology.but.introduces.a.virtual.link.(VL).paradigm,.which.is.an.important.concept.for.

characterizing.the.incoming.trac.of.the.network.

24.6.1 Full-Duplex Switched Ethernet

Reusing.Ethernet.technology.for.avionics.presents.many.advantages:.high.throughput.oered.to.the.

connected.units.(100.Mbps.compared.to.a.few.Mbps.with.the.ARINC.629.standard),.high.connectivity.

given.by.the.network.structure,.a.mature.industrial.standard,.and.a.signicantly.lower.connection.cost.

than.with.a.proprietary.or.aeronautical.specic.protocol..Despite.these.advantages,.Ethernet.was.not.

used.for.critical.systems.in.previous.aircra.because.of.its.random.physical.medium.access.protocol:.

CSMA/CD.[IEEE98]..An.embedded.network.must.have.determinism.properties.such.as.the.bounded.

transmission.delay.of.any.data..e.CSMA/CD.protocol.fails.to.oer.such.a.guarantee.because.of.poten-

tial

.collisions.on.the.physical.medium.during.the.transmission.and.because.of.random.(binary.

exponential.back-o.[BEB]).retransmission.algorithms.

To

.solve.this.problem,.the.rst.assumption.was.to.adopt.a.switched.Ethernet.technology;.all.units.are.

directly.connected.by.a.point-to-point.link.to.an.Ethernet.switch.since.cascading.switches.oer.the.desired.

M1

TG

3

TG

1

TG

2

M2 M3

ASG

TI

Level 1 Level 2 Level 3 Level 3

ASG ASG PSG

AT

FIGURE 24.5 ARINC.629.combined.protocol.

© 2011 by Taylor and Francis Group, LLC

24-8 Industrial Communication Systems

connectivity..is.reduces.the.possible.collision.domain.from.the.entire.network.to.the.single.link.between.

two.elements..e.second.assumption.consisted.in.using.full-duplex.links:.each.avionics.subsystem.is.

connected.to.a.switch.via.a.full-duplex.link.comprised.of.two.twisted.pairs.(one.pair.for.transmission.and.

one.pair.for.reception)..In.fact,.full-duplex.switched.Ethernet.eliminates.the.possibility.of.transmission.

collisions.on.links:.the.CSMA-CD.medium.access.control.protocol.is.no.longer.necessary..is.eliminates.

the.inherent.indeterminism.of.vintage.Ethernet.and.the.collision.frame.loss,.and.shis.the.problem.to.the.

switch.level.where.various.ows.enter.into.competition.for.the.use.of.switch.resources..e.switch.imple-

ments

.the.classic.IEEE.802.1d.bridging.algorithm.[IEEE98]:.Reception.and.transmission.buers.are.used.

in.the.switch.for.storing.multiple.incoming.and.outgoing.Ethernet.frames..e.role.of.the.switch.is.to.

lter.and.to.retransmit.frames.from.the.incoming.buers.to.the.outgoing.buers..e.store.and.forward.

bridging.mechanism.reads.the.destination.addresses.of.each.received.frame.and.retransmits.them.accord-

ing

.to.the.port.ID.stored.in.the.forwarding.table.of.the.switch..If.a.temporary.congestion.appears.on.the.

output.port.of.a.switch,.it.can.signicantly.increase.end-to-end.delays.of.frames.and.even.lead.to.frame.

loss.through.buer.overow..is.is.why.dedicated.mechanisms.have.been.added.to.the.classic.full-duplex.

Ethernet.in.order.to.guarantee.the.determinism.of.an.AFDX.network.

24.6.2 the arINC 664 Standard

e.AFDX.has.been.initiated.by.Airbus.for.the.evolution.of.the.A380.aircra.toward.IMA.as.represented.

in.Figure.24.6..AFDX.concepts.have.been.standardized.as.in.ARINC.664.with.the.help.of.many.avionics.

manufacturers:.Airbus,.Boeing,.Rockwell.Collins,.Honeywell,.etc..[ARI02,ARI03]..is.standard.adapts.

existing.Ethernet.standards,.describes.the.global.communication.system.of.the.aircra,.and.focuses.on.

the.interconnection.of.domains.with.dierent.safety.levels..In.particular,.it.explains.how.the.critical.

avionics.domain,.responsible.for.aircra.control,.can.be.connected.to.the.open-world.domain.

More

.precisely,.the.standard.denes.two.kinds.of.embedded.networks:.compliant.networks.and.pro-

led

.networks..Compliant.networks.conform.exactly.to.existing.standards:.IEEE.802.3,.802.1d.[IEEE98].

and.can.be.used.in.the.lowest.safety-level.domains,.such.as.the.open-world.domain..Proled.networks.

deviate. from. existing. standards,. when. specic. deviations. are. needed. to. achieve. required. levels. of.

GWMIOMCPM

Switch

Switch

Open world environment

Ethernet

429

Ethernet

AFDX network

Avionics world

LRU environment

429

GWM CPM

IOM

LRU environment

FIGURE 24.6 AFDX.IMA.avionics.architecture.

© 2011 by Taylor and Francis Group, LLC

Embedded Networks in Civilian Aircraft Avionics Systems 24-9

performance.and.safety..Among.these.proled.networks.is.dened.the.subset.of.deterministic.networks.

whose.main.characteristics.can.be.summarized.as.follows:

•

. Static conguration:.e.entire.network.conguration.must.be.static.and.precisely.dened.before.any.

take-o..is.includes.the.network.topology,.the.number.of.connected.units,.the.switch.parameters,.

and.switching.tables..Algorithms.such.as.ARP,.GMRP,.and.Spanning-Tree.must.not.be.implemented.

•

. Flow segregation and error connement:.e.main.safety.principle.is.that.errors.must.be.locally.

contained,.which.means.that.a.local.error.must.not.be.propagated.in.the.network.or.cause.the.

malfunction.of.another.system..is.led.to.the.recommendation.to.implement.a.ltering.function.

in.the.switches,.whose.role.is.to.check.all.incoming.frames.and.discard.invalid.ones.including.

incorrect.length,.unknown.sender.or.destination.address,.and.corrupted.frames.(FCS.check)..

Filtering.operations.prior.to.relaying.the.frames.and.dierentiating.the.service.oered.to.each.

ow.are.mandatory.for.robust.segregation.of.ows.

•

. Controlled trac:.e.main.characteristic.of.deterministic.networks.is.that.they.guarantee.a.given.

quality.of.service.that.is.provable.(bounded.delay.or.jitter,.frame.loss.probability.by.congestion,.

and.availability.rate)..Each.trac.source.must.assume.a.given.trac.pattern.for.each.ow.(needed.

regulation.is.managed.by.trac.shaping.mechanisms.at.end.system.level)..e.network.has.to.

provide.mechanisms.in.order.to.check.that.no.source.will.transmit.more.data.than.allowed.(trac.

policing.mechanisms.are.needed.at.the.switch.level.to.discard.frames.if.the.source.has.transmitted.

too.many.frames.for.a.given.ow.over.a.short.period).

In

.conclusion,.an.ARINC.664.deterministic.network.is.based.upon.the.Ethernet.frame.denition.and.

IEEE.802.1d.switching.protocol.but.includes.specic.mechanisms.in.order.to.guarantee.the.determin-

ism

.of.avionic.communications..e.main.AFDX.specic.assumptions.deal.with.the.static.denition.of.

avionic.ows.that.have.to.respect.a.bandwidth.envelope.(burst.and.rate).at.each.network.ingress.point.

24.6.3 Virtual Link Paradigm

e.end-to-end.trac.ow.characterization.is.standardized.by.ARINC.664.in.part.7.where.the.VL.

paradigm.is.presented.[ARI03]..e.idea.behind.this.concept.is.to.segregate.the.ows.for.safety.reasons..

Yet,.each.VL.can.also.be.seen.as.a.virtual.ARINC.429.bus.dedicated.to.one.emitting.end.system..is.

makes.it.possible.to.reuse.existing.avionics.components.or.concepts,.which.decreases.the.transition.

time.between.ARINC.429.and.ARINC.664.technologies..e.denition.of.VLs.is.based.on.the.concept.

of.virtual.communication.channels..us,.it.is.possible.to.statically.dene.all.ows.(VL),.which.enter.a.

network,.as.shown.in.Figure.24.7,.which.corresponds.to.an.AFDX.network.test.conguration.provided.

by.Airbus.for.industrial.research.

113

821

820

143

66

358

1207

113

S1 S8

S4 S7

S3

S6

S5

95

132

457

708

160

857

1156

142

S2

FIGURE 24.7 Example.of.AFDX.architecture.conguration.

© 2011 by Taylor and Francis Group, LLC

24-10 Industrial Communication Systems

e.AFDX.network.architecture.is.composed.of.several.interconnected.switches..e.inputs.and.out-

puts

.of.the.network.are.the.end.systems.(the.little.circles.in.Figure.24.7)..Each.end.system.is.connected.to.

exactly.one.switch.port.and.each.switch.port.is.connected.to.either.an.end.system.or.another.switch..e.

links.are.all.full.duplex..In.Figure.24.7,.the.values.on.the.end.systems.indicate.the.number.of.VL.that.are.

dispatched.between.the.end.systems.and.a.given.switch..us,.the.VL.concept.of.virtual.communication.

channels.has.the.advantage.of.statically.dening.the.ows,.which.enter.the.network,.and.associating.

some.performance.properties.to.each.ow..Each.VL.can.be.statically.mapped.on.the.network.of.inter-

connected

.AFDX.switches..Transmitting.an.Ethernet.frame.from.one.end.system.to.another.is.based.

on.a.VL.identier,.which.is.used.for.the.deterministic.routing.of.each.VL.(the.switch.forwarding.tables.

are.statically.dened.aer.allocation.of.all.VL.on.the.AFDX.network.architecture)..Each.VL.denes.a.

logical.unidirectional.connection.from.one.source.end.system.to.one.or.more.destination.end.systems..

For.example,.Figure.24.8.illustrates.dierent.kinds.of.VL:.vx.is.a.unicast.VL.with.path.{e3−S3−S4−e8},.

while.v6.is.a.multicast.VL.with.paths.{e1−S1−S2−e7}.and.{e1−S1−S4−e8}.

A

.VL.denition.includes.the.bandwidth.allocation.gap.(BAG).value,.the.minimum.frame.size.(S

min

),.

and.the.maximum.frame.size.(S

max

)..e.BAG.is.the.minimum.delay.between.two.consecutive.frames.

of.the.associated.VL.(which.actually.denes.a.VL.as.a.sporadic.ow)..BAG.and.S

max

.values.guarantee.an.

allocated.bandwidth.for.each.VL..Moreover,.a.jitter.value.is.associated.to.each.VL.to.establish.an.upper.

bound.on.the.maximum.admissible.jitter.aer.multiplexing.dierent.regulated.VL.ows.

24.6.4 Virtual Link Properties

From.the.avionics.systems.designer’s.point.of.view,.classic.ARINC.429.buses.have.many.interesting.

features..For.example,.the.single-emitter.assumption.implies.a.dedicated.link.oered.to.the.emitter,.and.

thus.guaranteed.access.to.the.bus,.guaranteed.bandwidth,.and.high.determinism..Moreover,.the.com-

munication

.paradigm.used.by.many.avionic.applications.is.derived.from.the.ARINC.429’s.properties.

behavior,.which.has.been.generalized.on.IMA.through.APEX.port.paradigm.[ARI97]..is.explains.why.

the.VL.concept.is.of.importance.in.the.denition.of.AFDX;.it.allows.direct.replacement.of.ARINC.429.

buses,.on.a.deterministic.ARINC.664.network.

24.6.4.1

VL Bandwidth Guarantee

Each

.avionic.function.denes.its.VL.bandwidth.requirements.in.the.form.of.two.parameters:.the.BAG.

and.the.maximum.frame.size.(S

max

)..When.the.VL.has.no.jitter,.the.BAG.represents.the.minimum.

interval.between.the.rst.bits.of.two.consecutive.frames..us,.the.bandwidth.oered.to.a.VL.is.the.one.

obtained.when.emitting.a.maximum-sized.frame.every.BAG,.the.latter.being.specied.by.an.integer.(k),.to.

give.(create).a.2

k

.interval.(in.milliseconds)..e.minimal.BAG.is.thus.1.ms.for.k.=.0,.and.when.combined.

with.standard.maximum.Ethernet.frames,.the.maximum.bandwidth.oered.attributed.to.a.single.VL.

can.be.up.to.12.Mbps.

e

.network.integrator.collates.all.the.VL.bandwidth.requirements.and.veries.that.the.sum.of.VL.

bandwidths.on.any.physical.link.of.the.full-duplex.switched.Ethernet.network.does.not.exceed.the.

v6, v8

v7, v9

vx, v1

v2, v3

v1, v3

v6, v7

v6, v8, v 9

vx, v2

v6, v8, v9

vx, v6, v7

v2, v5

v1, v3, v4

v5

S3

e5

e6

S1

S4

S5

S2

e7

e8

e9

e10

e

1

e2

e3

e4

v4

FIGURE 24.8 Example.of.AFDX.VLs.conguration.

© 2011 by Taylor and Francis Group, LLC

Embedded Networks in Civilian Aircraft Avionics Systems 24-11

100.Mbps.capacity..Moreover,.the.network.integrator.is.responsible.for.VL.placement:.A.multipath.

VL.(a.tree.originating.from.the.emitter).has.to.be.statically.allocated.on.the.network’s.physical.topology.

and.the.path.can.be.chosen.from.among.several.possibilities.

One

.must.note.that.guaranteeing.bandwidth.on.the.network.requires.that.all.VLs.remain.compliant.

with.their.specied.BAG.and.S

max

.parameters;.otherwise,.the.sum.of.some.VL.bandwidths.could.possi-

bly

.exceed.the.100.Mbps.capacity..For.this.reason,.every.VL.is.shaped.inside.the.emitter.end.system,.and.

all.incoming.VLs.are.also.controlled.by.policers.at.the.switch.level;.frames.exceeding.the.VL’s.contract.

are.deleted.by.the.switches.(leaky.bucket.algorithm).as.represented.in.Figure.24.9.

24.6.4.2

VL Latency Guarantee

e

.communication.latency.of.an.ARINC.429.data.bus.is.very.easy.to.measure..It.is.simply.the.time.

required.to.emit.data.plus.a.negligible.propagation.time;.it.is.absolutely.deterministic.

e

.picture.is.completely.dierent.for.a.VL.on.an.AFDX.network..Obviously,.the.latency.of.a.frame.

cannot.be.predicted.as.it.depends.on.whether.or.not.the.frame.will.be.delayed.by.other.frames.sharing.a.

section.of.its.path..us,.a.strong.form.of.determinism.cannot.be.obtained;.a.weaker.form.of.determin-

ism

.is.proposed,.it.is.based.on.VL.end-to-end.latency.upper.bounding.methods..VLs.competing.for.a.

given.switch.output.port.generate.contentions.in.the.output.port.queue.and.can.be.delayed.depending.

on.the.number.of.conuent.VLs.and.their.characteristics.(maximum.frame.size.for.example).

Of

.course,.end-to-end.latencies.have.to.be.compared.to.the.real-time.constraints.of.avionics.commu-

nications,

.but.in.reality,.these.constraints.are.very.dierent.from.one.avionics.function.to.another..us,.

in.the.early.prototype.specications,.a.maximum.latency.of.1.ms.per.switch.crossing.was.integrated.into.

the.switch.specication..When.four.or.ve.switches.are.crossed,.the.maximum.obtained.latency.is.com-

parable

.with.the.highest.“freshness”.required.for.some.critical.data..At.100.Mbps,.1.ms.of.continuous.

emission.of.minimum-sized.frames.represents.nearly.150.frames.exiting.from.an.output.port’s.queue..

Of.course,.the.physical.size.of.the.switches’.queues.is.the.actual.constraint:.overowing.this.queue.

capacity.necessarily.implies.lost.frames.

24.6.4.3

VL Jitter Issues

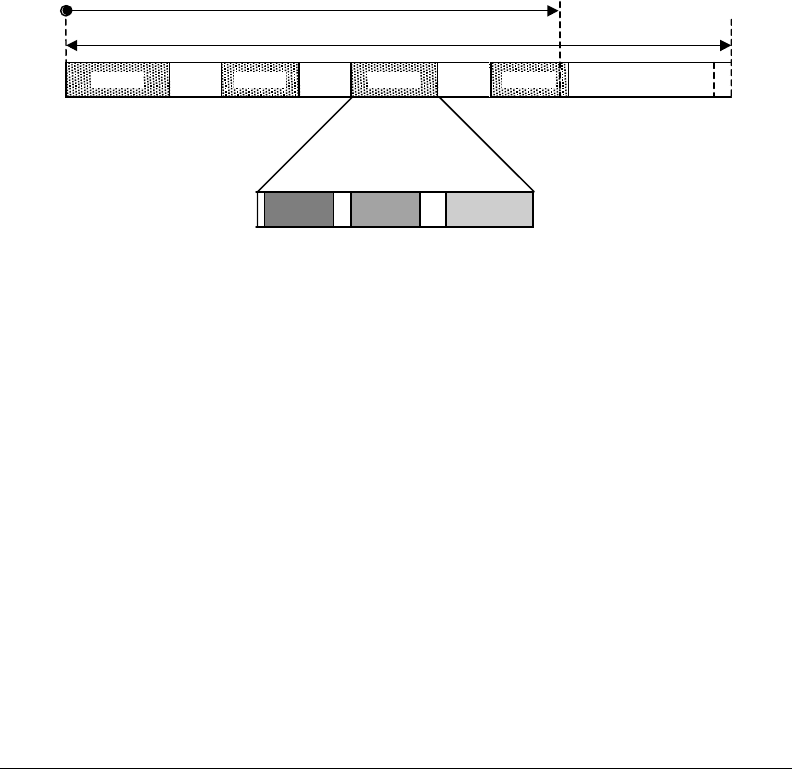

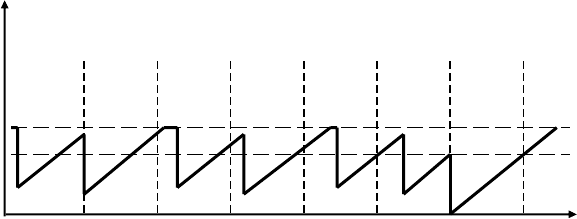

Jitter

.is.the.third.parameter.of.a.VL,.after.the.BAG.and.S

max

..As.the.AFDX.definition.in.the.ARINC.

664.standard.states,.jitter.is.considered.null.at.the.output.of.the.end.system.shapers.applied.to.each.

VL..Since.the.VLs.are.multiplexed.in.the.end.system.just.after.having.been.shaped,.as.represented.

in.Figure.24.10,.jitter.is.non-null.at.the.output.of.the.multiplexer.and.is.limited.by.two.bounds:.the.

first.one.comes.from.the.calculation.of.the.multiplexer’s.latency.and.the.second.is.an.absolute.value.

of.500.μs.

is

.value.has.been.chosen.as.half.the.minimal.BAG.in.order.to.avoid.burst.occurrences.where.a.

frame.pertaining.to.some.VLs.would.be.overtaken.by.a.following.frame.of.the.same.VL..Of.course,.

avoiding.this.problem.in.end.systems.does.not.prevent.it.from.occurring.later.down.the.network.

t

1

1 + Jit/BAG

Credit

BAGBAGBAGBAGBAGBAGBAG

FIGURE 24.9 AFDX.VLs.shaping.and.policing.

© 2011 by Taylor and Francis Group, LLC