Nof S.Y. Springer Handbook of Automation

Подождите немного. Документ загружается.

Design Automation for Microelectronics 38.3 New Trends and Conclusion 665

38.3 New Trends and Conclusion

Due to technology scaling, nanoscale process tech-

nologies are fraught with nonidealities such as process

variations, noise, soft errors, leakage, and others.

Designers are also facing unprecedented design com-

plexity due to these issues. CAD techniques need new

innovations to continue to deliver high-quality IC de-

signs in a short period of time. Under this vision, we

introduce some new trends in CAD below.

Design for Manufacturing (DFM)

Nanometer IC designs are deeply challenged by man-

ufacturing variations. The industry is currently using

193nm photolithography for fabrication of ICsin

130nm and down (to 32nm or even 22 nm). There-

fore, it is challenging for the photolithography process

to precisely control the manufacturing quality of the

circuit features. There are other manufacturing/process

challenges, such as topography variations, random de-

fects due to missing/extra material, via void/failure, etc.

DFM will take the manufacturing issues into the de-

sign process to improve circuit manufacturability and

yield. The essential task in DFM is the development

of resolution enhancement techniques (RETs), such as

tools for optical proximity correction (OPC) and phase-

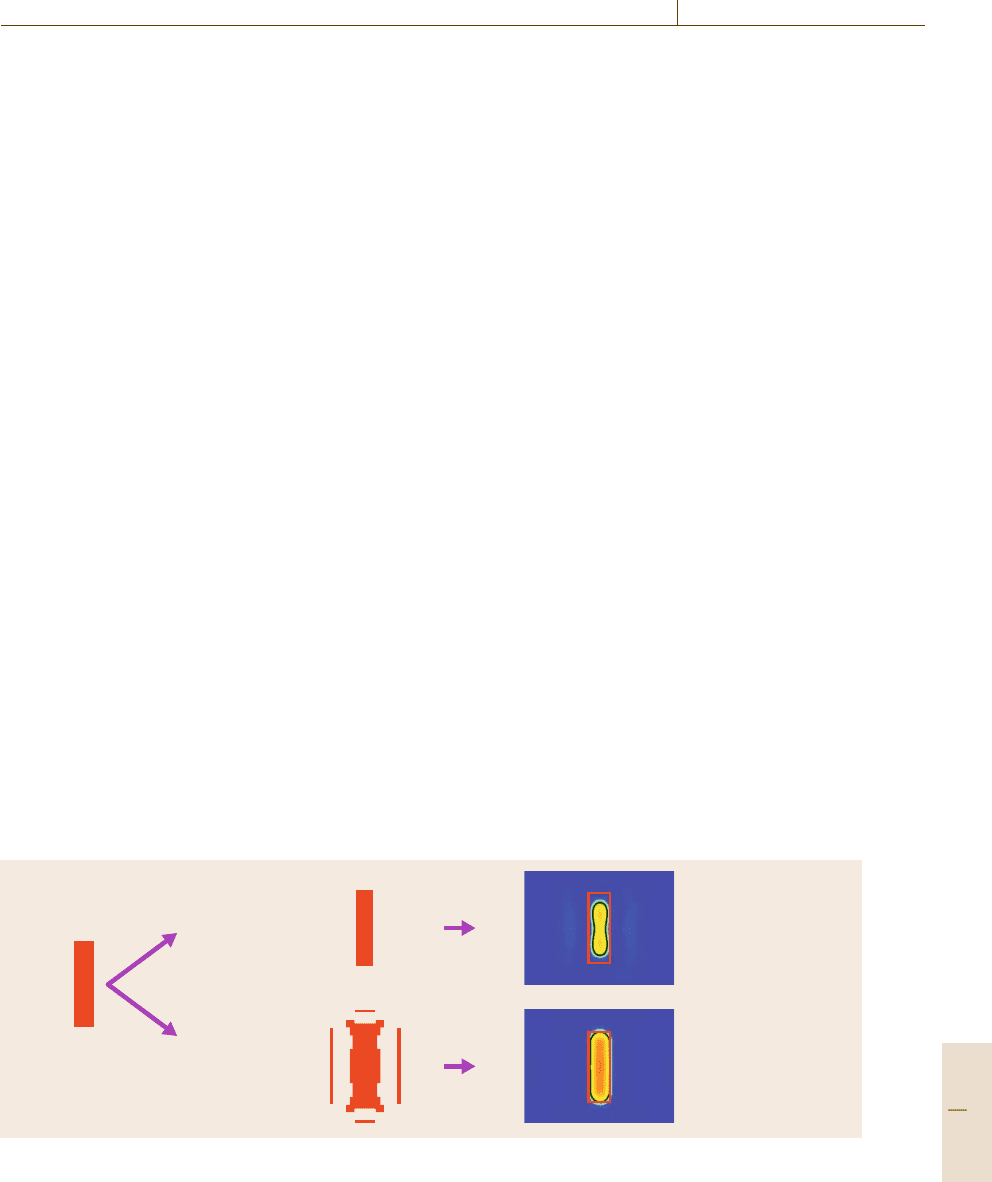

shift mask (PSM) [38.81–85]. As an example, Fig.38.9

shows the OPC optimization for a layout, which ma-

nipulates mask geometry to compensate for image

distortions. Another area is to develop efficient engi-

neering change order (ECO) tools, so that when some

changes need to be made, as few layers as possible need

to be modified [38.86,87]. Meanwhile, post-silicon de-

bug and repair techniques are gaining importance as

well [38.88,89].

Silicon image

w/o OPC

Conventional

(no OPC)

Silicon image

with OPC

OPC

layout

Original

layout

Fig. 38.9 An illustration of optical proximity correction (after [38.81])

Statistical Static Timing Analysis (SSTA)

Large variation in process parameters makes worst-

case design too expensive in terms of power and

delay. Meanwhile, nominal case design will result in

a loss in yield as performance specifications may not

be met for a large percentage of chips. SSTA is an

effortto specifically improve performance yieldto com-

bat manufacturing variations. SSTA treats the delay

of each gate as a random variable and propagates

gates’ probability density functions (PDFs) through

the circuit to create a PDF of the output delay ran-

dom variable. Spatial correlations among the circuit

components need to be considered. A vast amount

of research has been reported (e.g., [38.90–98]) in

the past 5 years. SSTA is critical to guide statisti-

cal design methodologies. An important application is

SSTA-driven placement and routing to improve perfor-

mance yield.

Design for Nanotechnology

Sustained exponential growth of complex electronic

systems will require new breakthroughs in fabrication

and assembly with controlled engineering of nanoscale

components. Bottom-up approaches, in which inte-

grated functional device structures are assembled from

chemically synthesized nanoscale building blocks (so-

called nanomaterials), such as carbon nanotubes,

nanowires, and other molecular electronic devices, have

the potential to revolutionize the fabrication of elec-

tronic systems. Nanoelectronic circuits always have

a certain percentage of defects as well as nanomaterial-

specific variations over and above process variations

introduced by lithography. Using simplified nanode-

Part D 38.3

666 Part D Automation Design: Theory and Methods for Integration

vice assumptions and traditional scaled design flows

will lead to suboptimal and impractical nanocircuit

designs and inaccurate system evaluation results. For

nanotechnology to fulfill its promise, there is a need

to understand and incorporate nano-specific design

techniques, such as nanosystems modeling, statistical

approaches, and fault-tolerant design, systematically

from devices all the way up to systems. Initial effort has

been made in this important area [38.99–107], but much

more research has to be done to enable the large inte-

gration capability of nanosystems. Chapter 53 provides

more information on micro and nano manipulation re-

lated to design of nanotechnology.

Design for 3-D ICs

One promising way to improve circuit performance,

logic density or power efficiency is to develop three-

dimensional integration, which increases the number of

active die layers and optimizesthe interconnect network

vertically [38.108–115]. Potentially, three-dimensional

(3-D) IC provides improved bit bandwidth with re-

duced wire length, delay, and power. There are different

bonding technologies for 3-D ICs, including die-to-die,

die-to-wafer, and wafer-to-wafer, and the two parties

can be bonded face-to-face or face-to-back. One dis-

advantage of the 3-D IC is its thermal penalty. The

3-D stacks will increase heat density, leading to de-

graded chip performance and reliability if not handled

properly.

Design for Reliability

Besides fabrication defects, soft errors and aging errors

have emerged as the new sources of circuit unre-

liability for nanometer circuit designs. A soft error

occurs when a cosmic particle, such as a neutron,

strikes a portion of the circuit, upsetting the state

of a bit. Aging errors are due to the wearing effect

of an operating circuit. As device dimensions scale

down faster than the supply voltage [38.9], the re-

sulting high electric fields combined with temperature

stresses lead to device aging and hence failure. Espe-

cially, transistor aging due to negative-bias temperature

instability (NBTI) has become the determining factor

in circuit lifetime. Reliability analysis and error miti-

gation techniques under soft errors, aging effects, and

process variations have been proposed [38.116–126].

Ultimately, chip reliability would need to become a crit-

ical design metric incorporated into mainstream CAD

methodologies.

Design with Parallel Computing

An important way to deal with design complexity is

to take advantage of the latest advances of parallel

computing with multicore computer systems so that

computation can be carried out in parallel for accel-

eration. Although there are some studies on parallel

CAD algorithms (e.g., [38.127,128]), much more work

is needed to come up with parallel CAD algorithms to

improve design productivity.

Design for Network on Chip (NoC)

The increasing complexity and heterogeneity of fu-

ture SoCs (system-on-a-chip) prompt significant sys-

tem scalability challenge using conventional on-chip

communication schemes, such as the point-to-point

(P2P) andbus-basedcommunication architectures.NoC

emerged recently as a promising solution for the fu-

ture [38.129–133]. In a NoC system, modules such as

processor cores, memories, and other IP blocks ex-

change data using a network on a single chip. NoC

communication is constructed from a network of data

links interconnected by switches (or routers) such that

messages can be relayed from any source module to any

destination module. Because all links in the NoC can

operate simultaneously on different data packets, a high

level of parallelism can be achieved with a great scaling

capability. However, many challenging research prob-

lems remain to be solved for NoC, from the design of

the physical link through the network-level structure, all

the way up to the system architecture and application

software.

Electronic design automation or computer-aided de-

sign as an engineering field has been evolving through

the past several decades since its birth shortly after the

invention of integrated circuits. On the one hand, it

has become a mature engineering area to provide de-

sign tools for the electronic semiconductor industry. On

the other hand, many challenges and unsolved problems

still remain in this exciting field as on-chip device den-

sity continues to scale. As long as electronic circuits

are impacting our daily lives, design automation will

continue to diversify and evolve to further facilitate the

growth of the semiconductor industry and revolutionize

our future.

Part D 38.3

Design Automation for Microelectronics References 667

References

38.1 F. Vahid, T. Givargis: Embedded System Design:

A Unified Hardware/Software Introduction (Wiley,

New York 2002)

38.2 G. De Micheli: Synthesis and Optimization of Digital

Circuits (McGraw-Hill, Upper Saddle River 1994)

38.3 N. Weste, D. Harris: CMOS VLSI Design: A Circuits

and Systems Perspective, 3rd edn. (Addison Wesley,

Indianapolis 2004)

38.4 K. Keutzer, S. Malik, R. Newton, J. Rabaey,

A. Sangiovanni-Vincentelli: System level design:

orthogonalization of concerns and platform-based

design, IEEE Trans. CAD Integr. Circuits Syst. 19(12),

1523–1543 (2000)

38.5 A. Sangiovanni-Vincentelli, G. Martin: A vision for

embedded systems: platform-based design and

software methodology, IEEE Des. Test Comput.

18(6), 23–33 (2001)

38.6 G. Martin, H. Chang: Winning the SoC Revolution:

Experiences in Real Design (Kluwer, Dordrecht 2003)

38.7 I. Kuon, J. Rose: Measuring the gap between FPGAs

and ASICs, IEEE Trans. CAD Integr. Circuits Syst. 26(2),

203–215 (2007)

38.8 D. Orecchio: FPGA explosion will test EDA, Electronic

Design Update (2007), http://electronicdesign.com/

Articles/ArticleID/15910/15910.html. Accessed 18 June

2007

38.9 L. Wilson: International Technology Roadmap for

Semiconductors. http://www.itrs.net/ (2008)

38.10 G.G.E. Gielen, R.A. Rutenbar: Computer-aided

design of analog and mixed-signal integrated cir-

cuits, Proc. IEEE 88(12), 1825–1854 (2000)

38.11 P. Wambacq, G. Vandersteen, J. Phillips, J. Roy-

chowdhury, W. Eberle, B. Yang, D. Long, A. Demir:

CAD for RF circuits, Proc. Des. Autom. Test Eur. (2001)

38.12 L. Scheffer, L. Lavagno, G. Martin (eds.): Electronic

Design Automation for Integrated Circuits Hand-

book (CRC, Boca Raton 2006)

38.13 D. Jansen (ed.): The Electronic Design Automation

Handbook (Springer, Norwell 2003)

38.14 C.J. Alpert, D.P. Mehta, S.S. Sapatnekar (eds.): The

Handbook of Algorithms for VLSI Physical Design

Automation (CRC, Boca Raton 2007)

38.15 S. Kumar, J. Aylor, B.W. Johnson, W.A. Wulf: The

Codesign of Embedded Systems: A Unified Hard-

ware/Software Representation (Kluwer, Dordrecht

1996)

38.16 Y.T. Li, S. Malik: Performance Analysis of Real-Time

Embedded Software (Kluwer, Dordrecht 1999)

38.17 G. De Micheli, R. Ernst, W. Wolf (eds.): Readings in

Hardware/Software Codesign (Morgan Kaufmann,

New York 2001)

38.18 F. Balarin, H. Hsieh, L. Lavagno, C. Passerone,

A. Pinto, A. Sangiovanni-Vincentelli, Y. Watan-

abe, G. Yang: Metropolis: a design environ-

ment for heterogeneous systems. In: Multi-

processor Systems-on-Chips, ed. by A. Jerraya,

W. Wolf (Morgan Kaufmann, New York 2004),

Chap. 16

38.19 R.P. Dick, N.K. Jha: MOCSYN: multi-objective core-

based single-chip system synthesis, Proc. IEEE Des.

Autom. Test Eur. (1999)

38.20 P. Petrov, A. Orailoglu: Tag compression for low

power in dynamically customizable embedded

processors, IEEE Trans. CAD Integr. Circuits Syst.

23(7), 1031–1047 (2004)

38.21 S.P. Levitan, R.R. Hoare: Structural Level SoC Design

Course (The Technology Collaborative, Pittsburgh

1991)

38.22 B. Bailey, G. Martin, A. Piziali: ESL Design and Ver-

ification: A Prescription for Electronic System Level

Methodology (Elsevier, Amsterdam 2007)

38.23 K. Wakabayashi, T. Okamoto: C-based SoC design

flow and EDA tools: an ASIC and system vendor per-

spective, IEEE Trans. CAD Integr. Circuits Syst. 19(12),

1507–1522 (2000)

38.24 J.P. Elliott: Understanding Behavioral Synthesis:

A Practical Guide to High-Level Design (Kluwer,

Dordrecht 1999)

38.25 D. Gajski, N. Dutt, A. Wu: High-Level Synthesis:

Introduction to Chip and System Design (Kluwer,

Dordrecht 1992)

38.26 A. Raghunathan, N.K. Jha, S. Dey: High-Level

Power Analysis and Optimization (Kluwer, Dor-

drecht 1998)

38.27 R. Camposano, W. Wolf: High-Level VLSI Synthesis

(Springer, New York 2001)

38.28 J. Chang, M. Pedram: Power Optimization and

Synthesis at Behavioral and System Levels Using

Formal Methods (Kluwer, Boston 1999)

38.29 A. Chandrakasan, M. Potkonjak, J. Rabaey,

R. Brodersen: Hyper-LP: a system for power

minimization using architectural transformations.

In: TheBestofICCAD,20YearsofExcellence

in Computer-Aided Design, ed. by A. Kuehlman

(Kluwer, Boston 2003)

38.30 S. Gupta, N.D. Dutt, R. Gupta, A. Nicolau: SPARK:

A Parallelizing Approach to the High-Level Syn-

thesis of Digital Circuits (Kluwer, Norwell 2004)

38.31 S. Memik, E. Bozorgzadeh, R. Kastner, M. Sar-

rafzadeh: A scheduling algorithm for optimization

and early planning in high-level synthesis, ACM

Trans. Des. Autom. Electron. Syst. 10(1), 33–57

(2005)

38.32 J. Jeon, D. Kim, D. Shin, K. Choi: High-level syn-

thesis under multi-cycle interconnect delay, Proc.

AsiaSouthPac.Des.Autom.Conf.(2001)

38.33 P. Brisk, A. Verma, P. Ienne: Optimal polynomial-

time interprocedural register allocation for high-

level synthesis and ASIP design, Proc. Int. Conf.

Comput.-Aided Des. (2007)

Part D 38

668 Part D Automation Design: Theory and Methods for Integration

38.34 D. Chen, J. Cong, Y. Fan, G. Han, W. Jiang, Z. Zhang:

xPilot: a platform-based behavioral synthesis sys-

tem, Proc. SRC Techcon Conf. (2005)

38.35 F. Wang, X. Wu, Y. Xie: Variability-driven mod-

ule selection with joint design time optimization

and post-silicon tuning, Proc. Asia South Pac. Des.

Autom. Conf. (2008)

38.36 J. Cong, Y. Ding: FlowMap: an optimal technol-

ogy mapping algorithm for delay optimization in

lookup-table based FPGA designs, IEEE Trans. CAD

Integr. Circuits Syst. 13(1), 1–12 (1994)

38.37 T.J. Callahan, P. Chong, A. DeHon, J. Wawrzynek:

Fast module mapping and placement for datapaths

in FPGAs, Proc. Int. Symp. FPGAs (1998)

38.38 R. Brayton, G. Hachtel, C. McMullen, A. Sangio-

vanni-Vincentelli: Logic Minimization Algorithms

for VLSI Synthesis (Kluwer, Boston 1984)

38.39 E.Sentovich,K.Singh,L.Lavagno,C.Moon,R.Mur-

gai, A. Saldanha, H. Savoj, P. Stephan, R. Brayton,

A. Sangiovanni-Vincentelli: SIS: A System for Se-

quential Circuit Synthesis, Memo. UCB/ERL M92/41

(Univ. of California, Berkeley 1992)

38.40 R. Bryant: Graph-Based Algorithms for Boolean

Function Manipulation, IEEE Trans. Comput. 35(8),

677–691 (1986)

38.41 J. Marques Silva, K. Sakallah: Boolean satisfiability

in electronic design automation, Proc. Des. Autom.

Conf. (2000)

38.42 K. Keutzer: DAGON: technology mapping and lo-

cal optimization, Proc. IEEE/ACM Des. Autom. Conf.

(1987)

38.43 Berkeley ABC: A system for sequential synthesis

and verification. http://www.eecs.berkeley.edu/

˜alanmi/abc/ (2005)

38.44 C.-W. Kang, A. Iranli, M. Pedram: A synthesis ap-

proach for coarse-grained, antifuse-based FPGAs,

IEEE Trans. CAD Integr. Circuits Syst. 26(9), 1564–1575

(2007)

38.45 A.Ling,D.Singh,S.Brown:FPGAPLBarchitecture

evaluation and area optimization techniques us-

ing boolean satisfiability, IEEE Trans. CAD Integr.

Circuits Syst. 26(7), 1196 (2007)

38.46 A.K. Singh, M. Mani, R. Puri, M. Orshansky: Gain-

based technology mapping for minimum runtime

leakage under input vector uncertainty, Proc. Des.

Autom. Conf. (2006)

38.47 L. Cheng, D. Chen, D.F. Wong, M. Hutton, J. Govig:

Timing constraint-driven technology mapping for

FPGAs considering false paths and multi-clock do-

mains, Proc. Int. Conf. Comput.-Aided Des. (2007)

38.48 N. Sherwani: Algorithms for VLSI Physical Design

Automation (Kluwer, Dordrecht 1999)

38.49 C.M. Fiduccia, R.M. Matheysses: A linear-time

heuristic for improving network partitions, Proc.

IEEE/ACM Des. Autom. Conf. (1982) pp. 175–181

38.50 G. Karypis, R. Aggarwal, V. Kumar, S. Shekhar: Mul-

tilevel hypergraph partitioning: application in VLSI

domain, Proc. IEEE/ACM Des. Autom. Conf. (1997)

38.51 Y.C. Wei, C.K. Cheng: Ratio cut partitioning for hi-

erarchical designs, IEEE Trans. CAD Integr. Circuits

Syst. 10, 911–921 (1991)

38.52 H. Liu, D.F. Wong: Network-flow-based multi-

way partitioning with area and pin constraints,

IEEE Trans. CAD Integr. Circuits Syst. 17(1), 50–59

(1998)

38.53 L. Stockmeyer: Optimal orientation of cells in slic-

ing floorplan designs, Inf. Control 57(2–3), 91–101

(1984)

38.54 D.F. Wong, C.L. Liu: A new algorithm for floorplan

design, Proc. Des. Autom. Conf. (1986)

38.55 P. Sarkar, C.K. Koh: Routability-driven repeater

block planning for interconnect-centric floorplan-

ning, IEEE Trans. CAD Integr. Circuits Syst. 20(5),

660–671 (2001)

38.56 M. Healy, M. Vittes, M. Ekpanyapong, C. Balla-

puram, S.K. Lim, H. Lee, G. Loh: Multi-objective

microarchitectural floorplanning for 2-D and 3-D

ICs, IEEE Trans. CAD Integr. Circuits Syst. 26(1), 38–52

(2007)

38.57 W. Sun, C. Sechen: Efficient and effective place-

ment for very large circuits, IEEE Trans. CAD Integr.

Circuits Syst. 14(3), 349–359 (1995)

38.58 V. Betz, J. Rose, A. Marquardt: Architecture and

CAD for Deep-Submicron FPGAs (Kluwer, Dordrecht

1999)

38.59 A. Caldwell, A.B. Kahng, I. Markov: Can recur-

sive bisection produce routable placements?, Proc.

IEEE/ACM Des. Autom. Conf. (2000) pp. 477–482

38.60 U. Brenner, A. Rohe: An effective congestion-

driven placement framework, Proc. Int. Symp.

Phys. Des. (2002)

38.61 T.Chan,J.Cong,T.Kong,J.Shinnerl:Multilevel

circuit placement. In: Multilevel Optimization in

VLSICAD, ed. by J. Cong, J. Shinnerl (Kluwer, Boston

2003), Chap. 4

38.62 C. Chu, N. Viswanathan: FastPlace: efficient ana-

lytical placement using cell shifting, iterative local

refinement, and a hybrid net model, Proc. Int.

Symp. Phys. Des. (2004) pp. 26–33

38.63 Z. Xiu, J. Ma, S. Fowler, R. Rutenbar: Large-scale

placement by grid warping, Proc. Des. Autom. Conf.

(2004)

38.64 T. Taghavi, X. Yang, B. Choi, M. Wang,

M. Sarrafzadeh: Dragon2006: blockage-aware

congestion-controlling mixed-size placer, Proc.

Int. Symp. Phys. Des. (2006)

38.65 T.Chen,Z.Jiang,T.Hsu,H.Chen,Y.Chang:NTU-

place2: a hybrid placer using partitioning and

analytical techniques, Proc. Int. Symp. Phys. Des.

(2006)

38.66 A.B. Kahng, S. Reda, Q. Wang: APlace: a general an-

alytic placement framework, Proc. Int. Symp. Phys.

Des. (2005)

38.67 C.Y. Lee: An algorithm for path connections and

its applications, Proc. IRE Trans. Electron. Comput.

(1961)

Part D 38

Design Automation for Microelectronics References 669

38.68 D.W. Hightower: A solution to the line routing

problem on a continuous plane, Proc. Des. Autom.

Workshop (1969)

38.69 L. McMurchie, C. Ebeling: PathFinder: a negoti-

ation-based performance-driven router for FPGAs,

Proc. Int. Symp. FPGAs (1995)

38.70 C. Chu, Y.C. Wong: FLUTE: fast lookup table based

rectilinear steiner minimal tree algorithm for VLSI

design, IEEE Trans. CAD Integr. Circuits Syst. 27(1),

70–83 (2008)

38.71 J. Hu, S. Sapatnekar: A survey on multi-net global

routing for integrated circuits, Integration: VLSI J.

31, 1–49 (2001)

38.72 P. McGeer, R. Brayton: Efficient algorithms for com-

puting the longest viable path in a combinational

network, Proc. Des. Autom. Conf. (1989)

38.73 P. Ashar, S. Dey, S. Malik: Exploiting multicycle false

paths in the performance optimization of sequen-

tial logic circuits, IEEE Trans. CAD Integr. Circuits

Syst. 14(9), 1067–1075 (1995)

38.74 S.Zhou,B.Yao,H.Chen,Y.Zhu,M.Hut-

ton, T. Collins, S. Srinivasan, N. Chou, P. Suaris,

C.K. Cheng: Efficient timing analysis with known

false paths using biclique covering, IEEE Trans. CAD

Integr. Circuits Syst. 26(5), 959–969 (2006)

38.75 J. Mar: The application of TCAD in industry, Proc.

Int. Conf. Simul. Semiconduct. Process. Dev. (1996)

38.76 M. Pedram: Low power design methodologies and

techniques: an overview. http://atrak.usc.edu/

˜massoud/ (1999)

38.77 W. Nebel, J. Mermet (eds.): Low Power Design in

Deep Submicron Electronics (Springer, New York

1997)

38.78 K. Roy, S. Prasad: Low-Power CMOS VLSI Circuit

Design (Wiley, New York 2000)

38.79 M. Pedram, J.M. Rabaey: Power Aware Design

Methodologies (Springer, New York 2002)

38.80 R. Puri, L. Stok, J. Cohn, D. Kung, D. Pan,

D. Sylvester, A. Srivastava, S. Kulkarni: Pushing

ASIC performance in a power envelope, Proc. Des.

Autom. Conf. (2003)

38.81 L. Huang, D.F. Wong: Optical proximity correction

(OPC): friendly maze routing, Proc. Des. Autom.

Conf. (2004)

38.82 P. Yu, S.X. Shi, D.Z. Pan: True process vari-

ation aware optical proximity correction with

variational lithography modeling and model cali-

bration, J. Micro/Nanolith. MEMS MOEMS 6, 031004

(2007)

38.83 P. Berman, A.B. Kahng, D. Vidhani, H. Wang, A. Ze-

likovsky: Optimal phase conflict removal for layout

of dark field alternating phase shifting masks,

Proc. Int. Symp. Phys. Des. (1999)

38.84 L.W. Liebmann, G.A. Northrop, J. Culp, M.A. Lavin:

Layout optimization at the pinnacle of optical

lithography, Proc. SPIE Des. Process Integr. Elec-

tron. Manuf. (2003)

38.85 F.M. Schellenberg, L. Capodieci: Impact of RET on

physical layouts, Proc. Int. Symp. Phys. Des. (2001)

38.86 Y.M. Kuo, Y.T. Chang, S.C. Chang, M. Marek-

Sadowska: Engineering change using spare cells

with constant insertion, Proc. Int. Conf. Comput.-

Aided Des. (2007)

38.87 S. Ghiasi: Incremental component implementation

selection: enabling ECO in compositional system

synthesis, Proc. Int. Conf. Comput.-Aided Des.

(2007)

38.88 A. Krstic, L.C. Wang, K.T. Cheng, T.M. Mak:

Diagnosis-based post-silicon timing validation

using statistical tools and methodologies, Proc. Int.

Test Conf. (2003)

38.89 K.H. Chang, I. Markov, V. Bertacco: Automating

post-silicon debugging and repair, Proc. Int. Conf.

Comput.-Aided Des. (2007)

38.90 S. Sapatnekar: Timing (Springer, New York 2004)

38.91 A. Srivastava, D. Sylvester, D. Blaauw: Statistical

Analysis and Optimization for VLSI: Timing and

Power (Springer, New York 2005)

38.92 V. Mehrotra, S. Sam, D. Boning, A. Chandrakasan,

R. Vallishayee, S. Nassif: A methodology for

modeling the effects of systematic within-die

interconnect and device variation on circuit per-

formance, Proc. Des. Autom. Conf. (2000)

38.93 M. Guthaus, N. Venkateswaran, C. Visweswariah,

V. Zolotov: Gate sizing using incremental param-

eterized statistical timing analysis, Proc. Int. Conf.

Comput.-Aided Des. (2005)

38.94 J. Le, X. Li, L.T. Pileggi: STAC: statistical timing anal-

ysis with correlation, Proc. IEEE/ACM Des. Autom.

Conf. (2004)

38.95 M. Orshansky, A. Bandyopadhyay: Fast statistical

timing analysis handling arbitrary delay correla-

tions, Proc. IEEE/ACM Des. Autom. Conf. (2004)

38.96 V. Khandelwal, A. Srivastava: A general framework

for accurate statistical timing analysis consider-

ing correlations, Proc. IEEE/ACM Des. Autom. Conf.

(2005)

38.97 A. Ramalingam, A.K. Singh, S.R. Nassif, M. Orshan-

sky, D.Z. Pan: Accurate waveform modeling using

singular value decomposition with applications to

timing analysis, Proc. Des. Autom. Conf. (2007)

38.98 J. Xiong, V. Zolotov, L. He: Robust extraction of spa-

tial correlation, Proc. Int. Symp. Phys. Des. (2006)

38.99 J. Heath, P. Kuekes, G. Snider, S. Williams: A defect-

tolerant computer architecture: opportunities for

nanotechnology, Science 280, 1716–1721 (1998)

38.100 A. DeHon, H. Naeimi: Seven strategies for tolerating

highly defective fabrication, IEEE Des. Test Comput.

22(4), 306–315 (2005)

38.101 J.Deng,N.Patil,K.Ryu,A.Badmaev,C.Zhou,S.Mi-

tra, H.S. Wong: Carbon nanotube transistor circuits:

circuit-level performance benchmarking and de-

sign options for living with imperfections, Proc.

IEEE Int. Solid-State Circuits Conf. (2007)

Part D 38

670 Part D Automation Design: Theory and Methods for Integration

38.102 S.C. Goldstein, M. Budiu: NanoFabric: spatial com-

puting using molecular electronics, Proc. Int. Symp.

Comput. Archit. (2001) pp. 178–189

38.103 D.B. Strukov, K.K. Likharev: A reconfigurable archi-

tecture for hybrid CMOS/nanodevice circuits, Proc.

Int. Symp. FPGAs (2006)

38.104 A. Raychowdhury, A. Keshavarzi, J. Kurtin, V. De,

K. Roy: Analysis of carbon nanotube field effect

transistors for high performance digital logic –

modeling and DC simulations, IEEE Trans. Electron.

Dev. 53(11) (2006)

38.105 W. Zhang, N.K. Jha, L. Shang: NATURE: a CMOS/nano-

tube hybrid reconfigurable architecture, Proc. Des.

Autom. Conf. (2006)

38.106 M. Ben Jamaa, K. Moselund, D. Atienza, D. Bouvet,

A. Ionescu, Y. Leblebici, G. De Micheli: Fault-

tolerant multi-level logic decoder for nanoscale

crossbar memory arrays, Proc. Int. Conf. Comput.-

Aided Des. (2007)

38.107 A. Nieuwoudt, M. Mondal, Y. Massoud: Predicting

the performance and reliability of carbon nano-

tube bundles for on-chip interconnect, Proc. Asian

SouthPac.Des.Autom.Conf.(2007)

38.108 C. Ababei, P. Maidee, K. Bazargan: Explor-

ing potential benefits of 3-D FPGA integration,

Proc. Field Programmable Logic and Applica-

tion, Vol. 3203 (Springer, Berlin Heidelberg 2004)

pp. 874–880

38.109 K. Banerjee, S.J. Souri, P. Kapur, K.C. Saraswat:

3-D ICs: a novel chip design for improving

deep-submicrometer interconnect performance

and systems-on-chip integration, Proc. IEEE 89(5),

602–633 (2001)

38.110 M. Lin, A. El Gamal, Y.C. Lu, S. Wong: Performance

benefits of monolithically stacked 3-D-FPGA, Proc.

Int. Symp. FPGAs (2006)

38.111 W.R. Davis, J. Wilson, S. Mick, J. Xu, H. Hua,

C. Mineo, A.M. Sule, M. Steer, P.D. Franzon: De-

mystifying 3-D ICs: the pros and cons of going

vertical, IEEE Des. Test Comput. 22(6), 498–510

(2005)

38.112 C. Dong, D. Chen, S. Haruehanroengra, W. Wang:

3-D nFPGA: a reconfigurable architecture for 3-D

CMOS/nanomaterial hybrid digital circuits, IEEE

Trans. Circuits Syst. 54(11), 2489–2501 (2007)

38.113 Y. Xie, G. Loh, B. Black, K. Bernstein: Design space

exploration for 3-D architecture, ACM J. Emerg.

Technol. Comput. Syst. 2(2), 65–103 (2006)

38.114 J.Cong,Y.Ma,Y.Liu,E.Kursun,G.Reinman:3-D

architecture modeling and exploration, Proc. Int.

VLSI/ULSI Multilevel Interconnect. Conf. (2007)

38.115 M. Pathak, S.K. Lim: Thermal-aware steiner routing

for 3-D stacked ICs, Proc. Int. Conf. Comput.-Aided

Des. (2007)

38.116 M. Zhang, N.R. Shanbhag: Soft error-rate analysis

(SERA) methodology, IEEE Trans. CAD Integr. Circuits

Syst. 25(10), 2140–2155 (2006)

38.117 N. Miskov-Zivanov, D. Marculescu: MARS-C: mod-

eling and reduction of soft errors in combinational

circuits, Proc. Des. Autom. Conf. (2006)

38.118 R.R. Rao, K. Chopra, D. Blaauw, D. Sylvester: An ef-

ficient static algorithm for computing the soft error

rates of combinational circuits, Proc. Des. Autom.

Test Eur. (2006)

38.119 S. Mitra, N. Seifert, M. Zhang, Q. Shi, K.S. Kim:

Robust system design with built-in soft error re-

silience, IEEE Comput. 38(2), 43–52 (2005)

38.120 B. Paul, K. Kang, H. Kufluoglu, A. Alam, K. Roy:

Impact of NBTI on the temporal performance

degradation of digital circuits, IEEE Electron. Dev.

Lett.

26(8), 560–562 (2005)

38.121 D. Marculescu: Energy bounds for fault-tolerant

nanoscale designs, Proc. Des. Autom. Test Eur.

(2005)

38.122 W. Wang, S. Yang, S. Bhardwaj, R. Vattikonda,

S. Vrudhula, F. Liu, Y. Cao: The impact of NBTI on

the performance of combinational and sequential

circuits, Proc. IEEE/ACM Des. Autom. Conf. (2007)

38.123 W. Wu, J. Yang, S.X.D. Tan, S.L. Lu: Improving the

reliability of on-chip caches under process varia-

tions, Proc. Int. Conf. Comput. Des. (2007)

38.124 A. Mitev, D. Canesan, D. Shammgasundaram,

Y. Cao, J.M. Wang: A robust finite-point based

gate model considering process variations, Proc.

Int. Conf. Comput.-Aided Des. (2007)

38.125 S. Sarangi, B. Greskamp, J. Torrellas: A model for

timing errors in processors with parameter varia-

tion, Proc. Int. Symp. Qual. Electron. Des. (2007)

38.126 L. Cheng, Y. Lin, L. He, Y. Cao: Trace-based frame-

work for concurrent development of process and

FPGA architecture considering process variation

and reliability, Proc. Int. Symp. FPGAs (2008)

38.127 P. Banerjee: Parallel Algorithms for VLSI Computer-

Aided Design (Prentice-Hall, Englewood Cliffs 1994)

38.128 A. Ludwin, V. Betz, K. Padalia: High-quality,

deterministic parallel placement for FPGAs on com-

modity hardware, Proc. Int. Symp. FPGAs (2008)

38.129 G. De Micheli, L. Benini: Networks on Chips: Tech-

nology and Tools (Morgan Kaufmann, New York

2006)

38.130 A. Jantsch, H. Tenhunen (eds.): Networks on Chip

(Kluwer, Dordrecht 2003)

38.131 A.Hemani,A.Jantsch,S.Kumar,A.Postula,

J. Öberg, M. Millberg, D. Lindqvist: Network on

a chip: an architecture for billion transistor era,

Proc. IEEE NorChip Conf. (2000)

38.132 H.G. Lee, N. Chang, U.Y. Ogras, R. Marculescu:

On-chip communication architecture exploration:

a quantitative evaluation of point-to-point, bus,

and network-on-chip approaches, ACM Trans. Des.

Autom. Electron. Syst. 12(3) (2007)

38.133 H. Wang, L.S. Peh, S. Malik: Power-driven design

of router microarchitectures in on-chip networks,

Proc. Int. Symp. Microarchit. (2003)

Part D 38

671

Safety Warnin

39. Safety Warnings for Automation

Mark R. Lehto, Mary F. Lesch, William J. Horrey

Automated systems can provide tremendous ben-

efits to users; however, there are also potential

hazards that users must be aware of to safely op-

erate and interact with them. To address this need,

safety warnings are often provided to operators

and others who might be placed at risk by the

system. This chapter discusses some of the roles

safety warnings can play in automated systems,

from both the traditional perspective of warnings

as a form of hazard control and the perspective of

warnings as a form of automation. During this dis-

cussion, the chapter addresses some of the types

of warnings that might be used, along with issues

and challenges related to warning effectiveness.

Design recommendations and guidelines are also

presented.

39.1 Warning Roles...................................... 672

39.1.1 Warning as a Method

of Hazard Control ....................... 672

39.1.2 Warning as a Form of Automation 674

39.2 Types of Warnings ................................ 676

39.2.1 Static Versus Dynamic Warnings ... 676

39.2.2 Warning Sensory Modality ........... 678

39.3 Models of Warning Effectiveness............ 680

39.3.1 Warning Effectiveness Measures... 680

39.3.2 The Warning Compliance

Hypothesis ................................ 680

39.3.3 Information Quality .................... 681

39.3.4 Information Integration .............. 682

39.3.5 The Value

of Warning Information .............. 682

39.3.6 Team Decision Making ................ 683

39.3.7 Time Pressure and Stress ............. 683

39.4 Design Guidelines and Requirements ..... 684

39.4.1 Hazard Identification.................. 684

39.4.2 Legal Requirements.................... 685

39.4.3 Voluntary Standards ................... 687

39.4.4 Design Specifications .................. 687

39.5 Challenges and Emerging Trends ........... 690

References .................................................. 691

Automated systems have become increasingly preva-

lent in our society, in both our work and personal lives.

Automation involves the execution by a computer (or

machine) of a task that was formerly executedby human

operators [39.1]; for example, automation may be ap-

plied to a particular function in order to complete tasks

that humans cannot perform or do not want to perform,

to complete tasks that humans perform poorly or that

incur high workload demands, or to augment the capa-

bilities and performance of the human operator [39.2].

The potential benefits of automation include increased

productivity and quality, greater system safety and reli-

ability, and fewer human errors, injuries or occupational

illnesses. These benefits follow because some demand-

ing or dangerous tasks previously performed by the

operator can be completely eliminated through automa-

tion, and many others can be made easier. On the other

hand, automation can create new hazards and increase

the potential for catastrophic human errors [39.3]; for

example, in advanced manufacturing settings, the use

of robots and other forms of automation has reduced the

need to expose workers to potentially hazardous mater-

ials in welding, painting, and other operations, but in

turn has created a more complex set of maintenance,

repair, and setup tasks, for which human errors can

have seriousconsequences, such as damaging expensive

equipment, long periods of system downtime, produc-

tion of multiple runs of defective parts, and even injury

or death.

As implied by the above example, a key issue is that

automation increases the complexity of systems [39.4].

A second issue is that the introduction of automation

Part D 39

672 Part D Automation Design: Theory and Methods for Integration

into a system or task does not necessarily remove the

human operator from the task or system. Instead, the

role and responsibilities of the operator change. One

common result of automation is that operators may go

from active participants in a task to passive monitors of

the system function [39.5, 6]. This shift in roles from

active participation to passive monitoring can reduce

the operator’s situation awareness and ability to re-

spond appropriately to automation failures [39.7]. Part

of the problem is that the operator may have few op-

portunities to practise their skills because automation

failures tend to be rare events. Further complicating

the issue, system monitoring might be done from a re-

mote location using one or more displays that show the

status of many different subsystems. This also can re-

duce situation awareness, for many different reasons.

Another common problem is that workload may be

too low during routine operation of the automated sys-

tem, causing the operator to become complacent and

easily distracted. Furthermore, designers mayassign ad-

ditional unrelated tasks to operators to make up for the

reduced workload dueto automation. Thisagain can im-

pair situation awareness, as performing these unrelated

tasks can draw the operator’s attention away from the

automated system. Theneed to perform these additional

tasks can also contribute to a potentially disastrous in-

crease in workload in nonroutine situations in which the

operator has to take over control from the automated

system.

Many other aspects of automated systems can make

it difficult for operators and others to be adequately

aware of the hazards they face and how to respond to

them [39.4, 8]. To address this issue, safety warnings

are often employed in such systems. This chapter dis-

cusses some of the roles safety warnings can play in

automated systems, from both the traditional perspec-

tive of warnings as a form of hazard control and the

perspective of warnings asa formof automation.During

this discussion, the chapter addresses some of the types

of warnings that might be used. We also discuss is-

sues relatedto theeffectivenessof warnings andprovide

design recommendations and guidelines.

39.1 Warning Roles

The role of warnings in automated systems can be

viewed from two overlapping perspectives: (1) warn-

ings as a method of hazard control, and (2) warnings

as a form of automation.

39.1.1 Warning as a Method

of Hazard Control

Warnings are sometimes viewed as a method of last re-

sort to be relied upon when more fundamental solutions

to safetyproblems areinfeasible. This view corresponds

to the so-called hierarchy of hazard control, which can

be thought of as a simple model that prioritizes control

methods from mostto leasteffective. One version of this

model proposes the following sequence: (1) eliminate

the hazard, (2) contain or reduce the hazard, (3) con-

tain or control people, (4) train or educate people, and

(5) warn people [39.9]. The basic idea is that designers

should first consider design solutions that completely

eliminate the hazard. If such solutions are technically

or economically infeasible, solutions that reduce but

do not eliminate the hazard should then be consid-

ered. Warnings and other means of changing human

behavior, such as training, education, and supervision,

fall in this latter category for obvious reasons. Sim-

ply put, these behavior-oriented approaches will never

completely eliminate human errors and violations. On

the other hand, this is also true for most design so-

lutions. Consequently, warnings are often a necessary

supplement to other methods of hazard control [39.10].

There are many ways warnings can be used as

a supplement to other methods of hazard control; for

example, warnings can be included in safety training

materials, hazard communication programs, and within

various forms of safety propaganda, including safety

posters and campaigns, to educate workers about risks

and persuade them to behave safely. Particularly critical

procedures include start-up and shut-down procedures,

setup procedures, lock-out and tag-out procedures

during maintenance, testing procedures, diagnosis pro-

cedures, programming and teaching procedures, and

numerous procedures specific to particular applications.

The focus here is to reduce errors and intentional viola-

tions of safety rules by improving worker knowledge of

what the hazards are and their severity, how to identify

and avoid them, and what to do after exposure. Inex-

perienced workers are often the target audience at this

stage. Warnings can also be included in manuals or job

performance aids (JPAs), such as written procedures,

checklists, and instructions. Such warnings usually con-

Part D 39.1

Safety Warnings for Automation 39.1 Warning Roles 673

sist of brief statements that either instruct less-skilled

workers or remind skilled workers to take necessary

precautions when performing infrequent maintenance

or repair tasks. This approach can prevent workers from

omitting precautions or other critical steps in a task.

To increase their effectiveness, such warnings are often

embedded at the appropriate stage within step-by-step

instructions describing how to perform a task. Warning

signs, barriers, or markings at appropriate locations, can

play a similar role; for example, a warning sign placed

on a safety barrier or fence surrounding a robot installa-

tion might state that no one except properly authorized

personnel is allowed to enter the area. Placing a label on

a guardto warn thatremoving the guard creates a hazard

also illustrates this approach.

Warning signals can also serve as a supplement to

other safety devices such as interlocks or emergency

a)

b)

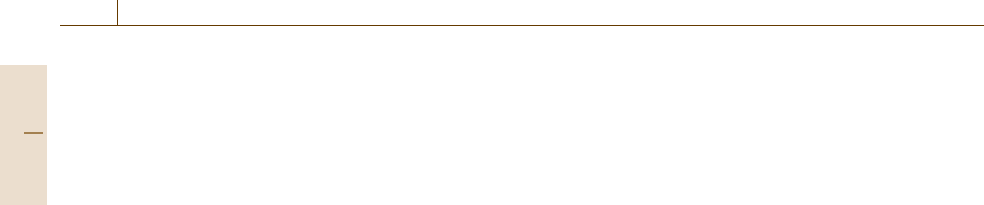

Fig. 39.1a,b Auto-body assembly line safety light curtain

system (courtesy of Sick Inc., Minneapolis)

Fig. 39.2 Safety laser scanner application (courtesy of

Sick Inc., Minneapolis)

braking systems; for example, presence sensing and

interlock devices are sometimes used in installations

of robots to sense and react to potentially dangerous

workplace conditions. Sensors used in such systems

include (1) pressure-sensitive floor mats, (2) light

curtains, (3) end-effector sensors, (4) ultrasound, ca-

pacitive, infrared, and microwave sensing systems, and

(5) computer vision. Floor mats and light curtains are

used to determine whether someone has crossed the

safety boundary surrounding the perimeter of the robot.

Perimeter penetration will trigger a warning signal and

in some cases will cause the robot to stop. End-effector

sensors detect the beginning of a collision and trigger

emergency stops. Ultrasound, capacitive, infrared, and

microwave sensing systems are used to detect intru-

sions. Computer vision theoretically can play a similar

role in detecting safety problems.

Figure 39.1a and b illustrate how a presence sensing

system, in this case a safety light curtain device in an

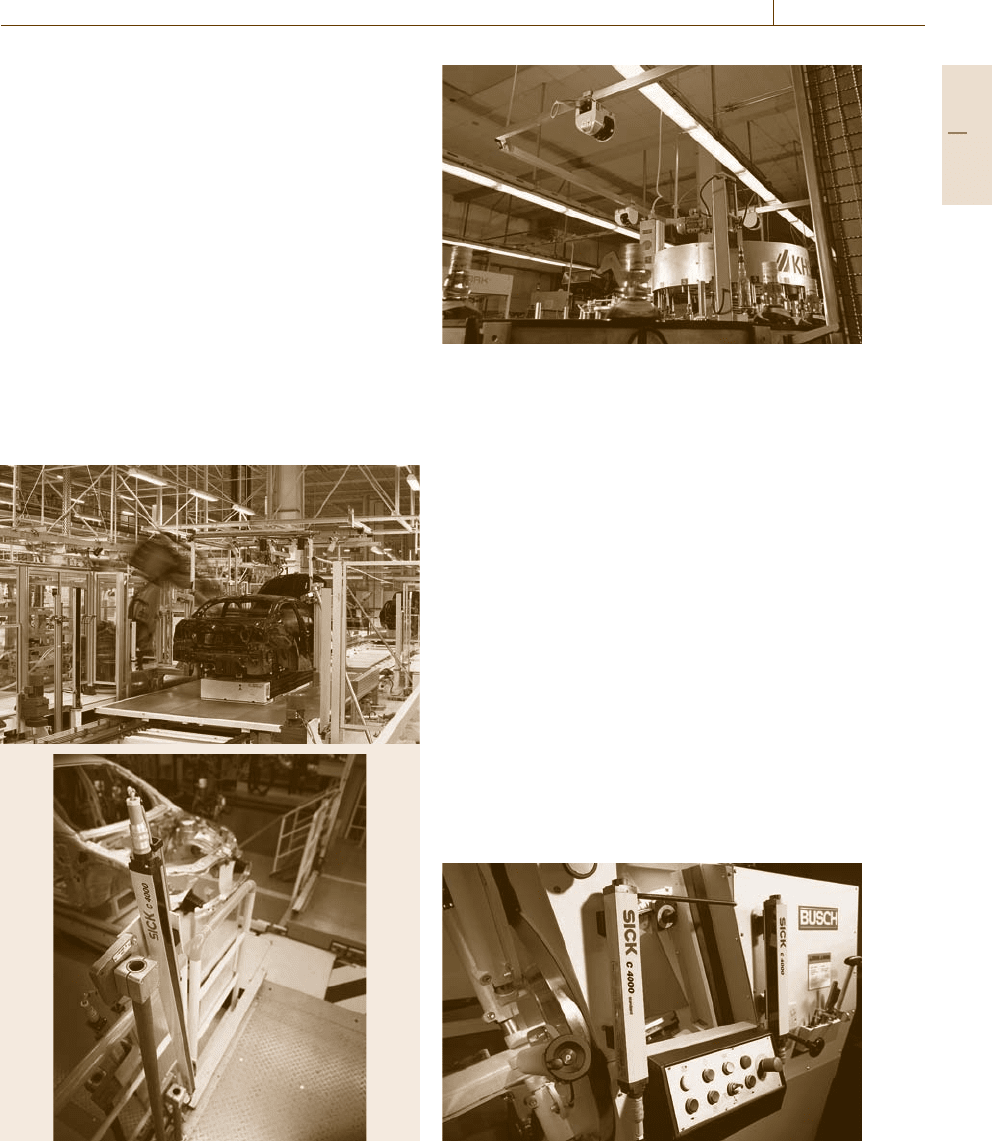

Fig. 39.3 C4000 safety light curtain hazardous point pro-

tection (courtesy of Sick Inc., Minneapolis)

Part D 39.1

674 Part D Automation Design: Theory and Methods for Integration

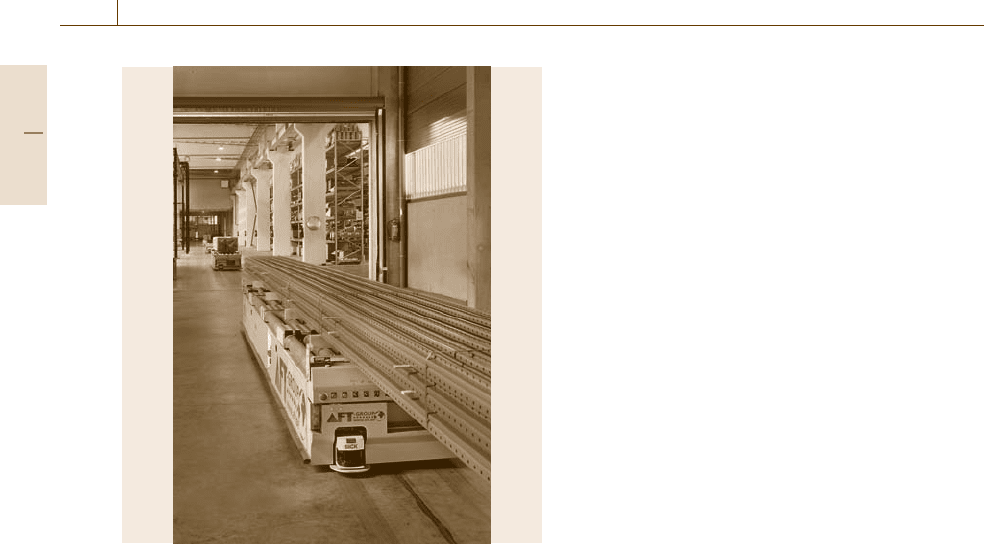

Fig. 39.4 Safety laser scannerAGV (automated guidedve-

hicle) application (courtesy of Sick Inc., Minneapolis)

auto-body assembly line, might be installed for point

of operation, area, perimeter, or entry/exit safeguard-

ing. Figure 39.2 illustrates a safety laser scanner. By

reducing or eliminating the need for physical barriers,

such systems make it easier to access the robot sys-

tem during setup and maintenance. By providing early

warnings prior to entry of the operator into the safety

zone, such systems can also reduce the prevalence of

nuisance machine shut-downs (Fig.39.3). Furthermore,

such systems can prevent the number of accidents by

providing warning signals and noises to alert personnel

on the floor (Fig.39.4).

39.1.2 Warning as a Form of Automation

Automated warning systems have been implemented in

many domains, including aviation, medicine, process

control and manufacturing, automobiles and other sur-

face transportation, military applications, and weather

forecasting, among others. Some specific examples of

automated systems include collision warning systems

and ground proximity warning systems in automo-

biles and aircraft, respectively. These systems will alert

drivers or pilots when a collision with another vehicle

or the ground is likely, so that they can take evasive

action. In medicine, anesthesiologists and medical care

workers must monitor patients’ vitals, sometimes re-

motely. Similarly, in process control, such as nuclear

power plants, workers must continuously monitor mul-

tiple subsystems to ensure that they are at safe and

tolerable levels. In these situations, automated alerts

can be used to inform operators of any significant de-

partures from normal and acceptable levels, whether in

the patients’ condition or in plant operation and safety.

Automation may be particularly important for com-

plex systems, which may involve too much information

(sometimes referred to as raw data), creating difficul-

ties for operators in finding relevant information at the

appropriate times. In addition to simply informing or

alerting the human operator, automation can play many

different roles, from guiding human information gather-

ing to taking full control of the system.

As impliedby the above examples, automated warn-

ing systems come in many forms, across a wide variety

of domain applications. Parasuraman et al. [39.11]

propose a taxonomy of human–automation interaction

that provides a useful way of categorizing the function

of these systems according to the psychological pro-

cess they are intended to replace or supplement. As

shown in Fig.39.5, automation can be applied at any

of four stages: (1) information acquisition, (2) infor-

mation analysis (3) decision selection, and (4) action

implementation. These fourstages are basedon asimple

model of human information processing (sensory pro-

cessing, cognition/working memory, decision making,

response execution). The model proposed by Parasur-

aman et al. [39.11] also maps onto Endsley’s [39.12]

model of situation awareness (SA), with early stages

of automation contributing to the establishment and

maintenance of SA (as also shown in Fig.39.5). Good

situation awareness is an important precursor to accu-

rate decision making and action selection.

For any given automated system, the level of au-

tomation at each stage of the model can vary from low

to high and this level will dictate how much control the

human is afforded in the operation of the system. As

expanded upon in the following discussion, the func-

tions performed by automated warning systems tend to

fall into the second and third stages of automation (in-

formation analysis and decision selection, respectively),

depending on whether they simply provide human op-

erators with alerts or whether they indicate also the

appropriate course of action.

Stage 1: Information Acquisition

At the first stage, automation involves the acquisition

and registration of multiple sources of input data. Au-

Part D 39.1