Механов, В.Б. Особенности архитектуры универсальных микропроцессоров

Подождите немного. Документ загружается.

151

– используется множественное декодирование х86 инст-

рукций в однотактные RISC-операции;

– процессор поддерживает логику предсказания ветвлений,

используя таблицу истории ветвлений из 8192 элементов, кэш

адресов перехода и стек возврата, которые обеспечивают веро-

ятность правильного предсказания перехода выше 0,95. В про-

цессоре используется двухуровневая схема предсказания ветв-

лений. Таблица истории ветвлений не хранит при предсказании

целевых адресов, специальные адресные АЛУ вычисляют целе-

вые адреса во время декодирования инструкции. Кэш адресов

ветвлений обеспечивает уточнение предсказанного ветвления,

уменьшая потери при обращении к памяти. Кэш адресов по-

ставляет на дешифраторы первые 16 байт инструкций, выбран-

ных согласно прогнозу ветвления;

– процессор содержит параллельные дешифраторы, цен-

трализованный планировщик операций и семь исполнительных

блоков, которые обеспечивают суперскалярное выполнение х86

инструкций в шестиступенчатом конвейере;

– в процессоре используется спекулятивное исполнение с

изменением последовательности команд, предварительная по-

сылка данных, переименование регистров.

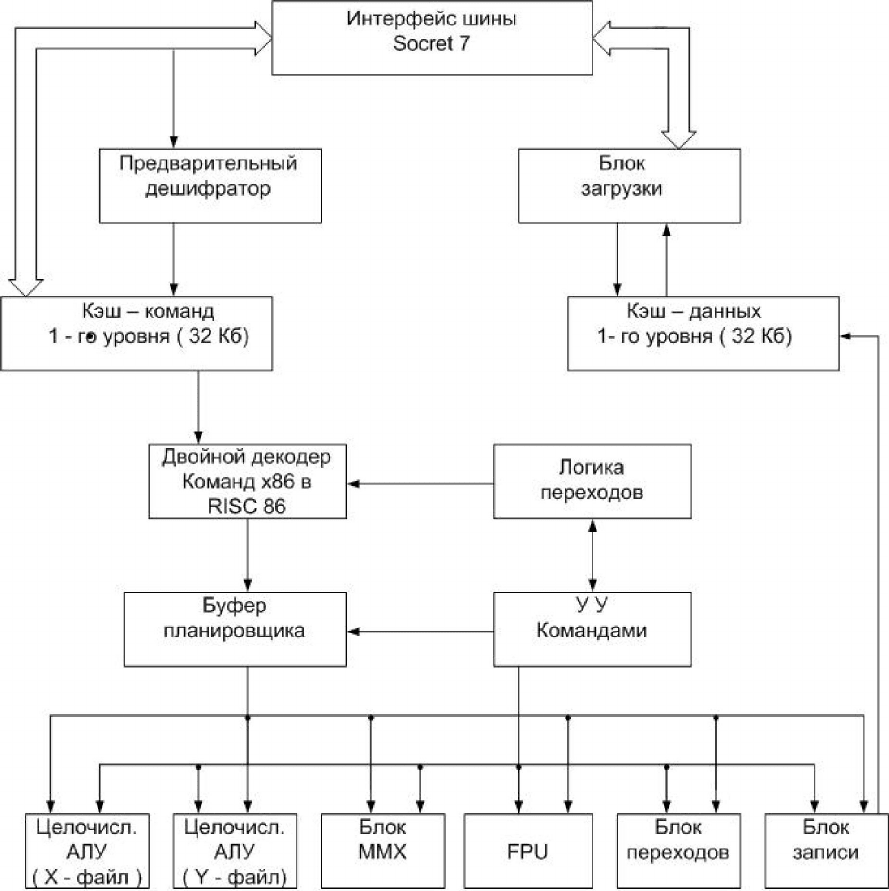

Структура микропроцессора К6 приведена на рис. 6.2.

RISC-ядро микропроцессора может выполнять за один такт

до шести команд RISC86. В процессе исполнения RОР ядро ис-

пользует 48 физических регистров – 24 регистра общего назна-

чения и 24 регистра для переименования. 24 регистра подразде-

ляются на 16 рабочих регистров и восемь регистров, соответст-

вующих универсальным регистрам архитектуры х86: ЕАХ, ЕВХ,

ЕСХ, ЕDХ, ЕВР, ЕSР, ЕSI и ЕDI.

Планировщик К6 содержит в буфере 24 команды RISC86 и

назначает инструкции на выполнение семи исполнительным уст-

ройствам:

– модулю сохранения;

– модулю загрузки;

– модулю перехода;

– двум целочисленным АЛУ;

152

– целочисленному блоку мультимедийных команд;

– блоку операций с плавающей точкой.

Наличие буфера позволяет планировщику в динамике ана-

лизировать и изменять выбранную для исполнения последова-

тельность команд, обеспечивая максимальную загрузку испол-

нительных устройств.

Блок мультимедийных команд выполняет все инструкции

расширения MМХ. Целочисленный Х-блок выполняет арифме-

тико-логические операции, включая умножение, деление, сдвиг,

циклический сдвиг. Y-блок – основные одно- и двухсловные

арифметико-логические операции: АDD, AND, СМР, ОR, SUB,

ХОR, расширение нуля и расширение знакового разряда числа.

Блок вычислений с плавающей точкой выполняет все команды с

плавающей точкой. Блок переходов осуществляет обновление

состояния процессора (регистров, флагов) после подтверждения

предсказанного условного ветвления, обеспечивая тем самым

возможность спекулятивного выполнения команд (на глубину до

7 переходов).

153

Рис. 6.2. Структура микропроцессора К6

6.3. Микропроцессор К7

Микропроцессор К7 (кодовое имя Athlon) начал выпус-

каться в 1999 г. сначала по технологии 0,25 мкм (22 млн транзи-

сторов на кристалле), затем – 0,18 мкм (37 млн транзисторов на

кристалле).

Архитектура, реализованная в Athlon, получила название

QuantiSpeed. Она включает в себя суперскалярное конвейерное

выполнение команд, конвейерный блок вычислений с плаваю-

щей точкой, аппаратную предвыборку данных в кэш-память и

усовершенствованную технологию предсказания ветвлений.

154

Athlon имеет девять исполнительных блоков: три для обра-

ботки целочисленных данных, три для вычисления адреса и три

блока для вычислений с плавающей точкой и обработки муль-

тимедийных данных (один для загрузки/сохранения данных с

плавающей точкой и два конвейерных блока для исполнения

команд). Длина целочисленного конвейера составляет 10 стадий,

конвейера с плавающей точкой – 15 стадий (в предыдущих мо-

делях FPU не был конвейеризированным). Команда FPU Athlon

позволяет одновременно выполнять до двух команд с плаваю-

щей точкой.

Athlon может декодировать три команды х86 в шесть RISC-

операций. После декодирования ROP попадают в буфер, где

ожидают своей очереди на выполнение в одном из функцио-

нальных блоков процессора. Буфер К7 содержит 72 операции

(в три раза больше, чем у К6) и выдает 9 ROP для 9 исполни-

тельных устройств.

Увеличенная до 2048 позиций таблица предсказания пере-

ходов (в два раза больше, чем у Pentium III) и усовершенство-

ванный алгоритм предсказания позволяют давать правильный

прогноз в 95 % случаев (у Pentium III всего 90 %).

Athlon имеет 128 Кб кэш-памяти первого уровня (64 Кб для

данных и 64 Кб для команд). Для взаимодействия с кэш-

памятью второго уровня предусмотрена специальная шина (как

у архитектуры Р6 Intel). Кэш-память второго уровня размером

512 Кб расположена вне процессорного ядра, в процессорном

картридже, и работает на половинной частоте ядра.

Использование при производстве процессора Athlon техно-

логии 0,18 мкм с медными соединениями позволило разработ-

чикам разместить на кристалле кэш-память второго уровня раз-

мером 256 Кбайт, работающую на тактовой частоте ядра.

Разновидностью микропроцессора с архитектурой К7 стал

Duron – бюджетный вариант микропроцессора, ориентирован-

ный на дешевые ПК. Основным его отличием является умень-

шенная до 64 Кб кэш-память второго уровня. Микропроцессор

Duron содержит 25 млн транзисторов на кристалле.

155

Благодаря примененным в К7 новым архитектурно-техни-

ческим решениям микропроцессорам AMD удалось на 7–10 %

превысить производительность Pentium III при равных тактовых

частотах.

Дальнейшее совершенствование архитектуры и технологии

производства микропроцессоров в рамках семейства К7 привело

к появлению двух новых версий Athlon: Athlon XP и Athlon MP.

Процессор Athlon ХР имеет целый ряд преимуществ:

– расширен набор инструкций;

– благодаря усовершенствованному ядру Athlon ХР по-

требляет на 20 % меньше мощности, чем Athlon при той же час-

тоте;

– усовершенствован алгоритм предсказания ветвлений;

– улучшен механизм опережающей загрузки инструкций из

основной памяти в кэш;

– модифицирован буфер преобразования адресов TLB;

– в процессор встроен термодатчик, позволяющий опреде-

лять температуру кристалла.

Данный микропроцессор ориентирован на использование в

высокопроизводительных персональных компьютерах, и особую

эффективность, по мнению разработчиков, он должен проявлять

при работе с операционной системой Windows ХР (отсюда и ХР

в названии процессора).

Процессор содержит 54,3 млн транзисторов на кристалле.

Производился Athlon ХР изначально по технологии 0,18 мкм,

а затем – 0,13 мкм с использованием медных проводников.

Athlon МР предназначен для использования в серверах и

мощных рабочих станциях и предусматривает возможность ра-

боты в двухпроцессорной конфигурации.

6.4. Микропроцессоры AMD с 64-разрядной

архитектурой Opteron (Hammer)

Восьмое поколение процессоров AMD основано на техно-

логии AMD64, которая существенно расширяет традиционную

архитектуру x86. В результате не только достигается увеличение

общей производительности, но и обеспечиваются масштабируе-

мость и гибкость системы.

156

Стратегический подход AMD к переходу на 64-битные вы-

числения основывается на обеспечении совместимости с суще-

ствующими 32-разрядными приложениями и операционными

системами и одновременно возможности использовать 64-

разрядные приложения там, где это необходимо.

Сравнительные характеристики архитектуры AMD64 и

других 64-битных решений, присутствующих в настоящее время

на рынке, приведены в табл. 6.1.

Таблица 6.1

Архитектура AMD64 Другие 64-битные решения

Полная совместимость

с существующей архитектурой x86

Набор инструкций несовместим с

существующей x86 архитектурой

Высокая производительность

в 32-битном и в 64-битном режиме

Низкая производительность

в 32-битном режиме

Полная поддержка 16-, 32-

и 64-разрядных приложений,

работающих одновременно

Поддержка 16- и 32-разрядных

приложений только в режиме

программной или аппаратной

эмуляции

32-битный код работает

без изменений. Возможность

работы старых приложений

с 64-разрядным адресным

пространством

Необходимость перерабатывать

32-разрядный код для получения

максимальной

производительности

Архитектура AMD64 предполагает несколько режимов ис-

полнения кода в зависимости от выполняемой задачи: Long

mode и Legacy mode.

Режим Long mode реализует главное преимущество новой

технологии и имеет два подрежима: 64-битный режим и режим

совместимости.

Режим Long mode имеет следующие особенности:

– 64-разрядное виртуальное адресное пространство и 52-

разрядное физическое адресное пространство;

– страничное управление памятью;

– ограниченная поддержка сегментации;

– отсутствие поддержки механизма переключения задач

архитектуры x86;

157

– отсутствие поддержки устаревшего реального режима и

режима Virtual-8086; поддержка только 64-битных приложений

и 16- и 32-битных приложений защищенного режима.

64-битный подрежим поддерживает все новые возможно-

сти процессора:

– 64-разрядная виртуальная адресация;

– расширения регистров, доступные с помощью нового

префикса (REX) 8 новых регистров общего назначения (R8–

R15);

– расширение всех регистров общего назначения до 64 бит;

– 8 новых 128-битных регистров SSE (XMM8–XMM15);

– 64-разрядный указатель команд.

Подрежим совместимости позволяет 64-разрядным опе-

рационным системам сохранить полную совместимость с суще-

ствующими 16- и 32-разрядными приложениями, т.е. возмож-

ность исполнять любые приложения без перекомпиляции в 64-

разрядной операционной системе. В режиме совместимости при-

ложения имеют доступ к первым 4 Гб виртуального адресного

пространства. С точки зрения исполняющегося приложения ре-

жим совместимости выглядит как защищенный режим x86. С

точки зрения операционной системы трансляция адресов, обра-

ботка прерываний и исключений, а также системные структуры

данных используют механизмы режима Long mode.

Режим Legacy mode сохраняет полную двоичную совмес-

тимость с существующими 16- и 32-разрядными приложениями,

операционными системами и существующей 32-разрядной реа-

лизацией архитектуры x86.

Новое семейство микропроцессоров с архитектурой

AMD64 получило название Hammer (молоток). К нему относятся

микропроцессор для персональных компьютеров Claw (коготь)

Hammer и серверный процессор Sledge (санки) Hammer. Оба

процессора производятся по технологии 0,13 мкм с медными со-

единениями и изолированной подложкой. Микропроцессоры

данного семейства являются 64-разрядными, однако, в отличие

от архитектуры IA-64 Intel, обеспечивают совместимость с сис-

158

темой команд х86, в связи с чем архитектура получила название

Х86-64.

Основные преимущества архитектуры х86-64 следующие:

– обратная совместимость с инструкциями х86;

– 64-битные версии регистров общего назначения;

– 8 новых РОН, доступных только для 64-битных прило-

жений;

– увеличение объема адресуемой памяти;

– высокая производительность 32-битных приложений,

поддержка 64-битных приложений.

Создавая новую архитектуру, разработчики компании

AMD стремились повысить производительность микропроцес-

сора не только за счет увеличения тактовой частоты или числа

вычислительных блоков, но и за счет повышения степени их за-

грузки. С этой целью в микропроцессор внесены следующие из-

менения:

– увеличена длина вычислительных конвейеров: целочис-

ленного конвейера – до 12 стадий, с плавающей точкой – до 17

стадий;

– встроен контроллер памяти;

– усовершенствован блок предсказания ветвлений;

– встроен когерентный интерфейс HyperTransport.

Встроенный когерентный интерфейс HyperTransport обес-

печивает возможность использования Hammer в мультипроцес-

сорной конфигурации.

Улучшение блока предсказания ветвлений заключается в

выявлении и учете информации о типе ветвлений: статическое

ветвление, т.е. адрес перехода не изменяется, или динамическое.

Различия процессоров для одно- и многопроцессорных

конфигураций заключаются в основном в размере кэш-памяти

второго уровня и числе портов интерфейса HyperTransport.

159

7. Универсальные микропроцессоры

других архитектур

7.1. Микропроцессоры с архитектурой Alpha

(фирма DEC)

7.1.1. Микропроцессоры Alpha 2106х

До появления микропроцессоров Itanium микропроцессоры

с архитектурой Alpha на протяжении многих лет являлись наи-

более производительными однокристальными устройствами,

выпускаемыми серийно.

Микропроцессоры Alpha являются хорошей иллюстрацией

концепции Speed Daemon – достижения высокой производи-

тельности за счет увеличения тактовой частоты при относитель-

но простой логике функционирования.

Архитектура микропроцессоров Alpha впервые была пред-

ставлена в феврале 1992 г. на конференции ISSСС, а уже февра-

ле 1993 г. был выпущен первый из микропроцессоров – Alpha

21064 с тактовой частотой 200 МГц. (Микропроцессор Pentium с

такой тактовой частотой появился только в 1996 г.).

Благодаря высокой тактовой частоте и высокой степени

конвейеризации выполняемых операций (до 10 тактов на опера-

цию) этот микропроцессор надолго занял лидирующее положе-

ние по производительности.

Основной областью использования процессора явились

высокопроизводительные рабочие станции и серверы.

Следующими в сентябре 1993 г. были выпущены микро-

процессоры Alpha 21066–166 МГц и Alpha 21068–66 МГц. Эти

процессоры были ориентированы на использование в более де-

шевых системах – рабочих станциях нижнего и среднего уровня.

Архитектура ядра данных микропроцессоров аналогична Alpha

21064. На кристалле микропроцессоров Alpha 21066/21068 рас-

полагались контроллеры: прямого доступа к памяти, графиче-

160

ский и шины РСI, что позволяло снизить стоимость и упростить

построение систем на их основе.

Выпуск в октябре 1993 г. микропроцессора Alpha 21064А с

тактовыми частотами 225 и 275 МГц еще более упрочил пози-

ции микропроцессоров компании DЕС как лидеров по произво-

дительности.

Микропроцессор Alpha 21064 имеет 64-разрядную супер-

скалярную RISC-архитектуру с двумя исполнительными конвей-

ерами и может выполнять за один такт до двух команд с фикси-

рованной и плавающей точкой или команду перехода. Блок

предсказания перехода обеспечивает вероятность правильного

прогноза 0,8.

Микропроцессор содержит на кристалле раздельные кэш-

памяти команд и данных, каждая емкостью 16 Кб, 32 регистра

с плавающей точкой и 32 регистра с фиксированной точкой.

Кэш второго уровня – внешний, может составлять от 128 Кб до

16 Мб. Тактовая частота шины в системе может быть в 2,5–10

раз меньшей, чем частота работы микропроцессора. Ширина

внешних шин адреса и данных составляет 43 и 128 бит соответ-

ственно.

В микропроцессорах Alpha 21064 не используется сложная

логика переупорядочивания команд и переименования регист-

ров. Обеспечение эффективной загрузки исполнительных уст-

ройств возлагается на компилятор.

7.1.2. Микропроцессор Alpha 21164

Следующим рекордным достижением DЕС стал выпуск в

сентябре 1994 г. микропроцессора нового поколения Alpha

21164, с тактовыми частотами 266 и 300 МГц. Это был первый

микропроцессор, имеющий производительность до 1,2 млрд

операций в секунду.

Структура микропроцессора приведена на рис. 7.1.

Архитектура этого процессора максимально ориентирована

на достижение высокой тактовой частоты.

По сравнению с предыдущим поколением, в Alpha 21164

вдвое увеличилось число исполнительных устройств, а число

тактов, требуемых для выполнения команд, уменьшилось.