Механов, В.Б. Особенности архитектуры универсальных микропроцессоров

Подождите немного. Документ загружается.

111

4.3.3. Использование привилегий

в защищенном режиме

Уровни привилегий обеспечивают защиту задач, изоли-

руемых друг от друга локальными таблицами дескрипторов.

Программы операционной системы, обработчики прерываний и

другое системное обеспечение могут включаться в виртуальное

адресное пространство каждой задачи и защищаться системой

привилегий. Каждая часть системы работает на своем уровне

привилегий.

Задачи, дескрипторы и селекторы имеют свои атрибуты

привилегий.

Привилегии задач (Task Privilege) действуют на выполне-

ние инструкций и использование дескрипторов. Текущий уро-

вень привилегии задачи CPL (Current Privilege Level) определя-

ется двумя младшими битами регистра CS. CPL задачи может

изменяться только при передаче управления к новому сегменту

через дескриптор вентиля. Задача начинает выполняться с уров-

ня CPL, указанного селектором кодового сегмента внутри TSS,

когда задача инициируется посредством операции переключе-

ния задач. Задача, выполняемая на нулевом уровне привилегий,

имеет доступ ко всем сегментам, описанным в GDT, и является

самой привилегированной. Задача, выполняемая на уровне 3,

имеет наиболее ограниченные права доступа. Текущий уровень

привилегии может изменяться только при передаче управления

через вентили.

Привилегии дескриптора (Descriptor Privilege) задаются

полем DPL байта управления доступом. DPL определяет наи-

меньший уровень привилегий, с которым возможен доступ к

данному дескриптору. Самый защищенный дескриптор имеет

DPL = 0, к нему имеют доступ только задачи с CPL = 0. Самый

беззащитный дескриптор имеет DPL = 3, его могут использовать

задачи с CPL = 0, 1, 2, 3. Это правило применимо ко всем деск-

рипторам, за исключением дескриптора LDT.

Привилегии селектора (Selector Privilege) задаются полем

RPL (Requested Privilege Level) – двумя младшими битами се-

лектора. С помощью RPL можно урезать эффективный уро-

112

вень привилегий EPL (Effective Privilege Level), который опре-

деляется как максимальное арифметическое из значений CPL и

RPL. Селектор с RPL = 0 не вводит дополнительных ограниче-

ний.

Контроль доступа к сегментам данных производится при

исполнении команд, загружающих селекторы в сегментные ре-

гистры SS, DS, ES, FS и GS. Команды загрузки DS, ES, FS и GS

должны ссылаться на дескрипторы сегментов данных или сег-

ментов кодов, допускающих чтение. Для получения доступа эф-

фективный уровень привилегий EPL должен быть равным или

меньшим (арифметически) уровня привилегий DPL дескрипто-

ра. Если эффективный уровень привилегий не разрешает доступ,

ссылка идет на некорректный тип дескриптора (на дескриптор

вентиля или на дескриптор только исполняемого кодового сег-

мента) или на несуществующий дескриптор вырабатываются

соответствующие исключения.

Команды загрузки SS должны ссылаться на дескриптор

сегмента данных, допускающий запись. При этом DPL и RPL

должны быть равны CPL.

Контроль типов привилегий при передаче управления про-

изводится при загрузке селектора в регистр CS. Тип дескрипто-

ра, на который ссылается данный селектор, должен соответство-

вать выполняемой инструкции. Нарушение типа (например,

ссылка инструкции JMP на вентиль вызова) порождает исклю-

чение. При передаче управления действуют следующие правила

привилегий, нарушение которых также приводит к исключению:

– команды JMP или CALL могут ссылаться на сегмент с

DPL, равным CPL;

– прерывания внутри задачи или вызовы, которые могут

изменить уровень привилегий, могут передавать управление ко-

довому сегменту с уровнем привилегий, равным или больше

уровня привилегий CPL, только через вентили с тем же или

меньшим уровнем привилегий, чем CPL;

– инструкции возврата, которые не переключают задачи,

могут передать управление только кодовому сегменту с таким

же или меньшим уровнем привилегий;

113

– переключение задач может выполняться с помощью вы-

зова, перехода или прерывания, которые ссылаются на вентиль

задачи или сегмент состояния задачи (TSS) с тем же или мень-

шим уровнем привилегий.

Смена уровня привилегий, происходящая при передаче

управления, автоматически вызывает переопределение стека.

Начальное значение указателя стека SS:SP для уровня привиле-

гий 0, 1, 2 содержится в TSS. При передаче управления по ко-

мандам JMP или CALL в SS:SP загружается новое значение ука-

зателя стека, а старые значения помещаются в новый стек. При

возврате на прежний уровень привилегий его стек восстанавли-

вается (как часть инструкции возврата). Для вызовов подпро-

грамм с передачей параметров через стек и сменой уровня при-

вилегий из предыдущего стека в новый копируется фиксирован-

ное число слов, заданное в вентиле. Команда межсегментного

возврата RЕТ с выравниванием указателя стека при возврате

корректно восстановит значение предыдущего указателя.

Привилегии и битовая карта разрешения ввода-вывода

контролируют возможность выполнения операций ввода-вывода

и управления флагом прерываний IF. Уровень привилегий вво-

да-вывода определяется полем IOPL (Input/Output Privilege

Level) регистра флагов. Значение IOPL можно изменить только

при CPL = 0.

При CPL ≤ IOPL на операции ввода-вывода и управление

флагом IF никаких ограничений не накладывается.

4.3.4. Страничное управление памятью

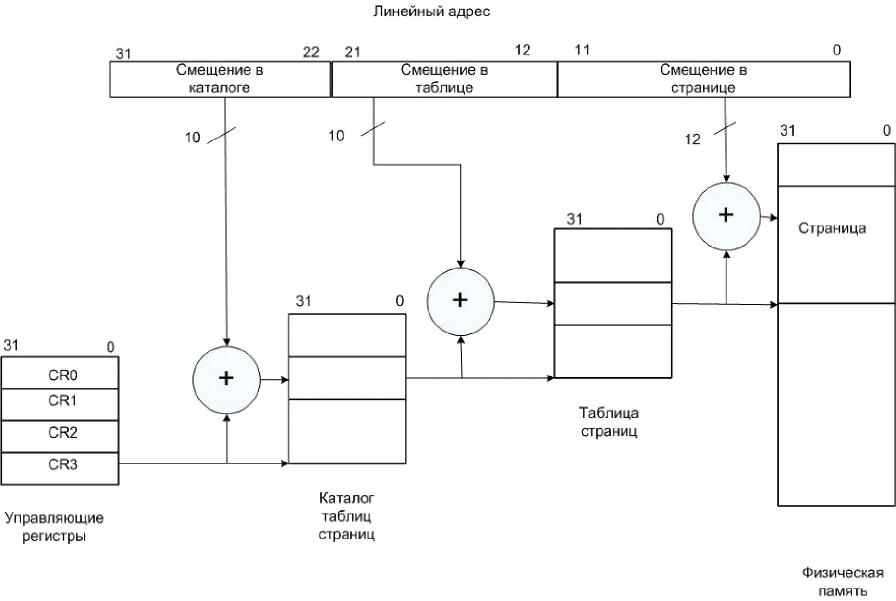

Механизм страничного управления использует двухуров-

невую табличную трансляцию линейного адреса в физический

(рис. 4.9).

Механизм имеет три части: каталог страниц (Page

Directory), таблицы страниц (Page Tables) и собственно страни-

цы (Page Frame). Механизм включается установкой бита PG = 1

в регистре CR0. Регистр CR2 хранит линейный адрес отказа и

адрес памяти, по которому был обнаружен последний отказ

страницы. Регистр CR3 хранит физический адрес каталога стра-

114

ниц. Его младшие 12 бит всегда нулевые (каталог выравнивается

по границе страницы).

Каталог страниц размером 4 Кб имеет 1024 строки (вхож-

дения). Каждая строка содержит 20 старших бит адреса таблицы

следующего уровня (младшие биты этого адреса всегда нулевые)

и признаки (атрибуты) этой таблицы. Индексом поиска в ката-

логе страниц является 10 старших бит линейного адреса (А22–

А31).

Каждая таблица страниц также имеет 1024 строки анало-

гичного формата, но эти строки содержат базовый физический

адрес и атрибуты самих страниц. Индексом поиска в таблице

являются биты А12–А21 линейного адреса. Физический адрес

собирается из адреса страницы, взятого из таблицы, и младших

12 бит линейного адреса.

Рис. 4.9. Механизм страничной переадресации

Обращение при каждой операции доступа к памяти через

две таблицы, расположенные в памяти, существенно снижает

производительность процессора. Для предотвращения этого за-

115

медления в процессор введен буфер ассоциативной трансляции

TLB для хранения интенсивно используемых строк таблицы.

В большинстве процессоров буфер представляет собой четырех-

канальный наборно-ассоциативный кэш на 32 строки таблицы

трансляции. Такой размер позволяет хранить информацию о

трансляции 128 Кб памяти, что в большинстве случаев мульти-

задачного использования дает коэффициент кэш-попаданий

98 %, т.е. только 2 % обращений к памяти требуют дополни-

тельных обращений к таблицам.

Механизм страничной адресации работает следующим об-

разом. Когда страничное управление разрешено (бит PG = 1

в CR0), блок страничного преобразования получает 32-битный

линейный адрес от блока сегментации. Его старшие 20 бит срав-

ниваются со значениями из TLB. В случае попадания физиче-

ский адрес вычисляется с использованием значения начального

адреса страницы, полученного из TLB, и выводится на шину ад-

реса. Если соответствующей строки в TLB нет, то производится

чтение строки из страничного каталога. Если строка имеет бит

доступности Р = 1 (таблица присутствует в памяти), в ней уста-

навливается бит доступа и производится чтение ею указанной

строки из таблицы второго уровня. Если и в этой строке Р = 1,

процессор вычисляет физический адрес и, наконец, производит

по нему обращение. Если на этом пути встречается страница

с Р = 0, вырабатывается исключение, обработчик которого дол-

жен принять меры по загрузке затребованной страницы в опера-

тивную память. Поскольку это исключение классифицируется

как отказ, после его обработки (успешной) повторяется доступ к

затребованной ячейке памяти.

Операционная система должна корректно сгенерировать

начальные таблицы трансляции и обрабатывать исключения от-

казов. В случае изменения таблиц она должна очищать буфер

TLB путем загрузки регистра CR3. Очистка TLB должна произ-

водиться и при изменении значений бита Р в любых таблицах.

В отличие от «непробиваемой» сегментной защиты, спосо-

бы обхода страничной защиты есть и на уровне пользователя.

116

4.4. Режим виртуального

микропроцессора 8086 (V86)

Прикладные программы для 8086 могут исполняться на

32-разрядных процессорах как в реальном режиме, так и в ре-

жиме виртуального 8086 (V86), который является особым со-

стоянием задачи защищенного режима. Режим V86 более при-

влекателен своими возможностями и гибкостью:

– в этом режиме работает защита и механизм страничной

переадресации, позволяющий адресоваться к любой области

4-гигабайтного пространства памяти;

– выполнение приложений 8086 в среде V86 возможно па-

раллельно с приложениями защищенного режима;

– несколько задач в режиме V86 совместно могут исполь-

зовать общие области кода операционной системы.

Все программы, выполняемые в режиме V86, имеют уро-

вень привилегий 3, т.е. минимальные привилегии (реальный ре-

жим подразумевает уровень привилегий 0). Таким образом, про-

граммы в V86 выполняются со всеми проверками защиты. По-

пытка выполнения привилегированных инструкций вызывает

исключение. Попытка выполнения инструкций, допустимых

только для защищенного режима, также вызовет исключение.

Прерывания в V86 для полной эмуляции машины на 8086

обрабатываются особым образом. Все прерывания и исключе-

ния влекут за собой смену уровня привилегий обратно к уровню

операционной системы защищенного режима. Эта ОС может

распознать, что прерывание пришло из V86, по образу регистра

флагов в стеке. Далее ОС может либо обработать это прерыва-

ние самостоятельно, либо переслать его к ОС реального режима,

работающей в V86.

В конечном итоге ОС защищенного режима может совер-

шенно прозрачно для приложения 8086, работающего в V86,

эмулировать окружение обычной машины 8086, включая пре-

рывания и перехватывая обращения к портам.

Вход в режим V86 – установка бита VM в регистре флагов

– возможен одним из двух способов:

117

– выполнение инструкции возврата в 32-битном режиме,

когда образ регистра флагов сохранен в стеке с установленным

битом VM (при CPL = 0, иначе бит VM не установится);

– переключение на задачу, у которой в TSS образ регистра

флагов имеет установленный бит VM.

Выход из режима V86 возможен только при обработке пре-

рывания. Если вызываемая процедура имеет CPL = 0, то бит VM

будет сброшен, и она будет выполняться в защищенном режиме.

Если ее CPL > 0, произойдет нарушение защиты. Если прерыва-

ние вызывает переключение задач, состояние регистров с уста-

новленным флагом VM сохранится в TSS старой задачи, к кото-

рой можно будет вернуться. Новый режим (защищенный или

V86) установится в соответствии с TSS новой задачи.

Значение бита VM не может изменено никакими другими

способами; кроме того, его значение не может быть и прочитано

– при любом программном сохранении регистра флагов значе-

ние VM всегда показывается нулевым. Так что приложение, вы-

полняемое в среде V86, никак не может ни переключить режим

процессора, ни распознать, в каком режиме – реальном или вир-

туальном – оно исполняется.

4.5. Режим системного управления SMM

Современные модели 32-разрядных микропроцессоров,

кроме обычных режимов – реального, защищенного и режима

V86, – имеют дополнительный режим системного управления

SMM (System Management Mode). Этот

режим предназначен для

выполнения некоторых действий с возможностью их полной

изоляции от прикладного программного обеспечения и даже

операционной системы. Главным образом этот режим предна-

значен для реализации системы управления энергопотреблени-

ем.

В режим SMM процессор может войти только по сигналу

на входе SMI# (System Management Interrupt). Сигнал SMI# для

процессора является запросом прерывания с наивысшим при-

оритетом. Обнаружив активный сигнал (низкий уровень) SMI#,

процессор по завершении текущей инструкции и выгрузки бу-

118

феров записи переключается в режим SMM. Сразу при входе

в SMM процессор сохраняет свой контекст – почти все регистры –

в специальной памяти SMRAM. Эта память является выделен-

ной областью физической памяти, доступ к которой обеспечива-

ется внешними (по отношению к процессору) схемами в шин-

ных циклах обращения к памяти только при наличии соответст-

вующего сигнала. После сохранения контекста процессор пере-

ходит к выполнению обработчика SMI, который расположен в

той же памяти SMRAM. Обработчик представляет собой после-

довательность обычных инструкций, исполняемых процессором

в режиме, напоминающем реальный. При входе в режим SMM

автоматически запрещаются аппаратные прерывания (включая и

немаскируемые) и не генерируются исключения, так что дейст-

вия процессора однозначно определяются программой обработ-

чика SMI. Процедура обработчика завершается инструкцией

возврата, по которой процессор восстанавливает свой контекст

из образа, хранившегося в SMRAM, и возвращается в обычный

режим работы.

При возврате из SMM возможны некоторые варианты, за-

казанные обработчиком (в пределах возможности SMM данного

процессора). Во-первых, обработчик может программно внести

изменения в образ контекста процессора, и при его восстановле-

нии процессор может вернуться не в то состояние, в котором

произошло SMI. Во-вторых, возможен выбор варианта для слу-

чая, когда прерывание SMI возникло во время останова процес-

сора по инструкции HALT: можно вернуться снова на инструк-

цию останова, а можно перейти к выполнению следующей за

ней инструкции. В-третьих, возможен рестарт (повторное вы-

полнение) инструкции ввода-вывода, предшествующей появле-

нию сигнала SMI.

Обработчик SMI «разбудит» устройство, после чего опера-

ция ввода-вывода рестартует, и прикладное ПО (или драйвер)

«не заметит», что устройство пребывало в спячке. Таким обра-

зом, управление потреблением может быть организовано на

уровне BIOS способом, совершенно «прозрачным» для про-

119

граммного обеспечения (в том числе и ОС). Прозрачность SMM

обеспечивается следующими свойствами режима:

– возможностью только аппаратного входа в SMM;

– исполнением кода SMM в отдельном адресном простран-

стве;

– полным сохранением состояния прерванной программы

в области SMRAM;

– запретом обычных прерываний;

– восстановлением состояния прерванной задачи по выхо-

ду из режима SMM.

Память SMRAM должна быть физически или логически

выделенной областью размером от 32 Кб (минимальные потреб-

ности SMM) до 4 Гб. SMRAM располагается, начиная с адреса

SMIBASE (по умолчанию 3000h).

Если режим SMM используется для отключения питания

процессора с возможностью быстрого «пробуждения», память

SMRAM, хранящая контекст процессора, должна быть энерго-

независимой. Память SMRAM должна быть схемотехнически

защищена от доступа прикладных программ. Процессор генери-

рует специальный выходной сигнал, который и должен явиться

«ключом» доступа к этой памяти.

В режиме SMM использование прерываний возможно, од-

нако предварительно необходимо позаботиться о корректной

инициализации таблицы прерываний, по крайней мере, для ис-

пользуемых векторов. Маскируемые аппаратные прерывания

могут быть разрешены просто установкой флага IF, немаскируе-

мое прерывание разрешается программным вызовом его обра-

ботчика.

Контекст математического сопроцессора (и регистры

ММХ) при SMI автоматически не сохраняется, поскольку опе-

рации с плавающей точкой в режиме SMM вряд ли кому-либо

потребуются. Однако если SMI используется для выключения

процессора, контекст блока FPU может быть программно сохра-

нен обработчиком.

Значение 3000h базового адреса SMRAM, устанавливаемое

по аппаратному сбросу (сигналу RESET) процессора, может

120

быть программно изменено на другое, выровненное по границе

32 Кб, во время исполнения обработчика SMI.