Аксенов, В.П. Сигнальные процессоры

Подождите немного. Документ загружается.

51

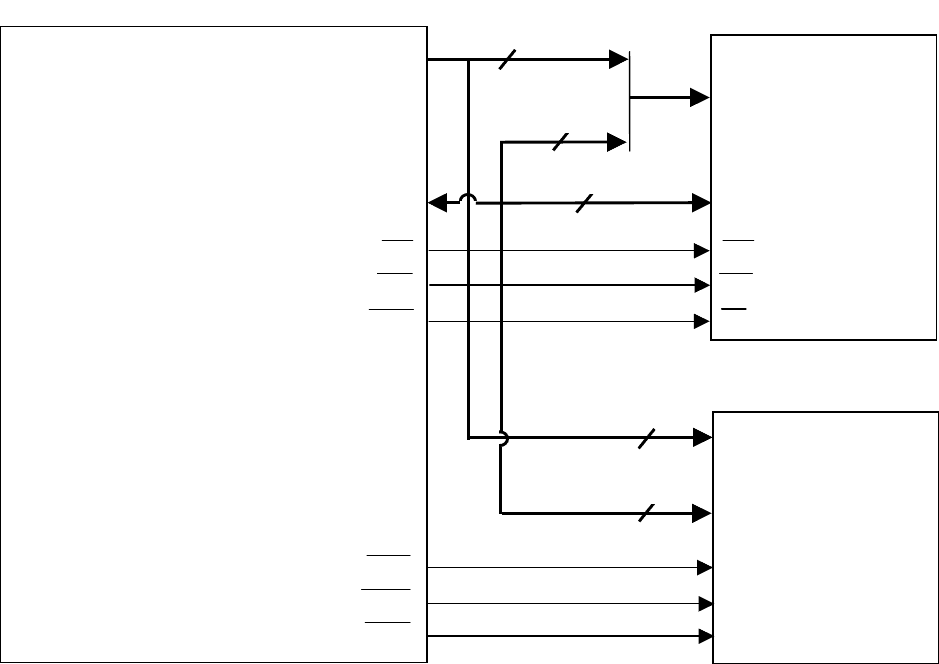

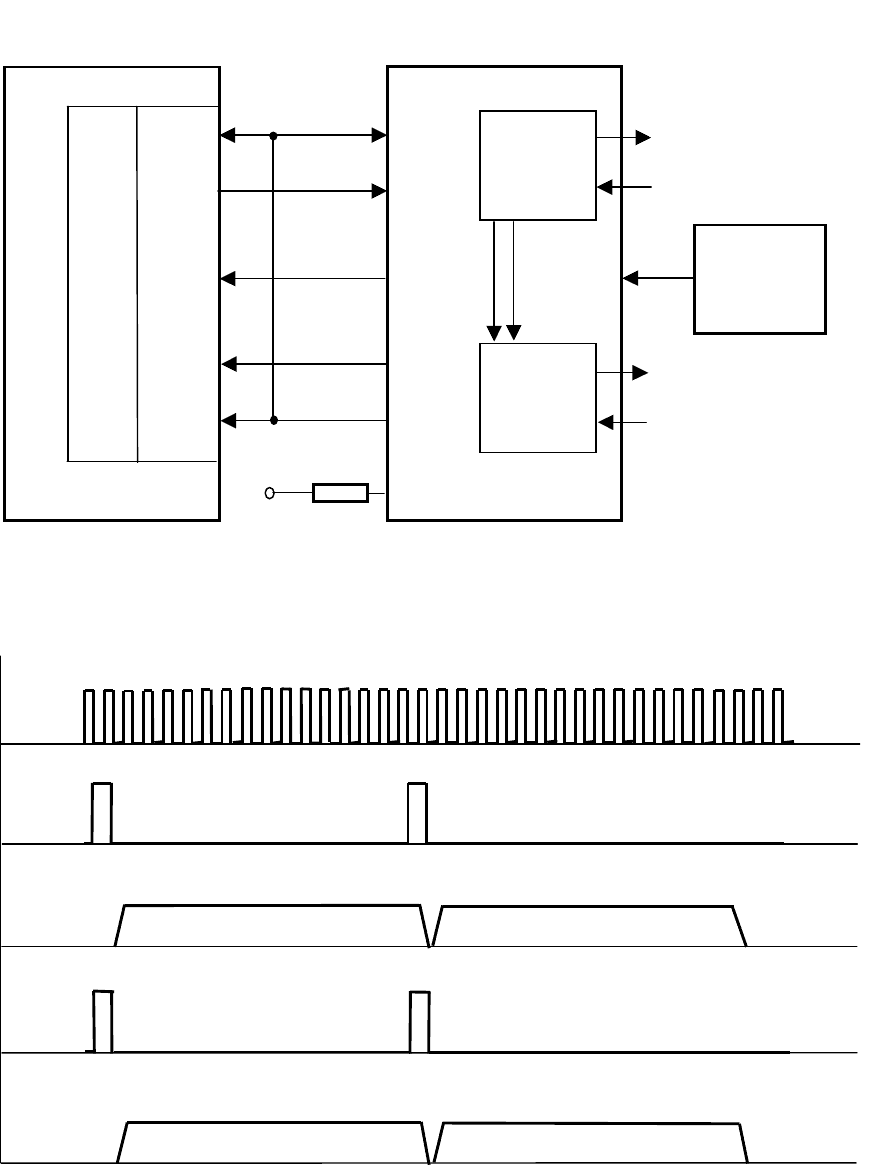

прямого доступа к памяти BDMA (Byte DMA) обеспечивает подключение мик-

росхем памяти ПЗУ или ОЗУ с байтовой организацией емкостью до 4 Мбайт

(рис. 31). Данное адресное пространство играет роль загрузочной области (boot

memory). Байтовая память имеет организацию 256 страниц по 16К×8 бит.

Для увеличения разрядности шины адреса кроме 14 сигналов А13-А0

программного счетчика в контроллере используются дополнительно 8 сигналов

шины данных D23-D16. Общее количество адресных сигналов, равное 22, оп-

ределяет максимальную емкость внешней памяти 2

22

= 4М, которую можно

подключить к порту BDMA для хранения программ и данных. Контроллер

обеспечивает передачу слова за один цикл и поддерживает начальную загрузку

процессора при включении напряжения питания.

Рис. 31. Использование внешней памяти

14

ПЗУ или ОЗУ

14

A13-A0

D23-D16

8

A21

-

A0

D15-D8

8

D7

-

D0

OE

WE

CS

ADDR 13 - 0

DATA 23 - 0

RD

WR

BMS

A13-A0

D23-D0

8

PMS

DMS

CMS

Оверлейная память

ADDR

DATA

ADSP-2189M

16

К для программ

16

К для данных

52

Выходные сигналы процессора

RD

и WR определяют направление пере-

дачи по шине данных. Сигнал шины управления

RD

организует чтение данных,

поступающих от микросхемы памяти, сигнал WR – запись данных во внеш-

нюю микросхему памяти. В обоих случаях обмен выполняется между встроен-

ной памятью процессора и внешней микросхемой.

Сигнал BMS используется для включения и отключения Z-состояния

внешней памяти. Высокий уровень сигнала BMS на выходе процессора пере-

водит микросхему ПЗУ или ОЗУ в высокоомное (Z) состояние для отключения

шины данных и шины адреса от соответствующих шин процессора DATA и

ADDR. Низкий уровень 0BMS = переводит внешнюю память в активное со-

стояние, в котором контроллер процессора выполняет операции чтения и запи-

си по двунаправленной шине данных, используя поочередно сигналы

RD

, WR .

Обмен с внешней микросхемой памяти контроллер BDMA выполняет в

фоновом режиме одновременно с выполнением секвенсором основной про-

граммы. Формат данных, передаваемых и принимаемых по шине DATA, авто-

матически определяется типом внутренней памяти. При обращении к памяти

программ РМ длина слова составляет 24 бита, при выполнении обмена с памя-

тью данных длину слова можно задать программно размером в 16 или 8 бит.

14-разрядный регистр BWCOUNT выполняет функцию счетчика передан-

ных слов. Перед обменом по интерфейсу BDMA в счетчик программно записы-

вается число слов для обмена. Контроллер уменьшает содержимое BWCOUNT

на единицу после каждого переданного слова. Обмен данными завершается по

условию BWCOUNT = 0. Максимальный размер одного блока данных состав-

ляет 2

14

= 16К слов. При запуске процессора по умолчанию в регистр записыва-

ется число 32. Это означает, что для начальной загрузки в процессор будет счи-

тано 32 слова из внешней микросхемы ПЗУ, которые используются для на-

стройки контроллера BDMA на прием оставшейся части программного кода

ПЗУ. Затем процессор начинает выполнение программы с адреса 0.

53

Разрядность программного счетчика (14 бит) позволяет процессору фор-

мировать 14 сигналов А13-А0 на шине адреса как для внутренней, так и внеш-

ней памяти. Это ограничивает максимальный размер исполняемого кода PM и

данных DM до 2

14

= 16К слов. Чтобы преодолеть данное ограничение в процес-

соре используется оверлейный механизм для работы с программами, размер ко-

торых больше 16К слов.

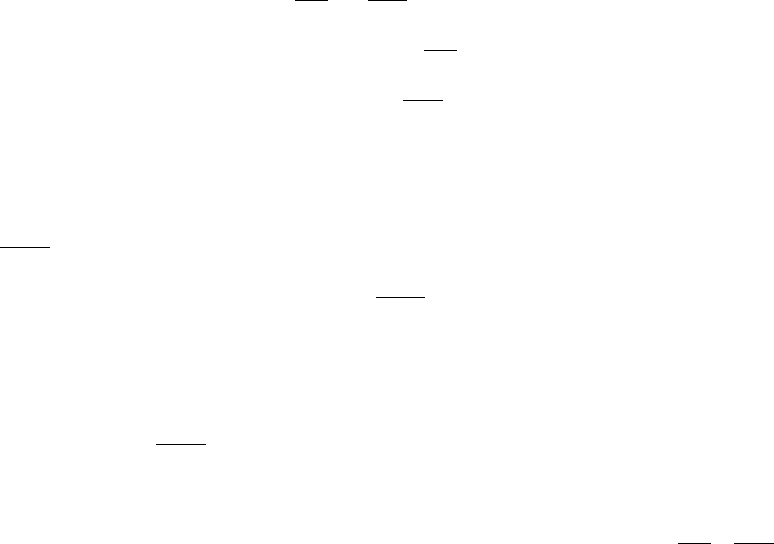

Расширение адресного пространства выполняется с помощью регистров

процессора PMOVLAY (program memory overlay) и DMOVLAY (data memory

overlay). Число, записанное в оверлейные регистры, используется процессором

для выбора одной из нескольких страниц памяти размером по 8К слов памяти

программ и 8К слов памяти данных. В указанные регистры необходимо про-

граммно записать одно из значений ряда 0,1,2,4,5,6,7. Страницы оверлея можно

менять в ходе выполнения программы, но процессор может работать в опреде-

ленный момент времени только с одной страницей. Распределение номеров

сегментов оверлея между внутренней и внешней памятью для одного из воз-

можных режимов процессора приведено на рис. 32. Внешняя память программ

и данных может использовать только страницы 1 и 2.

Рис 32. Структура памяти в режиме В = 0

Память программ

РМ оверлеи 0,4,5

для внутренней

памяти

РМ оверлеи 1,2

для внешней памяти

Внутренняя память

программ РМ

0х3FFF

0х3FE0

0х3FDF

0х2000

0х1FFF

0х0000

адрес

32 регистра управления

Внутренняя память

данных DМ

Память данных

DМ оверлеи 0,4,5,6,7

для внутренней памяти

DМ оверлеи 1,2

для внешней памяти

54

Секвенсор и генераторы адреса используют абсолютный адрес текущей

выполняемой команды и не контролируют состояние регистров PMOVLAY,

DMOVLAY. Неправильное изменение сегментов оверлея в командах безуслов-

ного перехода и при вызове процедур может привести к сбою программы. Во

время обращения к внешней памяти регистры управляют состоянием разряда

А13 шины адреса. Если в регистр PMOVLAY записана единица, то выходной

сигнал процессора А13 = 0, при PMOVLAY = 2 адресный сигнал А13 = 1.

Не следует путать оверлейную память со страничной памятью, которая

используется в универсальных процессорах Pentium. Загрузка оверлейного сег-

мента происходит под контролем программиста, в то время как распределением

и загрузкой страниц в процессорах Pentium управляет операционная система.

Оверлеи можно считать средством принудительного управления распределени-

ем памяти.

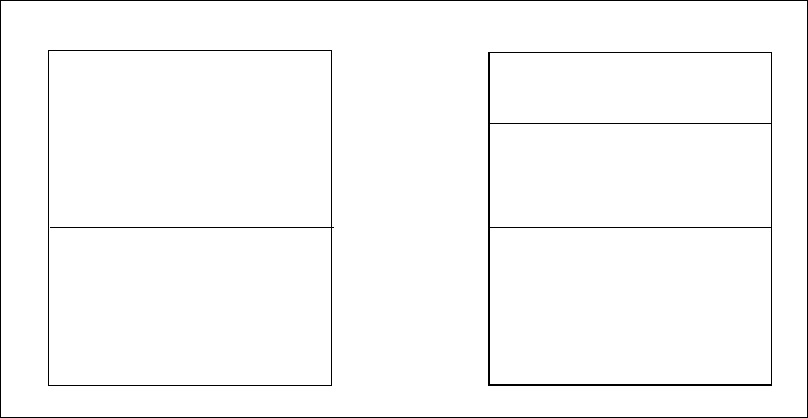

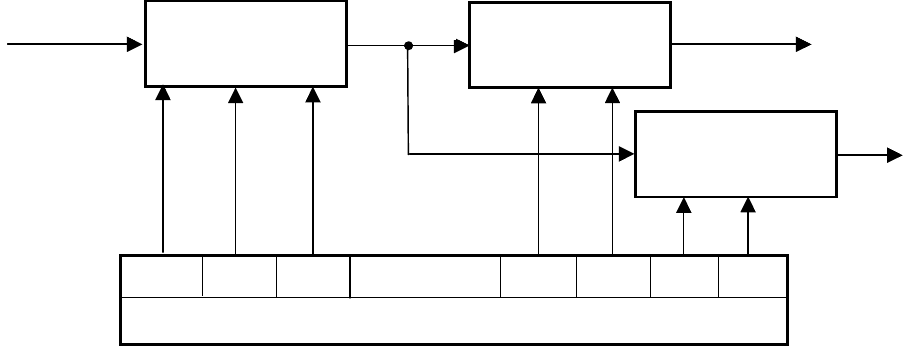

4.2. Последовательный кодек AD73322

Двухканальный кодек AD73322 с последовательным интерфейсом содер-

жит 16-разрядные ЦАП И АЦП в одной микросхеме (рис. 33) и предназначен

для приложений общего применения, включая обработку речи и телефонию.

Каждый канал обеспечивает отношение сигнал/шум 77 дБ во всей полосе рече-

вого сигнала. Усиление каналов АЦП и ЦАП программируется до 38 дБ и 21

дБ соответственно. При частоте внешнего генератора 16,384 МГц кодек форми-

рует сигналы на выходе сигма-дельта АЦП и ЦАП с частотой дискретизации

64 кГц, 32 кГц, 16 кГц и 8 кГц.

Одна из четырех перечисленных частот выбирается программно при на-

чальной инициализации AD73322, когда процессор записывает числа в регист-

ры управления A-H для выбора режима работы и установки параметров кодека.

55

Рис. 33. Кодек AD73322 с последовательным интерфейсом

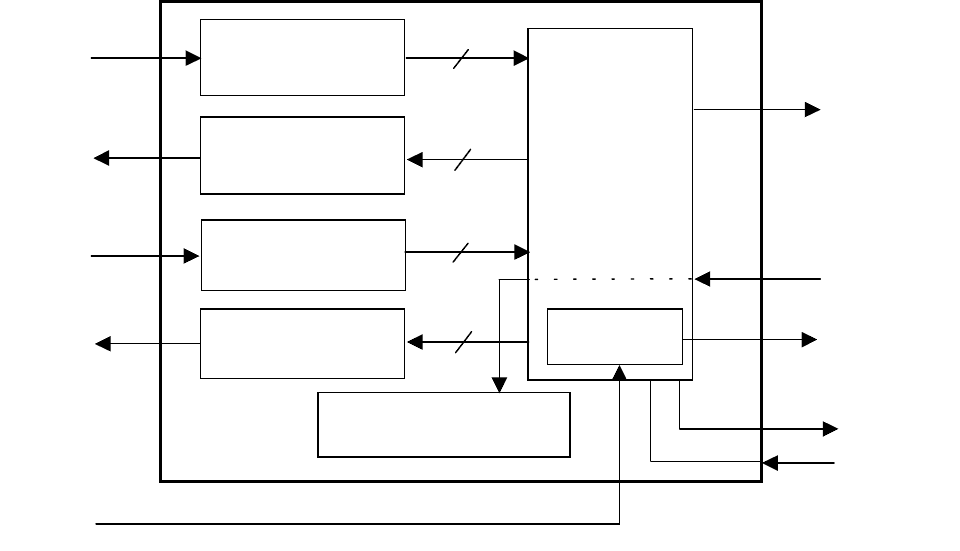

Последовательный интерфейс позволяет подключить одно или несколько

устройств в соответствии с промышленным DSP стандартом, в том числе и сиг-

нальные процессоры семейства ADSP-218х. Схема подключения кодека к про-

цессору и внешнему генератору приведена на рис. 34.

Напряжения аналоговых сигналов Uвх1 и Uвх2, подаваемые на входы

VFBP1 и VFBP2 первого и второго каналов микросхемы кодека AD73322, пре-

образуются с помощью АЦП1 и АЦП2 в пропорциональные 16-разрядные дво-

ичные числа и передаются последовательным кодом с выхода SDO (Serial Data

Output) на вход DR (Data Read) последовательного порта SPORT сигнального

процессора (рис. 35). Промежуток времени, который отводится порту на прием

бита, определяется одним периодом сигнала битовой синхронизации SCLK.

В начале каждого пакета данных из 16 бит кодек формирует импульс кад-

ровой синхронизации SDOFS (SDO Framing Signal), от которого порт процессо-

ра начинает счет поступающих от АЦП бит. Для передачи двух 16-разрядных

слов АЦП первого и второго каналов кодеку необходимо сформировать 32 им-

Кадровая

синхронизация

Внешний

генератор

SCLK

Последова-

тельный выход

Последова-

тельный вход

U

вх1

MCLK

VOUT2

VFBP2

VFBP1

VOUT1

ΣΔ АЦП

Канал 1

ΣΔ ЦАП

Канал 1

ΣΔ АЦП

Канал 2

ΣΔ ЦАП

Канал 2

Последова-

тельный

интерфейс

16

16

16

16

SDO

SDI

U

вх2

U

вых1

U

вых2

Регистры управления

A

,

B

,

C

,

D

,

E

,

F

,

G

,

H

Делитель

частоты

SDOFS

SDIFS

Битовая

синхронизация

56

пульса битовой синхронизации SCLK и 2 импульса кадровой синхронизации

SDOFS. Время передачи двух слов не должно превышать период дискретиза-

ции аналогового сигнала T

S

.

Рис. 34. Внешняя синхронизация приемника и передатчика порта SPORT

Рис. 35. Тактирование сигналов при обмене данными между кодеком и процессором

Аналоговые сигналы

кодека 1

Аналоговые сигналы

кодека 2

10 к

3 B

Кодек

AD73322

Процессор

ADSP

-

2189M

TFS

DT

SCLK

DR

RFS

SDIFS

SDI

SCLK

SDO

SDOFS

SE

Кодек 1

Кодек 2

Генератор

16,384 МГц

МCLK

VFBP1

VOUT2

VFBP2

VOUT1

П

о

р

т

S

P

O

R

T

t

SCLK

SDOFS

SDO

Слово АЦП канала

2

Слово АЦП канала 1

SDIFS

Слово ЦАП канала 2

Слово ЦАП канала 1

SDI

t

t

t

t

57

Одновременно с приемом данных от АЦП процессор передает два 16-

разрядных слова в ЦАП двух каналов кодека. Принятые 32 бита автоматически

записываются в регистр RX0 порта SPORT0 или RX1 порта SPORT1 – в за-

висимости от того, к какому последовательному интерфейсу подключена мик-

росхема AD73322. Формирование сигнала SСLK показано на рис. 36.

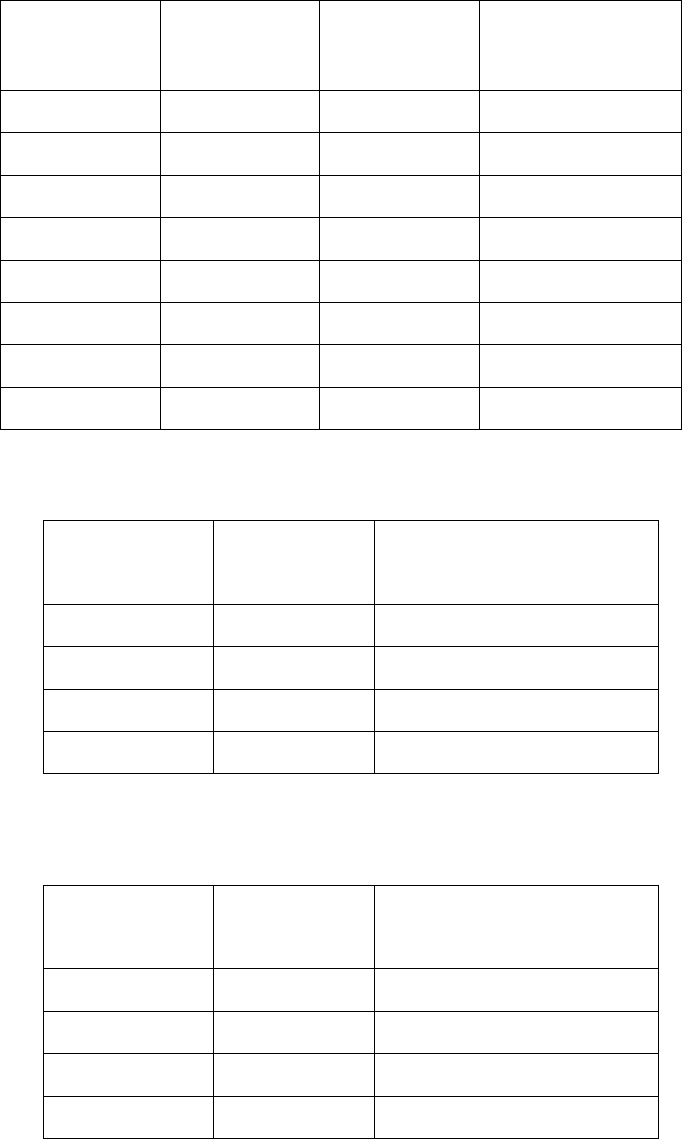

Рис. 36. Программное управление сигналом кодека SСLK

Программируемый делитель частоты внешнего генератора, подключенно-

го ко входу кодека МСLK, может задать один из пяти коэффициентов деления

1, 2, 3, 4 и 5.

Выбор коэффициента деления определяется разрядами 4-6 регистра

управления В при формировании внутреннего сигнала DМСLK (табл. 7). По

умолчанию устанавливается коэффициент деления 1 : 1.

Второй программируемый делитель частоты микросхемы AD73322 опре-

деляет частоту выходного сигнала SСLK с помощью бит 2-3 регистра В (табл.

8). Частота дискретизации аналогового сигнала F

S

определяется битами 0-1

регистра В и может принимать 4 значения: DMCLK/256, DMCLK/512,

DMCLK/1024 и DMCLK/2048 (табл. 9). После включения питания процессора

по умолчанию устанавливается минимальная частота дискретизации

F

S

=DMCLK/2048 = 8 кГц.

Частота

F

S

Делитель частоты

МСLK

МСLK

DМСLK

Делитель 1

частоты DМСLK

SСLK

Регистр управления В

MCD2

MCD1

MCD0

SCD1

SCD0

16,384 МГц

Делитель 2

частоты DМСLK

DIR1

DIR0

Битовая частота

58

Таблица 7. Установка внутренней частоты DMCLK

MCD2

(бит 6)

MCD1

(бит 5)

MCD0

(бит 4)

Коэффициент

деления MCLK

0 0 0 1 : 1

0 0 1 1 : 2

0 1 0 1 : 3

0 1 1 1 : 4

1 0 0 1 : 5

1 0 1 1 : 1

1 1 0 1 : 1

1 1 1 1 : 1

Таблица 8. Программная установка частоты сигнала SCLK

SCD1

( бит 3)

SCD0

( бит 2)

Коэффициент

деления DMCLK

0 0 1 : 8

0 1 1 : 4

1 0 1 : 2

1 1 1 : 1

Таблица 9. Программирование частоты дискретизации F

S

DIR1

( бит 1)

DIR0

( бит 0)

Коэффициент

деления DMCLK

0 0 1 : 2048

0 1 1 : 1024

1 0 1 : 512

1 1 1 : 256

Для передачи двух слов длиной 32 бита в каждом направлении с битовой

частотой F

SCLK

= 2,048 МГц, принятой по умолчанию, необходимо время

15,625 мкс. Это время намного меньше периода дискретизации T

S

= 125 мкс.

59

Частоты кодека, рассмотренные в примере, соответствуют такому состоя-

нию регистра управления В, при котором во всех его разрядах записаны нули.

Обнуление всех управляющих регистров кодека происходит автоматически при

поступлении сигнала низкого уровня на вход сброса RESET. Значения, отлич-

ные от принятых по умолчанию, записываются в программе пользователя при

начальной инициализации. Для этого процессору необходимо передать в кодек

от 8 до 16 управляющих 16-разрядных слов в зависимости от выбираемого ре-

жима кодека.

Частота битовой синхронизации и коэффициенты деления выбираются из

условия: (количество слов) × (размер слова) × F

S

< F

SCLK

. Для схемы подклю-

чения кодека, приведенной на рис. 34, необходимо выполнение неравенства

2 × 16 × F

S

< F

SCLK

. Если при инициализации кодека в программе записать в

регистр управления. В управляющее слово в двоичном коде

1000000100001111, то в младших 7 разрядах будут записана следующая ин-

формация DIR0 = 1 (бит 0), DIR1 = 1 (бит 1), SCD0 = 1 ( бит 2), SCD1 = 1 ( бит

3), MCD0 = 0 (бит 4), MCD1 = 0 (бит 5), MCD2 = 0 (бит 6). Пользуясь таблица-

ми 6, 7, 8 определяем коэффициенты деления и частоту сигналов. F

DMCLK

=

16,384 МГц, F

S

CLK

= 16,384 МГц, F

S

= 16,384/256 = 64 кГц.

4.3. Последовательный интерфейс процессора

Рассмотрим пример подключения кодека к порту SPORT0. Во время

приема и передачи информации последовательным кодом процессор может вы-

полнять программу, не связанную с работой порта по приему и передаче каж-

дого бита. В рассмотренном режиме работы на рис. 34 предполагается, что

процессор должен не пропустить только те моменты времени, когда в регистр

передатчика ТХ порта SPORT нужно записать передаваемое 32-разрядное сло-

во и прочитать из регистра приемника RX принятое 32-разрядное слово. Пре-

образование параллельного кода в последовательный при передаче и последо-

60

вательного кода в параллельный при приеме выполняет аппаратно встроенный

порт SPORT.

К программно доступным регистрам RX0, TX0 порта SPORT0 и RX1,

TX1 порта SPORT1 можно обратиться в любой момент времени. Для чтения

принятого 16-разрядного слова RX0 и записи 16-разрядного слова в передат-

чик TX0 порта SPORT0 достаточно записать две команды

АХ0 = RX0;

TX0 = AY0.

Первая ассемблерная команда записывает в регистр АХ0 число, принятое

последовательным портом из кодека, вторая – записывает в передатчик число

из регистра AY0, которое будет передано портом SPORT0 в кодек. Так как по-

следовательные порты управляются контроллером прерываний, то для обеспе-

чения максимальной производительности процессора указанные ассемблерные

команды должны выполняться в подпрограмме обработки прерываний. Ис-

пользование контроллера прерываний позволяет вводить данные из АЦП в па-

мять процессора и выводить из памяти в ЦАП с постоянным шагом во времени

T

S

.

Программирование последовательного порта можно разбить на две части.

Первый программный блок задает режим работы порта и его параметры, вы-

полняется обычно однократно в начале основной программы при инициализа-

ции устройств, подключенных к процессору (табл. 10). В некоторых слу-

чаях инициализация может проводиться повторно для изменения отдельных

параметров.

Вторая часть содержит подпрограмму обработки прерываний, выполняе-

мую циклически с частотой дискретизации сигналов F

S

. Кроме выполнения

команд ввода-вывода для обмена данными с кодеком она содержит программ-

ный код обработки поступающей информации в реальном времени. Например,

расчет выходного сигнала цифрового фильтра низкой частоты n-го порядка.