Аксенов, В.П. Сигнальные процессоры

Подождите немного. Документ загружается.

31

Адресные генераторы (DAG) вычисляют адреса при пересылке данных из

памяти в регистры и обратно. Генератор DAG1 может выполнять адресацию

только в памяти данных, DAG2 – в памяти данных и в памяти программ. Сек-

венсор управляет ходом выполнения программы. Регистр команд секвен-

сора хранит информацию о выполняемой в данный момент времени команде.

Команды загружаются из памяти программ в регистр команд в одном цикле

процессора и выполняются в следующем цикле, когда одновременно с выпол-

нением выбирается следующая команда программы. Регистр команд образует

одноуровневый конвейер в потоке выполняемых команд. Секвенсор позволяет

организовать цикл в программе без использования команд условного перехода.

Условие завершения цикла процессор выполняет автоматически, контролируя

системный счетчик циклов программы.

Устройство также способно с минимальной задержкой реагировать на

прерывания, поступающие от контроллера прерываний. Появление прерывания

вызывает временную остановку основной программы и переход к ячейке памя-

ти, где хранится подпрограмма обработки прерывания. Для этих целей в табли-

це векторов прерываний зарезервировано четыре ячейки памяти на одно пре-

рывание. Прерывания могут вызываться внешними сигналами, поступающими

на процессор, или циклически через равные интервалы времени, подсчитывае-

мые таймером.

Арифметико-логическое устройство (АЛУ) поддерживает 32-разрядные

арифметические действия. АЛУ обеспечивает стандартный набор арифметиче-

ских и логических функций: сложение, вычитание, инкремент, декремент, по-

лучение абсолютного значения, смену арифметического знака, логическое И,

ИЛИ, исключающее ИЛИ и инверсию. Поддерживаются примитивы деления.

Умножитель-накопитель МАС выполняет умножение со сложением или

умножение с вычитанием за один цикл. Пример такой ассемблерной команды

рассмотрен ранее. Для защиты от переполнения устройство содержит 40-

битный аккумулятор. Дополнительные 8 разрядов допускают возникновение

32

256 переполнений, прежде чем произойдет потеря данных. Если после оконча-

ния выполнения программы установлен флаг MV, то это означает, что регистр

результата содержит слово, длина которого больше 32 разрядов.

Устройство сдвига производит операции логического и арифметического

сдвига, нормализации (преобразование из формата с фиксированной запятой в

формат с плавающей запятой), денормализации (преобразование из формата с

плавающей запятой в формат с фиксированной запятой), вычисления экспонен-

ты.

Два последовательных порта SPORT0 и SPORT1 используются для обме-

на данными с последовательными устройствами. Обычно один из портов под-

ключается через СОМ-порт к компьютеру, другой – с последовательным коде-

ком (АЦП и ЦАП в одной микросхеме). Оба порта поддерживают обмен дан-

ными в последовательном коде словами длиной от 3 до 16 бит и обеспечивают

логарифмическое сжатие данных по А-закону или μ-закону в соответствии с

рекомендацией G.711.

Программируемый таймер генерирует периодические прерывания с по-

мощью 16-битного счетчика TCOUNT. Содержимое счетчика уменьшается на

единицу в каждом цикле процессора. Когда счетчик обнуляется, генерируется

прерывание и в него записывается начальное значение из 16-разрядного реги-

стра TPERIOD.

Микропроцессор содержит внутренний порт прямого доступа к памяти

(ПДП) и байтовый порт ПДП, которые обеспечивают быстрый обмен с памя-

тью. Внутренний порт ПДП поддерживает обмен с памятью программ, байто-

вый порт позволяет записывать и читать как команды, так и данные. Порт ин-

терфейса с хост-процессором обеспечивает подключение процессоров данного

семейства или других микропроцессоров без дополнительных интерфейсных

схем.

Напряжение питания ядра процессора 2.5В, напряжение на внешних вы-

водах портов ввода-вывода должно быть равным 2.5В или 3.3В. Мощность, по-

33

требляемая от источника питания, достигает максимума 90мВТ при выполне-

нии процессором программы из встроенной памяти и не превышает 1 мВТ в

режиме пониженного энергопотребления. Переход в «спящий» режим может

осуществляться аппаратно или программно.

Структура процессора ориентирована на выполнение наиболее часто

встречающихся операций при цифровой обработке за один цикл. Типовой опе-

рацией различных алгоритмов цифровых процессоров обработки сигналов яв-

ляется суммирование произведений. Для этого процессору необходимо извлечь

из памяти два операнда (например, коэффициент фильтра и один отсчет масси-

ва данных), перемножить их и суммировать результат с предыдущим произве-

дением.

При обращении к отдельному устройству в программах на языке ассемб-

лера используется одна или несколько переменных, хранящихся в регистрах

процессора. Имя регистра определяет не только конкретное устройство, но и

закрепленную за ним функцию. В генераторах адреса DAG1 и DAG2 четыре

индексных регистра I содержат адреса ячеек памяти, регистры М – шаг увели-

чения адреса, L – длину циклического буфера.

Данные, поступающие на входы АЛУ и МАС для выполнения арифмети-

ческих или логических операций, должны храниться в одном или нескольких

регистрах АХ0, АХ1, МХ0, МХ1, АY0, АY1, МY0, МY1. Результат выполнен-

ной операции хранится в регистрах AR, AF, MR, MF. Признаки результата опе-

рации, выполненной АЛУ и МАС, процессор автоматически заносит в регистр

ASTAT (табл. 2). Процессор установит бит AZ (AZ=1), если результат нулевой,

и сбросит бит (AZ=0) в противном случае. Бит AN=1, если после выполнения

текущей команды получено отрицательное число. Бит MV устанавливается в

том случае, если произошло переполнение 40-разрядного числа МАС.

Регистр режима работы MSTAT содержит 4 бита управления переключе-

нием регистров вычислительных блоков, бит-реверсивной адресацией генера-

34

тора DAG1 и насыщением АЛУ. Остальные 3 бита управляют размещением ре-

зультата в блоке МАС, таймером и запуском процессора.

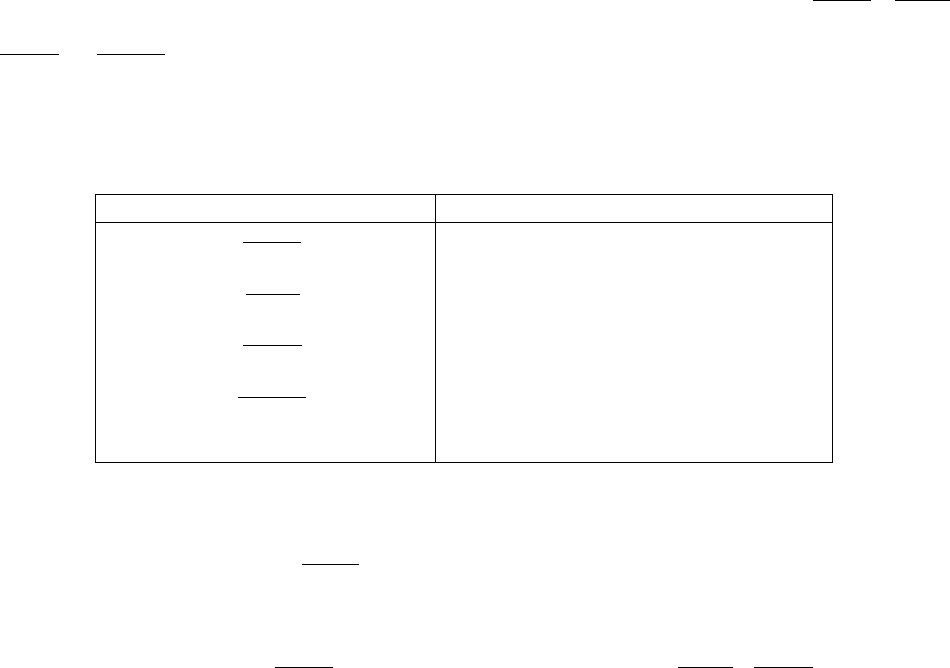

Таблица 2. Переменные регистра ASTAT

Стек счетчика COUNT содержит переменную CNTR для организации

цикла без указания в программе условия его завершения. Необходимо лишь за-

дать начальное значение счетчика CNTR, например, CNTR=10. Каждый цикл

программы автоматически уменьшает содержимое счетчика на единицу. После

10 циклов, когда счетчик обнулится, процессор продолжит линейное выпол-

нение программы.

В систему команд процессора входят многофункциональные команды,

использующие параллельное выполнение действий различными блоками. При-

мером такого типа команд является следующая инструкция, которая выполня-

ется за один цикл

MR=MR+MX0*MY0(SS), MX0=DM(I0,M0), MY0=PM(I4,M5);

Первая часть команды (до первой запятой) помещает в регистр результата MR

блока МАС сумму предыдущего значения регистра и произведение текущих

значений входных регистров Х и Y (МХ0 и МY0), данные в которых восприни-

маются процессором как числа со знаком SS, где S – первая буква слова sign

(знак). Во второй и третьей части команды процессор читает из памяти два но-

вых операнда и запоминает их в регистрах МХ0 и МY0. В регистр МХ0 зано-

сится значение из ячейки памяти данных (DM) с номером I0, в регистр МY0 –

из ячейки памяти программ (РМ) с номером I4. После записи чисел в регистры

значение переменной I0 увеличивается на М0, а I4 соответственно – на М5.

Биты ASTAT 7 6 5 4 3 2 1 0

Имя SS MV AQ AS AC AV AN AZ

переменной

35

3.2. Режимы работы микросхемы ADSP-2189M

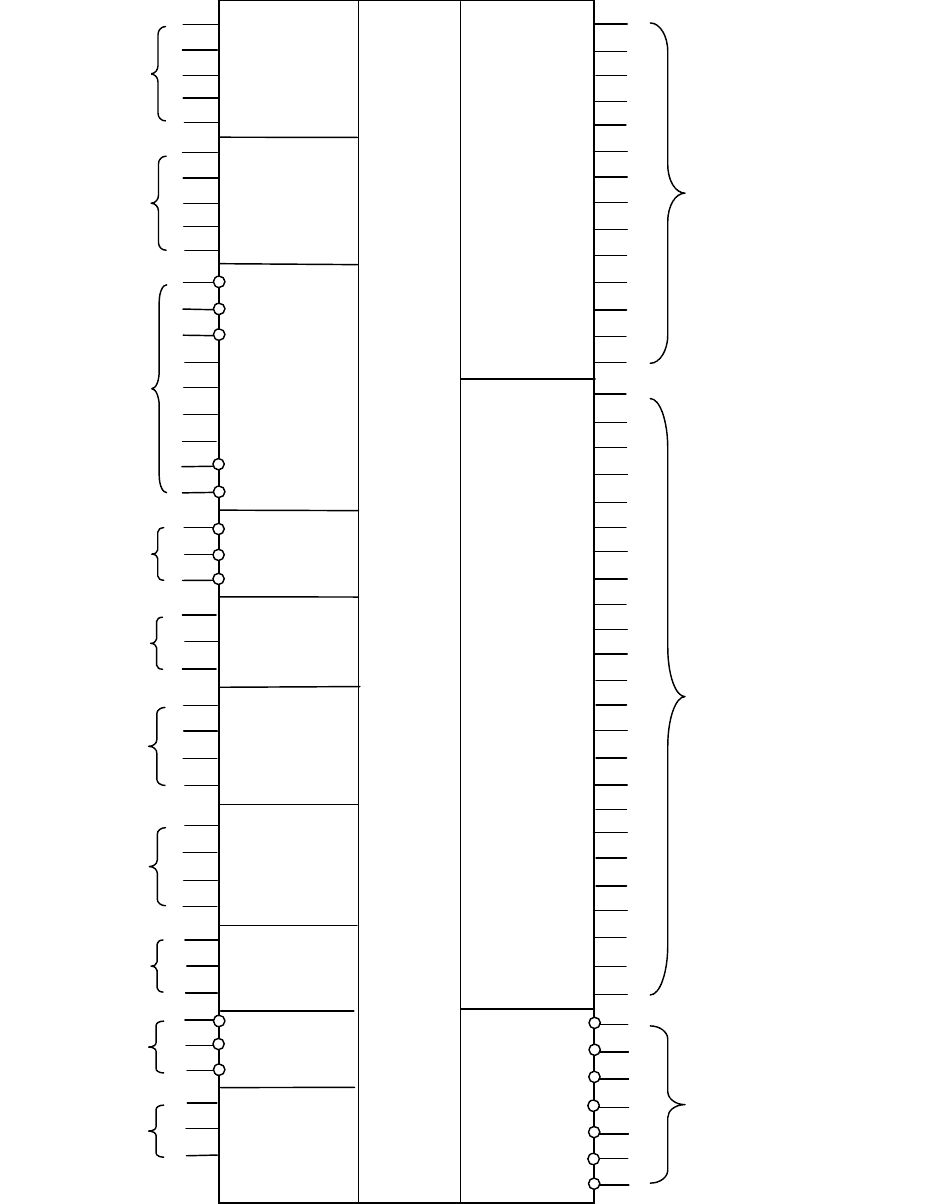

Выводы микросхемы ADSP-2189M (рис. 20), образующие системный ин-

терфейс, позволяют подключать к процессору микросхемы внешней памяти с

учетом модифицированной Гарвардской архитектуры, а также порты вво-

да/вывода для обмена данными с внешними устройствами. Сигнальный про-

цессор может работать в одном из двух вариантов организации памяти – пол-

ном и хост-режиме. Назначение сигналов микросхемы процессора определяется

выбранным режимом работы. Во время выполнения программы процессор мо-

жет поочередно обращаться к четырем различным областям внешней памяти с

помощью индивидуальных выходных сигналов шины управления

BMS

,

PMS

,

DMS

и

IOMS

(табл. 3).

Таблица 3. Сигналы шины управления процессора для внешней памяти

Выходной сигнал процессора

Область внешней

памяти

BMS

PMS

DMS

IOMS

Байтовая память

Память программ (оверлейная)

Память данных (оверлейная)

Порты ввода/вывода

При совместном использовании нескольких областей процессор дополни-

тельно выводит сигнал

CMS

. Например, если в оверлейной памяти размером

32 килослова необходимо хранить программы и данные, то процессор форми-

рует выходной сигнал

CMS

. Индивидуальные сигналы

PMS

,

DMS

в этом слу-

чае используются как дополнительные адресные сигналы для внешней микро-

схемы памяти оверлея, которые определяют область программ и область дан-

ных соответственно. В зависимости от типа выполняемой процессором коман-

ды на выводах микросхемы ADSP-2189 формируются активные низкие уровни

36

Рис. 20. Выводы микросхемы ADSP-2189M в корпусе LQFP100

SCLK0

RFS0

TFS0

DT0

DR0

SCLK1

RFS1

TFS1

DT1

DR1

EBG

EBR

EINT

ELIN

ELOUT

ECLK

EE

EMS

ERESET

RESET

PWDACK

PWD

DSP

ADSP

2189M

A13/IAD12

A12/IAD11

A11/IAD10

A10/IAD9

A9/IAD8

A8/IAD7

A7/IAD6

A6/IAD5

A5/IAD4

A4/IAD3

A3/IAD2

A2/IAD1

A1/IAD0

A0

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7/IWR

D6/IRD

D5/IAL

D4/IS

D3/IACK

D2/IAD15

D1/IAD14

D0/IAD13

WR

RD

CMS

IOMS

BMS

DMS

PMS

XTAL

CLKIN

CLKOUT

IRQ2/PF7

IRQL1/PF6

IRQL0/PF5

IRQE/PF4

MODE_D/PF3

MODE_C/PF2

MODE_B/PF1

MODE_A/PF0

BR

BGH

BG

VDDEXT

VDDINT

GND

Шина адреса/данных

Шина данных

Шина управле-

ния

Последова-

тельный порт

SPORT0

Последова-

тельный порт

SPORT1

Порт

эмулятора

EZ-ICE

Шина

управления

Тактовый

генератор

Внешние

прерывания/

двунаправ-

ленный порт

Выходной

порт флагов

Шина

управления

Источники

питания

Режим рабо-

ты процессо-

ра/двунаправл

енный порт

FL2

FL1

FL0

63

11

10

9

8

7

6

5

4

2

1

100

99

98

97

84

83

82

81

79

78

77

76

75

74

73

72

70

69

68

65

64

62

61

58

57

56

55

19

20

25

24

21

22

23

35

33

32

31

34

42

39

38

37

40

53

51

50

49

48

47

46

45

43

44

96

91

14

13

16

30

29

27

26

88

89

93

94

52

95

54

36

18

3

85

86

87

37

CMS

,

PMS

при обращении к внешней памяти программ или

CMS

,

DMS

при

обращении к внешней памяти данных. С помощью сигнала шины управления в

микропроцессорной системе можно организовать любую комбинацию совмест-

ного использования четырех областей – байтовой памяти, памяти программ,

памяти данных и портов ввода-вывода. Количество используемых областей

определяется программно в регистре 0x3FE6 при начальной инициализации

системных переменных и должно соответствовать применяемой электрической

схеме.

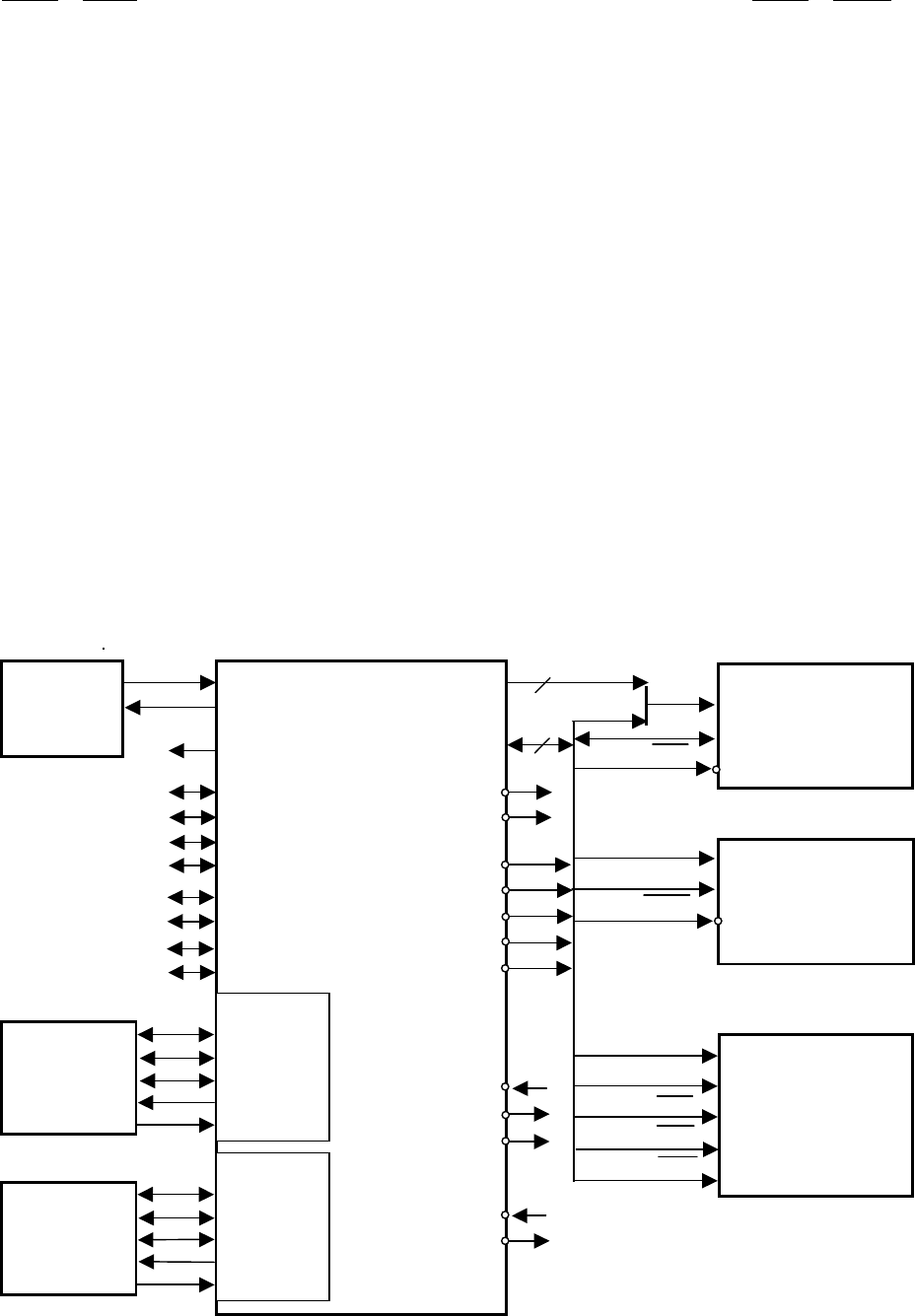

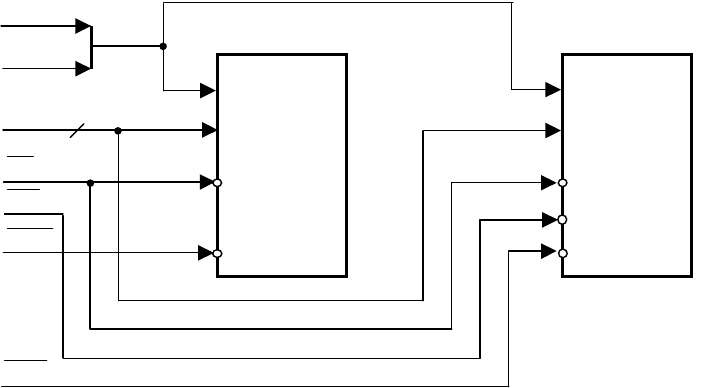

Сигнальный процессор может работать в одном из двух вариантов орга-

низации памяти – полном и хост-режиме. Выбор варианта определяется со-

стоянием сигнала MODE C на входе процессора во время сброса системы. В

полном режиме (Full Memory Mode) максимально используются внешние шины

данных и адреса микросхемы (рис. 21). Внутренний порт прямого доступа к па-

Рис. 21. Полный режим работы процессора (MODE C = 0)

D23:8

D15:8

D23:16

Генератор

½х или

резонатор

CLKIN

XTAL

FL0: 2

IRQ2/PF7

IRQL1/PF6

7

IRQL0/PF5

7

IRQE/PF4

MODE D/PF3

MODE C/PF2

MODE B/PF1

MODE A/PF0

SPORT

SCLK0

RFS0

TFS0

DT0

DR0

SPORT

SCLK1

RFS1/IRQ0

TFS1/IRQ1

DT1/FI

DR1/FO

Последо-

вательное

устройство

Последо-

вательное

устройство

А13

:

0

14

D23 : 0

24

WR

RD

BMS

IOMS

PMS

DMS

CMS

Байтовая

память

A21 : 0

ADDR

DATA

CS

BMS

ADDR

A10:0

DATA

CS

IOMS

Порты

ввода/

выв

о

да

ADDR

DATA

PMS

DMS

CMS

Оверлейна

я

память

2×8к

сегменты РМ

2×8к

сегменты DМ

А13

:

0

D23:0

BR

BG

BGH

PWD

PWDACK

38

мяти IDMA в этом случае не доступен. Подключение внешних микросхем па-

мяти и портов ввода-вывода выполняется с помощью 24-разрядной шины дан-

ных D23:0, 14-разрядной шины адреса А13:0, 5 сигналов выбора области па-

мяти

PMS

,

DMS

,

BMS

,

IOMS

,

CMS

.

Микросхемы памяти с байтовой шиной данных подключаются к процес-

сору через байтовый порт прямого доступа BDMA (рис. 22) с 22-разрядной

шиной адреса, обеспечивающей работу микросхем памяти общей емкостью до

4 Мбайт. Кроме сигналов A13:0 для увеличения разрядности адресной шины

дополнительно используются 8 бит шины данных D23:16. Контроллер байто-

вого обмена поддерживает 8- и 16-разрядный формат слов при обращении к

памяти данных, а также 24-разрядную организацию слов внутренней памяти

программ ADSP2189M.

Рис. 22. Порт прямого доступа к памяти BDMA

Контроллер BDMA выполняет начальную загрузку программы в процес-

сор из микросхемы внешней памяти и ее запуск. Обмен данными между внеш-

ней и внутренней памятью процессора может происходить в фоновом режиме

во время выполнения основной программы. Регистр BIAD используется для за-

дания начального адреса блока внутренней процессорной памяти, участвующе-

го в обмене. Стартовый адрес внешней памяти хранится в регистре BEAD. Ко-

BMS

RD

Ш

ина

адреса

22

A13

:

0

14

D23

:

16

8

D15:8

8

Шина

данных

A21

:

0

D7

:

0

CS

WR

OE

WE

Выбор кристалла

Чтение

Запись

Байтовая

память

4М

×8

ADSP2189M

39

личество передаваемых слов одного блока записывается в регистр BWCOUNT

перед началом обмена. Содержимое этого счетчика автоматически уменьшает-

ся на единицу после каждого переданного слова. Контроллер прямого доступа

к памяти заканчивает обмен при обнулении регистра-счетчика BWCOUNT и

вырабатывает сигнал прерывания.

Внешняя байтовая память может состоять из микросхем ПЗУ и ОЗУ, в

которых хранятся программы и данные. Обмен через порт прямого доступа

BDMA происходит с помощью слов выбранного формата (от 8 до 24 бит ) и

страниц фиксированного размера. Байтовая память состоит из 256 страниц,

каждая из которых имеет емкость 16к × 8 бит. Адресные сигналы процессора

D23:16 определяют номер страницы, сигналы A13:0 - номер ячейки внешней

памяти в пределах выбранной страницы. Номер страницы, формат данных, на-

правление обмена, разрешение работы процессора во время прямого доступа к

памяти – эти параметры устанавливаются отдельными битами в регистре

управления BDMA Control.

Рис. 23. Подключение к процессору микросхем памяти ПЗУ и ОЗУ

Если в микропроцессорной системе применяются внешние микросхемы

постоянной и оперативной памяти, то сигнал шины управления сигнального

CMS

ПЗУ

Запись

WR

Чтение

Адрес

ОЗУ или FLASH

D23

:

16

A13

:

0

A22

:

0

A22

:

0

D15

:

8

Данные

D7

:

0

D7

:

0

RD

OE

OE

WE

CS

BMS

CS

8

40

процессора BMS подается на вход выбора кристалла

CS

ПЗУ, сигнал

CMS

–

на вход

CS

ОЗУ (рис. 23). Тем самым обеспечивается непосредственное со-

единение микросхем памяти и процессора без дополнительных микросхем де-

шифрации адреса, необходимых в универсальных процессорах.

Системный интерфейс допускает управление шинами со стороны внеш-

него устройства. Когда периферийное устройство формирует импульс запроса

BR

на прямой доступ к внутренней памяти процессора, то в следующем ко-

мандном цикле шина данных, адреса и семь выводов шины управления

PMS

,

DMS

,

BMS

,

CMS

,

IOMS

,

RD

,

WR

переводятся в высокоомное Z-состояние,

если они не были заняты в это время обменом с внешней памятью. Затем про-

цессор вырабатывает ответный сигнал подтверждения

BG

, информирующий

запросившее устройство о том, что шины освобождены, и останавливает вы-

полнение программы на время обмена.

Последовательные порты SPORT0 и SPORT1 обеспечивают подключение

сигнального процессора к большинству стандартных последовательных уст-

ройств. Они поддерживают передачу данных словами от 3 до 16 бит и аппарат-

ное сжатие информации с помощью А- или μ-закона компандирования. Порт

SPORT0 может также работать в режиме многоканальной передачи данных 24-

или 32-разрядными словами при обмене с последовательными ЦАП и АЦП.

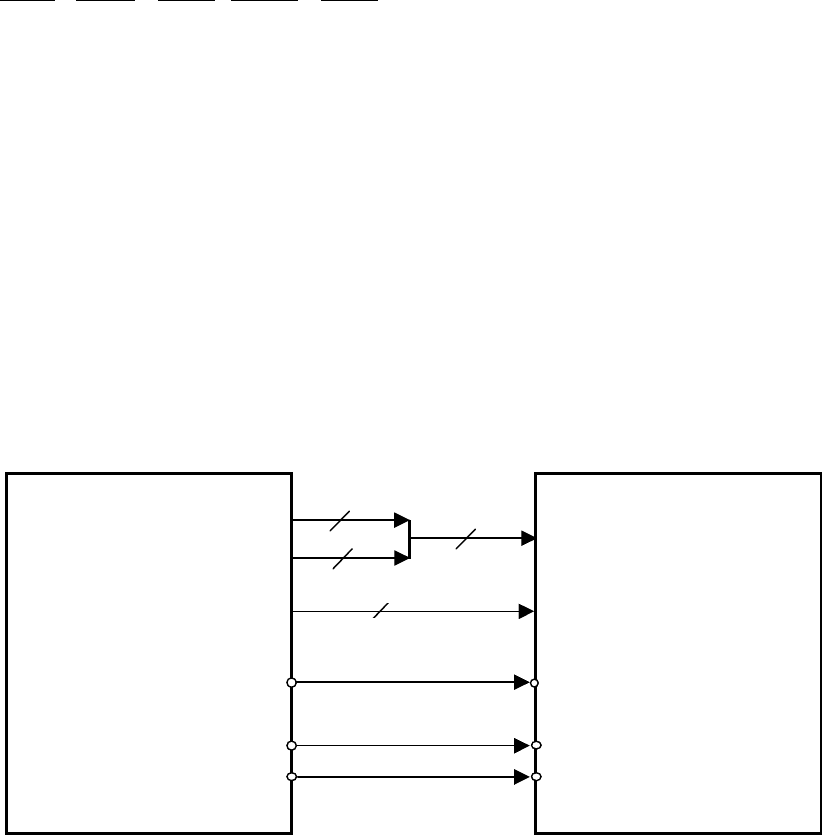

Для уменьшения количества выводов и размеров корпуса микросхемы

некоторые сигналы процессора мультиплексируются. Два последовательных

порта, внешние прерывания, шины адреса, данных и управления используют

выводы микросхемы ADSP-2189M, назначение которых меняется в различных

режимах работы процессора (рис. 24).

В полном режиме входной сигнал управления MODE C равен нулю,

через выводы мультиплексора проходят адресные сигналы A13:0 и три млад-

ших разряда шины данных D2:0. Противоположный уровень управляющего

сигнала MODE C = 1 пропускает через мультиплексор другую группу сигналов

– IAD 15:0.