Кагиров Р.Р. Лекции по Организации ЭВМ

Подождите немного. Документ загружается.

имели адресную шину шириной 32 бит и адресовали 4 гигабайта физической

памяти. Шина адреса также является параллельной, то есть увеличение ее

разрядности влечет увеличение числа адресных выводов процессора. Так, в

процессоре Pentium 4 адресная шина 36-разрядная, что позволило расширить

адресуемую память до 64 Гигабайт.

Третья группа сигналов, необходимая процессору для работы, относится

к служебным. С их помощью чипсет и процессор обмениваются командами и

запросами, по служебной шине осуществляется тактирование и синхронизация

процессора, управление напряжением питания. Число сигналов управления и,

соответственно, количество выводов разъема, необходимое для обмена

служебными сигналами, зависит от архитектуры процессора и чипсета,

количества поддерживаемых команд и инструкций. С усложнением

архитектуры число служебных линий и сигналов управления увеличивается.

Так, процессор i286 имел 18 выводов служебной шины, а процессор Pentium —

уже 83.

Подсчитаем число задействованных выводов для перечисленных выше

магистралей системной шины современного процессора, например Pentium 4

520:

36 для адресной шины;

64 для шины данных;

124 для служебной шины.

Остальные выводы в разъеме Socket 775 процессора Pentium 4

резервируются (например, 28 выводов в процессоре Pentium 4 520) или

используются для подачи питания. Эти выводы на принципиальных схемах

обычно называются VQC (плюс питания), Vss (земля) и VTT (терминаторы).

Так, в разъеме Socket 775 выводов VQC — 226 штук, выводов VTT— 24.

выводов Vss — 273.

С расширением разрядности ядра процессоров до 64 бит, с внедрением

двухъядерных архитектур и повышением рабочих частот будет расти число

выводов процессора и магистралей системной шины. Преодоление этой

тенденции возможно только с переходом на последовательные интерфейсы.

91

Шина HyperTransport

Высокоскоростной последовательный интерфейс HyperTransport

предназначен для использования в качестве внутренней шины персонального

компьютера, в том числе для соединения процессоров с прочими

компонентами, то есть в качестве системной шины.

Основным идеологом и разработчиком интерфейса HyperTransport

выступила компания AMD. Позднее был образован консорциум HyperTransport,

который утвердил спецификации шины HyperTransport версии 1.0.

Первоначально шина использовалась в платформах для процессоров AMD

Athlon и VIA C3 в качестве магистрали соединения северного и южного мостов

наборов микросхем системной логики. С появлением процессоров AMD Athlon

64./FX и AMD Opteron шина HyperTransport стала системной в платформах для

этих процессоров. Развитие архитектуры многоядерных процессоров

поддержано утверждением спецификации HyperTransport 2.0, рассчитанной на

возросшие тактовые частоты и возможность сопряжения (mapping) с хост-

адаптерами для шины PCI Express. Согласно спецификациям, шина

HyperTransport 2.0 может работать на тактовой частоте до 1,4 ГГц.

Передача информации осуществляется на обоих фронтах тактового

сигнала, то есть эффективная частота шины вдвое больше физической.

Максимальная пропускная способность в обоих направлениях достигает 22,4

Гбайт/с, что с лихвой покрывает потребности многопроцессорных

двухъядерных систем. По электрическим спецификациям шина HyperTransport

2.0 обратно совместима с первой версией.

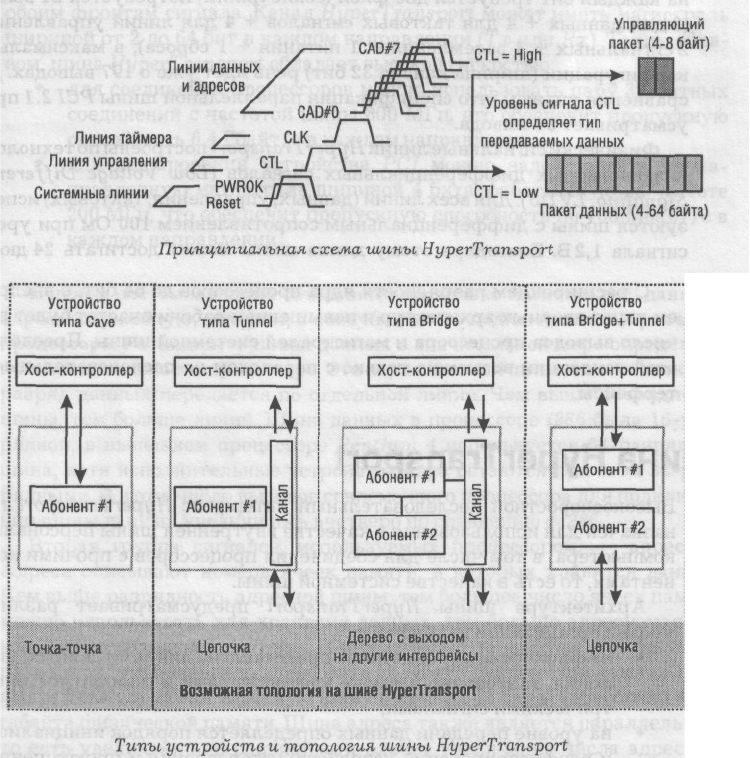

Архитектура шины HyperTransport предусматривает различные уровни

организации интерфейса:

на физическом уровне шина представлена линиями данных, управления,

тактовыми, а также контроллерами и стандартными электрическими

сигналами;

на уровне передачи данных определяется порядок инициализации и

конфигурирования устройств, установления и прекращения сеанса связи,

циклического контроля адекватности данных, выделения пакетов для

передачи данных;

на уровне протокола определены команды для выделения виртуальных

каналов связи, правила управления потоком данных;

на уровне транзакций команды протокола конкретизированы в

управляющие сигналы, например чтения или записи;

на уровне сессии определены правила управления энергопотреблением и

прочие команды общего характера.

92

Физические устройства в рамках интерфейса HyperTransport подразделяются

на несколько типов:

Host («контроллер шины») — основное устройство, полностью

реализующее все функции интерфейса;

Cave («ячейка») — оконечное устройство на двунаправленном ка¬

нале связи;

Tunnel («тоннель») — устройство на двунаправленном канале связи,

установленное «на проходе» (но не мост);

Bridge («мост») -- устройство на двунаправленном канале связи, один из

абонентов которого считается главным и связывает устройство с

контроллером шины (Host), а другие соединяют с прочими устройствами.

Таким образом, топологию совокупности устройств на шине

HyperTransport можно построить в виде цепочки или дерева. Спецификации

шины предусматривают ее масштабируемость в зависимости от решаемых

задач. В минимальной конфигурации (ширина канала 2 бит, на каждый бит

требуется две физические линии) потребуется 24 вывода (8 для данных + 4 для

тактовых сигналов + 4 для линий управления + 2 сигнальных + 4 заземления + 1

питания + 1 сброса), в максимальной конфигурации (ширина канала 32 бит)

речь идет уже о 197 выводах. Для сравнения укажем, что спецификация

параллельной шины PCI 2.1 предусматривает 84 вывода.

93

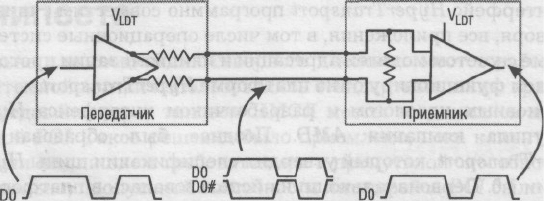

Физически сигнальные линии HyperTransport построены по технологии

низковольтных дифференциальных сигналов (Low Voltage Differential Signaling,

LVDS).

Для всех линий (данных, управления, тактовых) используются шины с

дифференциальным сопротивлением 100 Ом при уровне сигнала 1,2В.

Благодаря этому длина шины может достигать 24 дюйма (около 61 см) при

полосе пропускания на одной физической линии до 800 Мбит/с.

Следует заметить, что спецификация HyperTransport предусматривает

разделение «восходящих» (Upstream) и «нисходящих» (Downstream) потоков

данных. Такой подход обеспечивает возможность существенного увеличения

тактовых частот по сравнению с существующими архитектурами, поскольку

каждый сигнал LVDS функционирует в пределах своей физической линии.

Кроме того, пакет, объединяющий адреса, команды и данные, всегда кратен 32

бит. Тем самым обеспечивается его безошибочная передача по

масштабируемым каналам шириной от 2 до 32 бит. Это позволяет применять

единую технологию HyperTransport для соединения потребителей ресурсов

шины различной производительности: процессор, оперативная память,

видеоконтроллер низкоскоростные устройства ввода-вывода — используя в

каждом случае лишь необходимое число линий.

Устройства, поддерживающие протокол HyperTransport (процессоры,

наборы системной логики, контроллеры) соединены по принципу «точка-

точка» (peer-to-peer). Поэтому теоретически можно соединять между собой

любые компоненты системы без применения каких-либо коммутаторов или

мостов. Каждый канал состоит из линии «передачи» (Тх) и линии «получения»

(Roc), работающих асинхронно. Передача данных организована в виде пакетов

длиной до 64 байт (значение должно быть кратно четырем). Протокол

HyperTransport предполагает передачу данных по обоим фронтам сигнала.

Канал HyperTransport может иметь магистраль шириной от 2 до 64 бит в

каждом направлении (Тх или Rx). Таким образом, шина HyperTransport

обладает высокой гибкостью:

для соединения процессоров можно использовать пару 32-битных

соединений с частотой шины 800 МГц, что обеспечит пропускную

способность 6,4 Гбайт/с в каждом направлении;

для подключения устройства PCI можно задействовать двунаправленную

магистраль шириной 4 бита, работающую на частоте 200 МГц, что

обеспечит пропускную способность по 100 Мбайт/с в каждом

направлении.

94

Интерфейс HyperTransport программно совместим с шиной PCI, иначе

говоря, все приложения, в том числе операционные системы, разработанные с

учетом моделей адресации и инициализации протокола PCI, без проблем

функционируют на платформе HyperTransport.

95

Шина чипсета

Изначально для соединения северного и южного мостов набора

микросхем системной логики использовались стандартные шины архитектуры

ПК. До недавних пор в типовом НМСЛ мосты соединялись параллельной

шиной PCI. Такое решение было приемлемо, пока клиенты южного моста были

не слишком требовательны к пропускной способности шины. Действительно,

пропускной способности интерфейса PCI было достаточно для обслуживания

устройств ввода-вывода на портах COM, LPT, IrDA, PS/2, MIDI, накопителей

IDE/ATAPI спецификации АТА-66/100 и карт расширения с шинами ISA или

PCI. Однако с ростом производительности клиентов, подключенных к южному

мосту, с появлением высокоскоростных интерфейсов ввода-вывода,

возможности шины PCI перестали удовлетворять современным требованиям.

Среди требовательных к ресурсам клиентов южного моста отметим

следующие:

интерфейс Serial ATA (150 Мбайт/с на канал) или Serial ATA2 (300

Мбайт/с на канал);

интерфейс PCI Express (200 Мбайт/с на канал);

шина PCI (133 Мбайт/с);

интерфейс IDE (до 133 Мбайт/с);

шина Gigabit Ethernet (около 128 Мбайт/с);

интерфейс USB 2.0 (около 60 Мбайт/с);

интерфейс FireWire (около 50 Мбайт/с).

Теоретически можно предположить одновременное обращение к

ресурсам процессора и памяти (то есть к северному мосту) пары RAID-

накопителей, устройства PCI Express и клиента локальной сети, что дает

пиковый трафик около 1 Гбайт/с. Таким образом, мостовая шина должна

обеспечить не меньшую пропускную способность.

Исходя из этих требований, ведущие разработчики чипсетов применяют

самые скоростные шины для связи мостов НМСЛ:

компания Intel в современных НМСЛ использует вариант

последо¬вательной шины PCI Express под названием Digital Media

Interface с пропускной способностью до 2048 Мбайт/с;

компания nVidia использует последовательную шину HyperTransport в

интегрированных НМСЛ для платформы AMD Athlon 64, туже шину

используют компании ATI и ULi в своих дискретных чипсетах

(пропускная способность до 2048 Мбайт/с);

компания SiS предпочитает использовать шину MuTIOL с пропускной

способностью 1066 Мбайт/с;

компания VIA до сих пор применяет параллельную шину V-Link с

пропускной способностью 533 Мбайт/с.

Таким образом, возможности межмостовой шины в различных вариантах

различаются примерно в четыре раза. Очевидно, что при построении

96

современной платформы следует ориентироваться на перспективные решения,

то есть последовательные шины DMI или HyperTransport.

97

Шина ISA/EISA

Архитектура ISA (Industry Standard Architecture) — архитектура

промышленного стандарта, другое название AT-Bus. Шина ISA с разрядностью

данных 8 бит (разрядность адреса 20 бит) впервые появилась на платформе PC

XT. На платформе PC AT разрядность шины данных расширили до 16 бит

(разрядность адреса 24 бита). На современных платформах этот интерфейс либо

отсутствует, либо представлен внутренними шинами, обеспечивающими

совместимость с устаревшими компонентами. Разъем шины состоит из двух

частей: 62-контактного (ISA-8) и примыкающего к нему 36-контактного

сегментов (ISА-16). Шина обеспечивает устройствам возможность отображения

регистров в пространстве памяти и адресов ввода-вывода. В распоряжение

устройств на шине ISA выделяется до 11 линий запросов прерываний (в

варианте ISА-16) и до шести каналов прямого доступа к памяти. Пиковая

пропускная способность шины не превышает 5,55 Мбайт/с.

Спецификации ISA предусматривают выделение каждому устройству на

шине своих системных ресурсов: области адресов в пространстве памяти, в

регистрах ввода-вывода, линий запроса прерываний, каналов прямого доступа к

памяти. При этом автоматический арбитраж не предусмотрен, то есть

устройства не должны конфликтовать по ресурсам. Задача арбитража

возлагается на пользователя, а ее выполнение усложняется отсутствием

механизма передачи параметров устройств системному и прикладному

программному обеспечению. Конфигурирование устройств ISA производится

перемычками (джамперами). На шине все сигналы со всех слотов соединяются

параллельно, а никакого буфера для хранения информации о конфигурации не

предусмотрено.

В 1994 г. была разработана спецификация ISA Plug and Play version l.0a,

которая решила самые важные проблемы конфигурирования устройств на шине

ISA. Процедура конфигурирования имеет несколько этапов:

происходит блокировка всех устройств, кроме текущего;

текущему устройству назначается идентификатор Card Select Number,

в буфер BIOS записываются данные о поддерживаемых текущим

устройством ресурсах;

активным становится следующее устройство, а остальные блоки¬руются,

процедура повторяется для всех устройств;

по завершении опроса всех устройств происходит арбитраж ресурсов;

каждое устройство конфигурируется в соответствии с выделенными

ресурсами и становится активным.

Описанная технология поддерживается РпР BIOS системной платы и

выполняется в период процедуры POST. Параметры конфигурации для всех

типов устройств (не только шины ISA) в формате ESCD (Extended System

Configuration Data — расширенные данные системной конфигу¬рации)

хранятся в энергонезависимой памяти. Если BIOS не поддерживает

спецификацию РпР ISA, конфигурирование возлагается на операционную

систему.

98

EISA (Enhanced ISA) — расширенная шина ISA. Является расширением

интерфейса ISA. В разъемы можно вставлять как платы для шины ISA, так и

для EISA. Платы EISA имеют более высокую ножевую часть разъема с

дополнительными рядами контактов, а слот имеет расположенный в глубине

такой же ряд дополнительных контактов. Пиковая пропускная способность —

32 Мбайт/с. Поддерживает режим управления шиной со стороны любого из

устройств, установленных в разъем (технология Bus Mastering). На

современных системных платах не встречается.

99

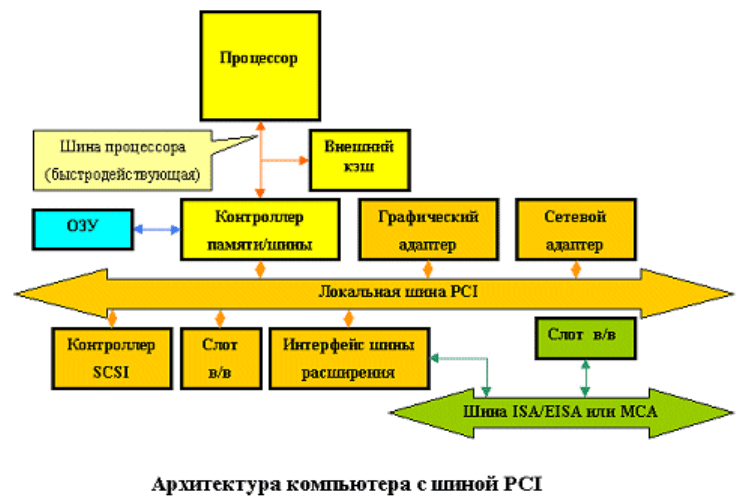

Шина PCI

Зарождение интерфейса происходило весной 1991 г. в недрах корпорации

Intel. Перспективные процессоры 80486 и Pentium требовали новой

организации взаимодействия с периферийными компонентами. Инженеры Intel

решили начать с нуля и в результате разработали шину PCI (Peripheral

Component Interconnect) local bus — шину соединения периферийных

компонентов, напрямую не связанную с системной. Так удалось обеспечить

независимость интерфейса от конкретного типа процессора. Новый интерфейс

оказался не совместимым ни с одним из предшествующих и потребовал

разработки соответствующего набора системных микросхем. С целью

обеспечить поддержку сторонних производителей Intel сделала архитектуру и

спецификации PCI открытыми, поэтому вскоре образовалась группа

заинтересованных организаций (PCI Special Interest Group), создавшая и

утвердившая все спецификации. В настоящее время действует спецификация

PCI 2.2 (утверждена в декабре 1998 г.). Шина РСI является синхронной —

регистрация сигналов выполняется по положительному фронту тактовых

импульсов.

Популярность PCI объясняется рядом преимуществ, предоставляемых

интерфейсом по сравнению с его предшественниками. Во-первых,

поддерживается синхронный обмен данными формата 32 или 64 бита. При этом

используется метод мультиплексирования (передача адресов и данных по

очереди по одним линиям), что позволило снизить число контактов в разъемах.

Во-вторых, предусмотрена установка компонентов с уровнями сигналов 5В или

3,3 В. Механические ключи (пластмассовые перемычки) на разъемах

исключают установку плат в «чужой» слот. Возможно изготовление

универсальных плат, поддерживающих оба уровня сигналов (что сейчас и

делает большинство производителей). Сочетание частот шины 33 МГц или 66

МГц с разрядностью данных предоставляет широкий диапазон пропускных

100