Wilamowski B.M., Irwin J.D. The Industrial Electronics Handbook. Second Edition: Industrial Communication Systems

Подождите немного. Документ загружается.

40-10 Industrial Communication Systems

which.communication.can.be.implemented.exibly..It.only.has.to.be.ensured.that.all.IRT.frames.can.be.sent.

wit

hin

.the.“or

ange

.int

erval.”

.e.syn

chronized

.“se

nd

.cyc

le”

.caus

es

.all.nod

es

.par

ticipating

.in.IRT.com

mu-

nication

.to.sta

rt

.tra

nsmitting

.I/O.data.at.the.sta

rt

.of.the.“or

ange

.int

erval.”

.As.a.res

ult,

.all.pos

sible

.wai

t

.tim

es

.

are.red

uced

.to.a.min

imum

.(sa

me

.as.in.uns

ynchronized

.com

munication),

.whe

reas

.the.I/O.tra

c

.is.sec

ured

.

aga

inst

.oth

er

.data.tra

c.

.e.data.fra

mes

.are.tra

nsmitted

.to.the.end.nod

e

.via.the.res

pective

.des

tination

.por

t

.

sol

ely

.on.the.basi

s

.of.the

ir

.MAC.add

ress

.(an

d

.cor

responding

.Fra

me_ID).

.is.ena

bles

.a.ver

y

.ex

ible

.met

hod

.

of.com

munication

.tha

t

.is.not.sub

ject

.to.any.spe

cial

.rul

es.

.Cha

nges

.in.the.pla

nt

.top

ology

.hav

e

.no.ee

ct

.her

e.

.

How

ever,

.base

d

.on.the.con

cept,

.the.enh

anced

.ex

ibility

.and.res

ulting

.ease.of.adap

tability

.of.a.sys

tem

.is.mad

e

.

pos

sible

.at.the.exp

ense

.of.inc

omplete

.opt

imization

.of.the.ban

dwidth

.uti

lization

.beca

use

.a.sma

ll

.res

erve

.is.

pro

vided

.for.in.the.“or

ange

.int

erval.”

.is.ens

ures

.tha

t

.all.fra

mes

.hav

e

.bee

n

.sen

t.

.Fra

mes

.wit

hin

.the.“or

ange

.

int

erval”

.can.be.tra

nsmitted

.wit

h

.or.wit

hout

.VLA

N

.tag

.

40.3.2 Communication Based on rt_CLaSS_3 (red Interval)

In.this.case,.the.communication.in.the.“red.interval”.is.based.on.a.schedule.congured.in.advance.(dur-

ing

.eng

ineering

.pha

se),

.i.e

.,

.in.add

ition

.to.the.inf

ormation

.for.the.end.nod

es,

.the.net

work

.com

ponents

.

loc

ated

.in.bet

ween

.req

uire

.inf

ormation

.de

ning

.the.for

warding

.of.fra

mes.

.Fra

mes

.are.for

warded

.bas

ed

.

exc

lusively

.on.the.pla

nning

.alg

orithm

.de

ned

.in.IEC.611

58.

.As.a.res

ult

.of.pla

nning,

.an.Ethe

rnet

.con

-

troller

.(or.mor

e

.pre

cisely,

.the.int

egrated

.swi

tch

.in.an.Ethe

rnet

.con

troller)

.kno

ws

.exa

ctly

.whi

ch

.fra

me

.

arr

ives

.at.whi

ch

.por

t

.and.whe

n

.it.mus

t

.be.for

warded

.to.whe

re.

.is.ena

bles

.a.ver

y

.hig

h

.uti

lization

.

of.the.ban

dwidth

.ava

ilable.

.If.a.sys

tem

.req

uires

.RT_

CLASS_3

.com

munication,

.the.bus.cyc

le

.mus

t

.be.

div

ided

.into.a.“re

d

.int

erval”

.and.a.UDP

/IP

.par

t

.(gr

een

.int

erval)

.dur

ing

.eng

ineering.

.Her

e,

.the.tim

ing

.

and.len

gth

.of.eac

h

.fra

me

.to.be.sen

t

.is.spe

cied

.on.a.por

t-by-port

.basi

s.

.e.pla

nt

.topo

logy,

.the.res

pective

.

fra

me

.len

gth,

.and.the.cab

le

.len

gths

.bet

ween

.the.ind

ividual

.nod

es

.are.cri

tical

.fac

tors

.in.the.tim

ing

.for.

the.pur

pose

.of.its.opti

mal

.uti

lization.

.If.the.sys

tem

.is.cha

nged,

.the.pla

nning

.alg

orithm

.mus

t

.the

refore

.

be.rep

eated.

.Dat

a

.tra

nsmission

.in.the.IRT.por

tion

.is.alw

ays

.sch

eduled.

.e.“sc

hedule”

.is.gea

red

.onl

y

.

to.the.seq

uence

.of.arr

iving

.fra

mes,

.whi

ch

.is.det

ermined

.by.the

ir

.Fra

me_ID

.and.the.fra

me

.len

gth.

.e.

tim

e-controlled

.pro

cessing

.of.jobs.wit

hin

.the.“re

d

.int

erval”

.aid

s

.in.eli

minating

.the.na

l

.sou

rces

.of.ina

c-

curacies.

.Sin

ce

.RT_

CLASS_3

.com

munication

.is.ori

ented

.onl

y

.on.the.basi

s

.of.tim

ing,

.the.thr

oughput

.

tim

es

.of.dat

a

.fra

mes

.thr

ough

.a.swi

tch

.are.sign

icantly

.sho

rter.

.Lik

ewise,

.the.per

formance

.in.bra

nched

.

net

works

.can.be.inc

reased

.by.opti

mized

.use.pla

nning

.of.the.sam

e

.com

munication

.pat

h.

.e.topo

logy

.

inf

ormation

.is.sen

t

.to.the.res

pective

.IO.con

troller

.dur

ing

.sys

tem

.pow

er-up.

.RT_

CLASS_3

.fra

mes

.are.

alw

ays

.se

nt

.wi

thout

.VL

AN

.ta

g

.sin

ce

.th

e

.ch

ronological

.po

sition

.is.al

ways

.kn

own.

40.3.3 Cycle Duration and Constrains

e.maximum.frame.length.in.Ethernet/PROFINET.yields.a.minimum.duration.of.the.“green.interval”.of.

125.μs.(4.×.31.

25

.μs)..How

ever,

.cer

tain

.rul

es

.mus

t

.be.de

ned

.in.ord

er

.to.car

ry

.out.ec

ient

.dat

a

.com

munica-

tion

.inv

olving

.di

erent

.RT.cla

sses,

.ens

uring

.tha

t

.the.timi

ng

.and.the.iso

chronous

.ope

ration

.are.adh

ered

.to.in.

eve

ry

.con

guration.

.e.gen

eral

.rul

e

.is.tha

t

.at.lea

st

.two.TCP

/IP

.fra

mes

.wit

h

.max

imum

.len

gth

.can.be.sen

t

.

per.mill

isecond.

.is.cor

responds

.to.a.tra

nsmission

.tim

e

.of.app

roximately

.250.μs..For.bus.cyc

les

.<=.500.μs,.

the.rul

e

.is.red

uced

.to.one.TCP

/IP

.fra

me.

.Fur

thermore,

.the.tra

nsmission

.tim

e

.of.cyc

lic

.dat

a

.sho

uld

.not.exc

eed

.

60%.of.the.bus.cyc

le

.in.ord

er

.to.all

ow

.su

cient

.tim

e

.for.TCP

/IP

.com

munication

.(se

e

.Fig

ure

.40.

5).

Only

.el

d

.dev

ices

.tha

t

.sup

port

.syn

chronization

.mea

sures

.can.par

ticipate

.in.syn

chronized

.com

muni-

cation

.(bu

s

.syn

chronization).

.Oth

erwise,

.the.tim

ing

.of.the.di

erent

.pha

ses

.can

not

.be.adh

ered

.to..Eac

h

.

dev

ice

.has.its.own.upd

ate

.tim

e.

.e.adv

antage

.of.the.dev

ice-granular

.upd

ate

.spe

cication

.is.tha

t

.the.

ban

dwidth

.can.be.sha

red

.by.fas

t

.nod

es

.and.slo

w

.nod

es.

.As.a.res

ult,

.the.upd

ate

.rat

e

.is.no.lon

ger

.det

er-

mined

.by.the.tota

l

.numb

er

.of.nod

es

.but.ins

tead

.can.be.ada

pted

.acc

ording

.to.the.app

lication.

.Und

er

.cer

-

tain

.con

ditions,

.it.is.pos

sible

.to.hav

e

.a.mix

ture

.of.iso

chronous

.and.non

isochronous

.app

lications

.in.el

d

.

devices.in.one.automation.system..However,.between.two.devices.that.run.isochronously,.only.switches.

wit

h

.su

pport

.to.is

ochronous

.op

eration

.ca

n

.be.us

ed.

© 2011 by Taylor and Francis Group, LLC

PROFINET 40-11

40.4 Engineering and Commissioning

e.PROFINET.support.to.the.system.engineering.is.very.powerful.in.order.to.reduce.the.commission-

ing

.phas

e

.of.the.netw

ork.

.For.inst

ance,

.the.PROF

INET

.func

tionalities

.of.a.cert

ied

.devi

ce

.are.desc

ribed

.

in.a.port

able

.le.(the.GSD.le)

,

.and.netw

ork

.mana

gement

.(add

ressing,

.redu

ndancy,

.etc.

)

.are.incl

uded

.

in.the.pro

tocol

.sta

ck.

40.4.1 GSD File

e.functionality.of.a.PROFINET.IO.device.is.always.described.in.a.GSD.le..is.le.contains.all.data.

that.are.rele

vant

.for.engi

neering

.as.well.as.for.data.exch

ange

.with.the.IO.devi

ce.

.PROF

INET

.IO.devi

ces

.

can.be.desc

ribed

.using.XML-b

ased

.GSD..e.desc

ription

.lang

uage

.of.the.GSD.le,.i.e.,.Gene

ric

.Stati

on

.

Desc

ription

.Mark

up

.Lang

uage

.(GSD

ML),

.is.base

d

.on.inte

rnational

.stan

dards.

.As.the.name.sugg

ests,

.

the.GSD.le.is.a.lang

uage-independent

.eXten

sible

.Mark

up

.Lang

uage

.(XML

)

.le..Many.XML.pars

ers

.

are.curr

ently

.avai

lable

.on.the.mark

et

.for.inte

rpreting

.XML.les

.

.Ever

y

.manu

facturer

.of.a.PROF

INET

.

IO.devi

ce

.must.supp

ly

.an.asso

ciated

.GSD.le.acco

rding

.to.the.GSDM

L

.spec

ication.

.is.le.is.test

ed

.

as.part.of.cert

ication

.test

ing.

.To.desc

ribe

.PROF

INET

.IO.devi

ces,

.PI.prov

ides

.an.XML.sche

ma

.to.each.

manu

facturer.

.is.allo

ws

.a.GSD.le.to.be.crea

ted

.and.test

ed

.easil

y.

.e.need.for.nume

rous

.subs

e-

quent

.inpu

t

.chec

ks

.is.ther

efore

.omit

ted.

.In.addi

tion,

.the.devi

ce

.mode

l

.of.PROF

INET

.IO.exhi

bits

.a.

furt

her

.hier

archy

.leve

l

.for.data.addr

essing

.when.comp

ared

.to.PROF

IBUS.

.us,.e.g.,.addr

essing

.with

in

.

a.eld.devi

ce

.(in.PROF

IBUS:

.slot.and.inde

x)

.has.been.expa

nded

.to.incl

ude

.the.iden

tier

.of.a.subs

lot.

.

In.PROF

INET

.IO,.addr

essing

.with

in

.a.eld.devi

ce

.can.be.perf

ormed

.with.ner.gran

ularity

.(slo

t

.and.

subs

lot).

.In.addi

tion,

.this.type.of.addr

essing

.coul

d

.not.be.desc

ribed

.with.the.GSD.le.for.PROF

IBUS.

.

To.enab

le

.syst

em

.engi

neering,

.the.GSD.les.of.the.eld.devi

ces

.to.be.con

gured

.are.requ

ired.

.e.eld.

devi

ce

.manu

facturer

.is.resp

onsible

.for.supp

lying

.thes

e.

.Duri

ng

.syst

em

.engi

neering,

.the.con

guring

.

engi

neer

.joins.toget

her

.the.modu

les/submodules

.den

ed

.in.the.GSD.le.to.map.them.to.the.real.syst

em

.

and.to.assig

n

.them.to.slot

s/subslots.

.e.con

guring

.engi

neer

.con

gures

.the.real.syst

em,

.so.to.spea

k,

.

symbo

lically

.in.the.eng

ineering

.tool

.

40.4.2 Device addressing

A.logical.name.is.assigned.to.every.eld.device..It.should.reference.the.function.or.the.installation.

loca

tion

.of.the.devi

ce

.in.the.plan

t

.and.ulti

mately

.lead.to.assig

nment

.of.an.IP.addr

ess

.duri

ng

.addr

ess

.

reso

lution.

.e.name.can.alwa

ys

.be.assig

ned

.with.the.DCP.inte

grated

.by.defa

ult

.in.ever

y

.PROF

INET

.IO.

eld.devi

ce.

.PROF

INET

.prov

ides

.also.the.optio

n

.for.addr

ess

.sett

ing

.via.DHCP.or.othe

r

.manu

facturer-

specic

.mech

anisms.

.e.addr

essing

.optio

ns

.supp

orted

.by.an.IO.eld.devi

ce

.are.den

ed

.in.the.GSD.le.

for.the.resp

ective

.devi

ce.

.An.IO.cont

roller

.has.all.the.info

rmation

.need

ed

.for.addr

essing

.the.IO.devi

ces

.

and.for.data.exch

ange

.aer.all.the.nece

ssary

.info

rmation

.have.been.down

loaded

.by.the.manu

facturer-

specic

.eng

ineering

.tool

.

Before

.it.can.perf

orm

.data.exch

ange

.with.an.IO.devi

ce,

.the.IO.cont

roller

.must.assig

n

.the.IO.devi

ce

.

an.IP.addr

ess

.base

d

.on.the.devi

ce

.name

.

.is.must.take.plac

e

.prio

r

.to.syst

em

.powe

r-up

.(“Po

wer

.on”.or.a.

“Res

et”).

.e.IP.addr

ess

.is.assig

ned

.with

in

.the.same.subn

et

.using.the.DCP.proto

col

.inte

grated

.by.defa

ult

.

in.ever

y

.PROF

INET

.IO.devi

ce.

.An.IO.cont

roller

.alwa

ys

.init

iates

.syst

em

.powe

r-up

.aer.a.star

tup/restart

.

base

d

.on.the.con

guration

.dat

a

.wit

hout

.any.int

ervention

.by.the.use

r.

40.4.3 System Power-Up

Following.a.“power.on,”.the.following.steps.are.performed.in.the.eld.device:.initializing.the.physi-

cal

.inte

rfaces

.in.an.IO.devi

ce

.in.orde

r

.to.acco

mmodate

.the.data.tra

c;

.nego

tiating

.the.tran

smis-

sion

.para

meters;

.dete

rmining

.the.degr

ee

.of.expa

nsion

.in.the.eld.devi

ce

.and.comm

unicating

.the.

© 2011 by Taylor and Francis Group, LLC

40-12 Industrial Communication Systems

information.to.the.context.management;.starting.the.exchange.of.the.neighborhood.information;.

address.resolution.on.the.side.of.the.IO.controller;.establishment.of.communication.between.IO.con-

troller

.and.IO.device;.parameterizing.the.submodules.in.the.device.(write.records);.retentive.saving.of.

port.information.to.the.physical.device.(PDev);.completing.and.checking.the.parameterization,.and.

starting.the.data.exchange.

To

.establish.communication.between.the.higher.level.controller.and.an.IO.device,.the.communica-

tion

.paths.must.be.established..ese.are.set.up.by.the.IO.controller.during.system.startup.based.on.the.

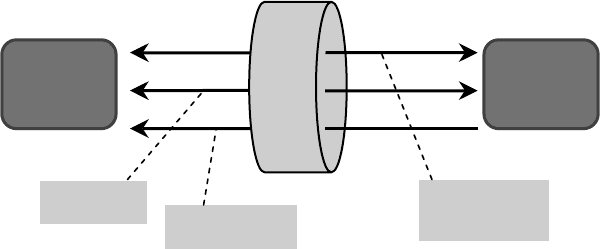

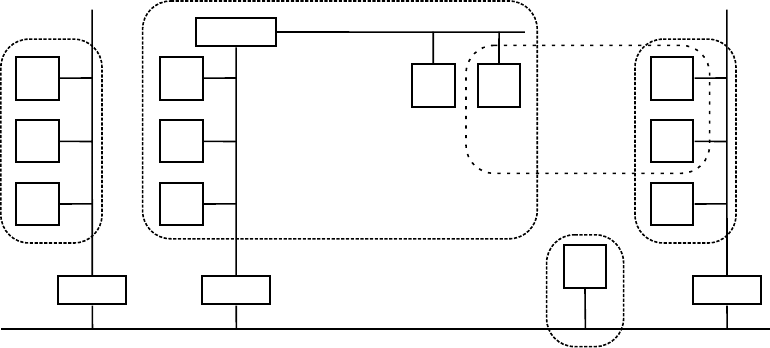

conguration.data.in.the.engineering.system..is.species.the.data.exchange.explicitly..As.shown.in.

Figure.40.4,.every.data.exchange.has.an.embedded.“application.relation”.(AR)..is.establishes.a.pre-

cisely

.specied.application.(connection),.i.e.,.the.AR,.between.the.higher.level.controller.(IO.controller.

or.IO.supervisor).and.the.IO.device..Within.the.AR,.“communication.relations”.(CR).specify.the.data.

explicitly..An.IO.device.can.have.multiple.ARs.established.from.various.IO.controllers.

e

.IO.controller.initiates.setup.of.an.AR.during.system.power-up..As.a.result,.all.data.for.the.device.

modeling,.including.the.general.communication.parameters,.are.downloaded.to.the.IO.device..At.the.

same.time,.the.communication.channels.for.cyclic/acyclic.data.exchange.(IO.data.CR,.record.data.CR),.

alarms.(alarm.CR),.and.multicast.communication.relations.(MCR).are.set.up..CR.for.data.exchange.must.

be.set.up.within.an.AR..ese.specify.the.explicit.communication.channel.between.a.consumer.and.a.

provider.

40.4.4 Neighborhood and topology Detection

PROFINET.specication.describes.a.method.to.replace.a.device.without.using.an.engineering.tool..

is.task.is.done.by.means.of.neighborhood.detection.with.the.link.layer.discovery.protocol.(LLDP).

according.to.IEEE.802.1.AB..is.requires.the.ability.to.determine.the.data.of.neighboring.devices.

on.a.port-by-port.basis.using.LLDP.services.and.to.provide.these.data.to.the.higher.level.controller..

Together,.these.conditions.enable.modeling.of.a.plant.topology.and.convenient.plant.diagnostics.as.

well. as. device.replacement.without.additional.tools.. PROFINET. IO.eld.devices.exchange.existing.

addressing.information.with.connected.neighbor.devices.over.each.switch.port..e.neighbor.devices.

are.thereby.unambiguously.identied.and.their.physical.location.is.determined..e.LLDP.protocol.is.

implemented.in.soware.and.therefore.requires.no.special.hardware.support..LLDP.is.independent.of.

the.network.structure.(line,.star,.etc.)..Automation.systems.can.be.congured.with.a.line,.star,.or.tree.

structure..For.this.reason,.it.is.important.to.know.which.eld.devices.are.connected.to.which.switch.

port.and.the.identity.of.the.respective.port.neighbor..e.higher.level.controller.can.then.reproduce.the.

plant.topology.accordingly..In.addition,.if.a.eld.device.fails,.it.is.possible.to.check.whether.the.replace-

ment

.device.has.been.reconnected.in.the.proper.position.

IO Data CR

- Process data

Record data CR

- Conguration

- Parametrization

Alarm CR

- Real-time alarm

AR

PROFINET

IO-

controller

PROFINET

IO-

device

FIGURE 40.4 Data. communication. in. PROFINET. IO. is. encapsulated. in. “application. and. communication.

relations.”

© 2011 by Taylor and Francis Group, LLC

PROFINET 40-13

40.4.5 redundancy

e.goal.of.redundancy.in.automation.systems.is.to.increase.the.system.availability.signicantly,.thus.a.

redundancy.manager.(RM).and.several.clients.should.be.used.to.assure.the.correct.operation.in.this.cases.

e

.media.redundancy.protocol.(MRP),.according.to.IEC.61158.and.IEC.61784,.describes.PROFINET.

redundancy.(for.TCP/IP.and.RT.frames).with.a.typical.reconguring.time.of.communication.paths.aer.

a.fault.of.less.than.200.ms..e.MRP.operates.with.a.physical.ring.structure.where.the.RM.is.the.coordina-

tor.

.e.task.of.an.RM.is.to.check.the.functional.capability.of.the.congured.ring.structure..is.is.done.by.

sending.out.cyclic.test.frames:.as.long.as.the.ring.structure.is.intact,.it.receives.all.the.test.frames.again.aer.

one.circulation.through.the.ring..e.architecture.allows.an.RM.to.prevent.standard.frames.from.circulating.

and.to.convert.a.physical.ring.structure.into.a.“logical”.line.structure..e.RM.must.communicate.changes.

in.the.ring.to.all.clients.involved.(switches.as.so-called.passers).through.special.“change.in.topology”.frames.

In

.principle,.even.in.PROFINET.IO.redundant.installations,.the.same.previously.described.data.trans-

mission

.mechanisms.are.used..e.only.dierence.is.the.communication.path.used.to.transmit.the.frames.

(UDP/IP.and.RT.frames)..ese.frames.are.only.transmitted.via.the.“healthy”.channel.(single.channel).

that.looks.like.a.line.structure..A.redundancy.client.(RC).is.a.switch.that.acts.only.as.a.“passer”.of.frames.

and.generally.does.not.assume.an.active.role..It.must.have.two.switch.ports.in.order.to.connect.to.other.cli-

ents

.or.the.RM.in.a.single.ring..In.PROFINET.IO,.only.“managed.switches”.that.support.MRP.are.used.for.

implementing.media.redundancy..Redundant.switches.can.be.congured,.e.g.,.via.SNMP.or.Web.services.

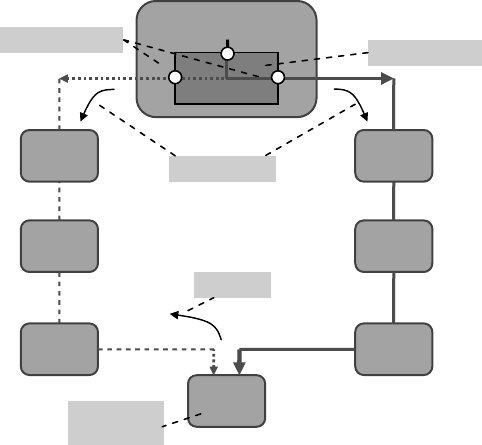

e

.media.redundancy.for.real-time.(MRRT).protocol.dened.in.IEC.61158.describes.the.handling.of.

RT.frames.of.RT_CLASS_1.and.RT_CLASS_2.for.redundancy.operation..Operation.of.MRP.is.always.

a.prerequisite.for.operation.of.MRRT..IEC.61784.describes.the.procedure.for.using.the.MRRT.protocol..

With.RT.communication,.the.MRRT.protocol.enables.a.virtually.smooth.switchover.of.communica-

tion

.paths.if.a.fault.occurs..is.is.accomplished.by.redundant.transmission.of.RT.frames.(i.e.,.via.two.

channels).if.the.destination.port.is.designed.as.a.redundant.port.(see.Figure.40.5)..On.the.receiving.side,.

two.RT.frames.always.arrive,.provided.the.redundant.transmission.is.error-free..Only.the.rst.frame.to.

arrive.is.forwarded.to.the.application..Also.in.this.case,.the.RM.must.check.the.functional.capability.of.

the.system.by.means.of.test.frames.

Station 1

Managed switch

Redundant ports

Station

2

Station

3

Station

8

Station

7

Station

5

Station

4

Station

6

Process data

Test frame

Destination

Source

Comparison

old/new data

FIGURE 40.5 Media.redundancy.with.MRP.increases.the.plant.availability.

© 2011 by Taylor and Francis Group, LLC

40-14 Industrial Communication Systems

IEC. 61158.describes. the. redundancy. concept. for. RT_CLASS_3. frames.as. “media. redundancy. for.

plan

ned

.dupl

ication.”

.IEC.6178

4

.descr

ibes

.the.use.of.redun

dancy

.clas

s

.3.for.RT_C

LASS_3

.comm

unica-

tion

.with.smoo

th

.swit

chover

.of.comm

unication

.path

s

.if.a.faul

t

.occur

s.

.Duri

ng

.syst

em

.powe

r-up,

.the.IO.

cont

roller

.load

s

.the.data.of.the.comm

unication

.path

s

.for.both.comm

unication

.chan

nels

.(dir

ections)

.in.a.

comm

unication

.ring.to.the.indi

vidual

.node

s.

.us,.it.is.unim

portant

.whic

h

.node.fail

s

.becau

se

.the.load

ed

.

“sched

ule”

.for.both.path

s

.is.avail

able

.in.the.eld.devi

ces.

.Load

ing

.of.the.“sched

ule”

.alon

e

.is.suc

ient

.to.

excl

ude

.fram

es

.from.circ

ulating

.in.this.varia

nt,

.becau

se

.the.dest

ination

.port

s

.are.expl

icitly

.den

ed.

40.5 Integration of Fieldbus Systems and Web applications

PROFINET. species.a. model.for.integrating. existing.PROFIBUS.and.other.eldbus.systems.such.as.

INTE

RBUS

.and.Devi

ceNet.

.is.mean

s

.that.any.comb

ination

.of.eld

bus

.and.Ethe

rnet-based

.subs

ystems

.

can.be.con

gured

.in.a.simp

le

.way..e.foll

owing

.cons

trains

.are.take

n

.into.cons

ideration:

.the.plan

t

.oper

a-

tor

.woul

d

.like.the.abil

ity

.to.easi

ly

.inte

grate

.his.exis

ting

.inst

allations

.into.a.newl

y

.inst

alled

.PROF

INET

.

syst

em;

.the.plan

t

.and.mach

ine

.manu

facturer

.woul

d

.like.the.abil

ity

.to.use.the.well

-proven

.devi

ces

.it.is.

fami

liar

.with.for.PROF

INET

.auto

mation

.proj

ects,

.as.well

,

.with

out

.the.need.for.any.modi

cations;

.the.

devi

ce

.manu

facturer

.woul

d

.like.the.abil

ity

.to.inte

grate

.its.exis

ting

.eld.devi

ces

.into.PROF

INET

.syst

ems

.

with

out

.expe

nding

.any.eor

t

.for.modi

cations.

.Fiel

dbus

.solut

ions

.can.be.easi

ly

.and.seaml

essly

.inte

grated

.

into.a.PROF

INET

.syst

em

.usin

g

.prox

ies

.and.gate

ways.

.Anyw

ay,

.the.more.powe

rful

.way.is.usin

g

.a.prox

y.

40.5.1 Integration via Proxy

In.simplest.terms,.a.proxy.is.a.representative.for.a.lower-level.eldbus.system..In.PROFINET,.a.proxy.rep-

resents

.a.eld

bus

.(e.g.

,

.PROF

IBUS,

.Inte

rbus,

.Foun

dation

.Fiel

dbus,

.Devi

ceNet).

.As.a.resu

lt,

.the.advan

tages

.

of.eld

buses,

.such.as.high.dyna

mic

.resp

onse,

.pinp

oint

.diag

nostics,

.and.auto

matic

.syst

em

.con

guration

.

with

out

.setti

ngs

.on.devi

ces,

.can.be.util

ized

.in.the.PROF

INET

.worl

d.

.More

over

.with.the.prox

y,

.devi

ces

.

and.sowa

re

.tool

s

.are.also.supp

orted

.in.the.accus

tomed

.mann

er

.and.inte

grated

.into.the.hand

ling

.of.the.

PROF

INET

.syst

em.

.e.prox

y

.coor

dinates

.the.Ethe

rnet

.data.tra

c

.and.the.eld

bus-specic

.data.traf

-

c.

.For.inst

ance,

.a.PROF

INET/PROFIBUS

.prox

y

.(on.the.Ethe

rnet

.side

)

.repr

esents

.one.or.more.eld

bus

.

devi

ces.

.is.prox

y

.ensu

res

.tran

sparent

.impl

ementation

.of.comm

unication

.(no.tunn

eling

.of.prot

ocols)

.

betw

een

.netw

orks.

.For.exam

ple,

.it.forw

ards

.the.cycl

ic

.data.comi

ng

.from.the.Ethe

rnet

.to.the.eld

bus

.

devi

ces

.in.a.tran

sparent

.mann

er.

.On.the.PROF

IBUS

.DP.side

,

.the.prox

y

.work

s

.as.a.PROF

IBUS

.mast

er

.

that.exch

anges

.data.with.PROF

IBUS

.node

s.

.At.the.same.time

,

.it.is.an.Ethe

rnet

.node.with.Ethe

rnet-based

.

PROF

INET

.comm

unication.

In

.this.proc

ess,

.the.Ether

net

.comm

unication

.is.alre

ady

.den

ed

.by.the.avai

lable

.sow

are.

.Only.the.

init

ialization

.of.the.proc

ess

.data.prev

iously

.prov

ided

.from.the.lowe

r

.leve

l

.eld

bus

.to.PROF

INET

.stil

l

.

has.to.be.ensu

red.

.As.a.resu

lt

.of.this.conc

ept,

.eld

buses

.of.any.type.can.be.inte

grated

.into.PROF

INET

.

with.mini

mal

.eor

t,

.wher

eby

.a.prox

y

.is.used.to.repr

esent

.the.lowe

r

.leve

l

.bus.syst

em.

.For.inst

ance,

.prox

-

ies

.can.be.imp

lemented

.as.PLC

s

.or.PC-b

ased

.con

trollers.

40.5.2 Web Integration

e.PROFINET.Web.integration.was.designed.mainly.for.commissioning.and.diagnostics..Possible.

appl

ications

.for.Web.inte

gration

.incl

ude:

.test

ing

.and.comm

issioning

.of.the.netw

ork,

.over

view

.of.devi

ce

.

data.(PRO

FINET

.IO),.and.devi

ce

.diag

nostics

.and.syst

em/device

.docu

mentation.

.e.basic.comp

onent

.

of.Web.inte

gration

.is.the.Web.serv

er.

.is.mean

s

.that.even.a.simpl

e

.PROF

INET

.devi

ces

.with.Web.

inte

gration

.optio

n

.is.equi

pped

.with.an.“embe

dded

.Web.serv

er.”

.e.indi

vidual

.func

tions

.can.be.impl

e-

mented

.depe

nding

.on.the.perf

ormance

.capa

bility

.of.the.devi

ce.

.is.allo

ws

.solu

tions

.to.be.custo

mized

.

to.eac

h

.use.cas

e.

© 2011 by Taylor and Francis Group, LLC

PROFINET 40-15

acronyms

AR. Application.relation

CR

. Com

munication

.re

lations

DCP

. Dis

covery

.an

d

.co

nguration

.pr

otocol

DHCP

. Dyn

amic

.ho

st

.co

nguration

.pr

otocol

IRT

. Iso

chronous

.re

al-time

.co

mmunication

LLDP

. Lin

k

.la

yer

.di

scovery

.pr

otocol

MRP

. Med

ia

.re

dundancy

.pr

otocol

MRRT

. Med

ia

.re

dundancy

.fo

r

.re

al-time

PI

. PRO

FIBUS

.In

ternational

RT

. Rea

l-time

.co

mmunication

Bibliography

. 1.. International.Electrotechnical.Commission,.IEC.61158..Digital.data.communications.for.measure-

ment

.and.cont

rol—Fieldbus

.for.use.in.indu

strial

.cont

rol

.system

s,

.Int

ernational

.Elec

trotechnical

.

Commi

ssion,

.Gen

eva,

.Sw

itzerland,

.2007.

. 2.. Int

ernational

.Ele

ctrotechnical

.Com

mission,

.IEC.617

84-1.

.Ind

ustrial

.Com

munication

.Net

works—

Profiles—Part

. 1:. Fie

ldbus

. pro

files,

. Int

ernational

. Ele

ctrotechnical

. Com

mission,

. Gen

eva,

.

Swi

tzerland,

.200

7.

. 3.. Int

ernational

.Elec

trotechnical

.Commi

ssion,

.IEC.61784-2..Ind

ustrial

.Comm

unication

.Netw

orks—

Proles—Part

. 2:. Addit

ional

. eldb

us

. pro

les

. for. rea

l-time

. netw

orks

. bas

ed

. on.ISO/IEC. 8802-3,.

Int

ernational

.Ele

ctrotechnical

.Co

mmission,

.Gen

eva,

.Sw

itzerland,

.2007.

. 4.. Pro

bus

. Int

ernational,

. GSDML

Specication for Pronet IO,

. Versio

n

. 2.20,. Order. No.. 2.352,.

PRO

FIBUS

.Nu

tzerorganisation

.e.V

.,

.Ka

rlsruhe,

.Ger

many,

.2008.

. 5.. Pro

bus

.Int

ernational,

.Pro

le Guidelines Part 1: Identication & Maintenance Functions,

.Versio

n

.

1.1.1,.Order.No

.

.3.502,.PR

OFIBUS

.Nu

tzerorganisation

.e.V

.,

.Ka

rlsruhe,

.Ger

many,

.2005.

© 2011 by Taylor and Francis Group, LLC

41-1

41.1 Introduction

LonWorks.or.local.operating.network.(LON).is.an.event-triggered.control.network.system.originally.

desig

ned

.by.Eche

lon

.Corp

oration

.in.1990

.

.It.consi

sts

.of.a.comm

unication

.proto

col

.call

ed

.LonT

alk,

.a.

spec

ial

.cont

roller

.(the.Neur

on

.Chip

),

.tran

sceivers

.for.bus.acce

ss,

.and.a.set.of.deve

lopment

.and.mana

ge-

ment

.tool

s.

e

.main.appl

ication

.of.LonW

orks

.is.buil

ding

.and.home.autom

ation,

.wher

e

.it.is.used.to.cont

rol

.

and.moni

tor,

.amon

g

.othe

rs,

.heat

ing,

.vent

ilating,

.and.air-

conditioning

.(HVA

C),

.ligh

ting,

.secu

rity,

.and.

elev

ators.

.But.also.othe

r

.appl

ication

.area

s

.exis

t,

.such.as.indu

strial

.autom

ation,

.tran

sportation

.autom

a-

tion,

.and.str

eet

.lig

hting.

e

.LonT

alk

.comm

unication

.prot

ocol,

.whic

h

.impl

ements

.the.OSI.refe

rence

.mode

l,

.was.stan

dard-

ized

.as.ANSI

/EIA-709

.and.ANSI

/CEA-709

.in.1999

.

.Both.stan

dards

.also.incl

ude

.the.chan

nel

.spec

i-

cations

.of.free

-topology

.twis

ted-pair,

.powe

r

.line.and.ber

-optics,

.whic

h

.are. used. for.LonW

orks

.

netw

orks.

.e.LonT

alk

.prot

ocol

.ANSI

/CEA-709

.was.revi

sed

.in.2002.[1].and.was.rele

ased

.as.Euro

pean

.

Stan

dard

.EN-1

4908

.[2].in.2005

.

.e.corr

esponding

.inte

rnational

.stan

dard

.ISO/

IEC-14908

.is.cur-

r

ently

.in.dra.stat

e

.[3].

G

uidelines

. for. the. impl

ementation

. of. the. appl

ications

. on. the. Neur

on

. Chip

s

. are. den

ed

. by. the.

LonM

ark,

.a.glo

bal

.memb

ership

.org

anization

.tha

t

.pro

motes

.and.adv

ances

.the.Lon

Works

.pla

tform.

41.2 System Components

LonWorks.networks.normally.consist.of.network.nodes,.based.on.the.Neuron.Chip..In.the.rst.years,.

these.chip

s

.were.manu

factured

.by.Moto

rola

.[4].and.Tosh

iba

.[5]..Toda

y’s

.mode

ls

.are.buil

t

.by.Cypre

ss

.[6].

and.Eche

lon

.itse

lf.

.Eche

lon

.oer

s

.so-c

alled

.smar

t

.tran

sceivers,

.whic

h

.inte

grate

.a.Neur

on

.Chip.and.

atran

sceiver

.into.one.chi

p

.[7]

.

41

LonWorks

41.1. Introduction.....................................................................................41-1

41.2

. Syst

em

.Com

ponents........................................................................ 41-1

41.3

. LonT

alk

.Pro

tocol.............................................................................41-4

Physical.Layer. •. Link.Layer. •. Network.Layer. •. Transport.

andSession.Layer. •. Application.and.Presentation.Layer

41.4. e.Application.Layer.Programming.Model.............................. 41-7

41.5

. Func

tion

.Blo

ck-Based

.Desi

gn

.and.Sys

tem

.Int

egration.............41-8

41.6

. Netw

ork

.Desi

gn

.Too

ls................................................................... 41-11

41.7

. Autom

atic

.Desi

gn

.App

roaches....................................................41-12

References................................................................................................... 41-13

Uwe Ryssel

Dresden University

of Tec

hnology

Henrik Dibowski

Dresden University

of Tec

hnology

Heinz Frank

Reinhold-Würth-University

Klaus Kabitzsch

Dresden University

of Tec

hnology

© 2011 by Taylor and Francis Group, LLC

41-2 Industrial Communication Systems

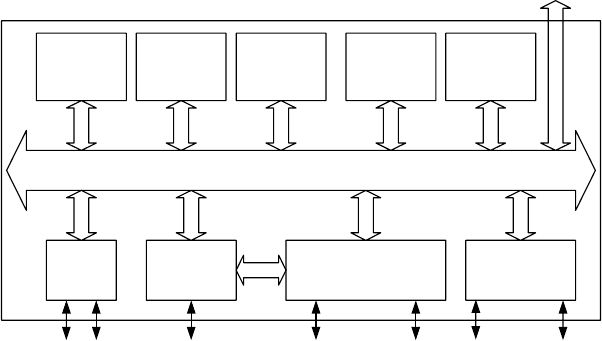

As.shown.in.Figure.41.1,.the.Neuron.Chip.implements.a.three-processor.architecture.with.shared.

memory,.which.includes.the.rmware.ROM,.an.EEPROM.for.the.user.application.program,.and.RAM..

Each.of.the.three.processors.handles.a.certain.task:

e

.media access control.(MAC).processor.sends.and.receives.messages.to.and.from.the.communi-

cation

.medium.with.support.of.the.transceiver,.which.handles.the.line.coding.for.a.specic.medium..

Since.many.dierent.transceiver.types.exist,.a.wide.range.of.communication.media.can.be.used,.such.

as.twisted.pair,.power.line,.ber.optics,.and.radio.frequency..e.network processor.handles.the.upper.

layers.of.the.LonTalk.protocol,.which.are.described.in.the.next.section..And.the.application processor.

runs.the.user.application.implementing.the.specic.task.of.the.node.

e

.communication.among.the.three.processors.is.realized.in.shared.RAM.by.communication.buf-

fers

.and.ags..ere.are.input.and.output.buer.queues.storing.messages.to.be.forwarded.to.the.other.

processors..Special.ag.bytes.indicate.that.the.other.processor.should.do.a.certain.action,.such.as.creat-

ing,

.sending,.or.receiving.a.message.

Peripheral

.hardware,.such.as.sensors.and.actuators,.are.connected.to.a.set.of.I/O.pins,.which.can.be.

congured.in.a.range.of.single.bit.input.and.output.for.switches.or.LEDs.via.nibble.and.byte.input.and.

output.up.to.higher.I/O.protocols,.such.as.serial.and.parallel.interfaces,.I

2

C,.and.Magcard.

ere

.are.also.alternatives.to.the.Neuron.Chip..For.example,.LOYTEC.oers.a.more.powerful.ARM7-

based

.embedded.controller.(LC3020).that.implements.the.LonTalk.protocol.according.to.CEA-709.as.

well..It.also.supports.LonWorks/IP.(standardized.as.CEA-852.[8]),.where.LonTalk.messages.are.tun-

neled

.over.LAN.or.Internet.in.IP.packets..Such.controllers.are.used.for.more.complex.tasks,.like.panels.

with.a.graphical.user.interface.or.IP.routers.

To

.identify.the.LonWorks.nodes.in.the.network,.each.Neuron.Chip.has.a.xed.48.bit.identier.called.

Neuron ID.assigned.by.the.manufacturer..A.LonWorks.node.can.actively.transmit.its.Neuron.ID.in.a.

service pin message,.when.a.special.service.pin.is.pressed.on.the.node..is.simplies.the.network.inte-

gration,

.when.new.nodes.have.to.be.added.to.the.network,.because.it.is.not.required.to.enter.the.Neuron.

ID.manually.in.the.management.tool..Instead,.the.management.tool.simply.has.to.wait.for.the.service.

pin.message.

During

.conguration,.a.logical.address.is.assigned.to.each.node..It.consists.of.the.domain,.subnet,.

and.node ID..e.domain.represents.a.whole.LonWorks.network,.which.is.identied.by.the.domain.ID.

with.up.to.6.bytes.length..Direct.message.passing.among.domains.is.not.possible,.but.it.can.be.done.via.

gateways.

MAC

processor

Control

Network

processor

Timer/

counter

Application I/O

Network

Com. Port

CP 0 ... 4

To transceiverTo application specic HWClockServiceReset

IO 0 ... 10

Appl.

processor

ROM

EEPROM

RAM

To external memory

Address bus (16 bit) Data bus (8 bit)

FIGURE 41.1 Structure.of.a.Neuron.Chip.

© 2011 by Taylor and Francis Group, LLC

LonWorks 41-3

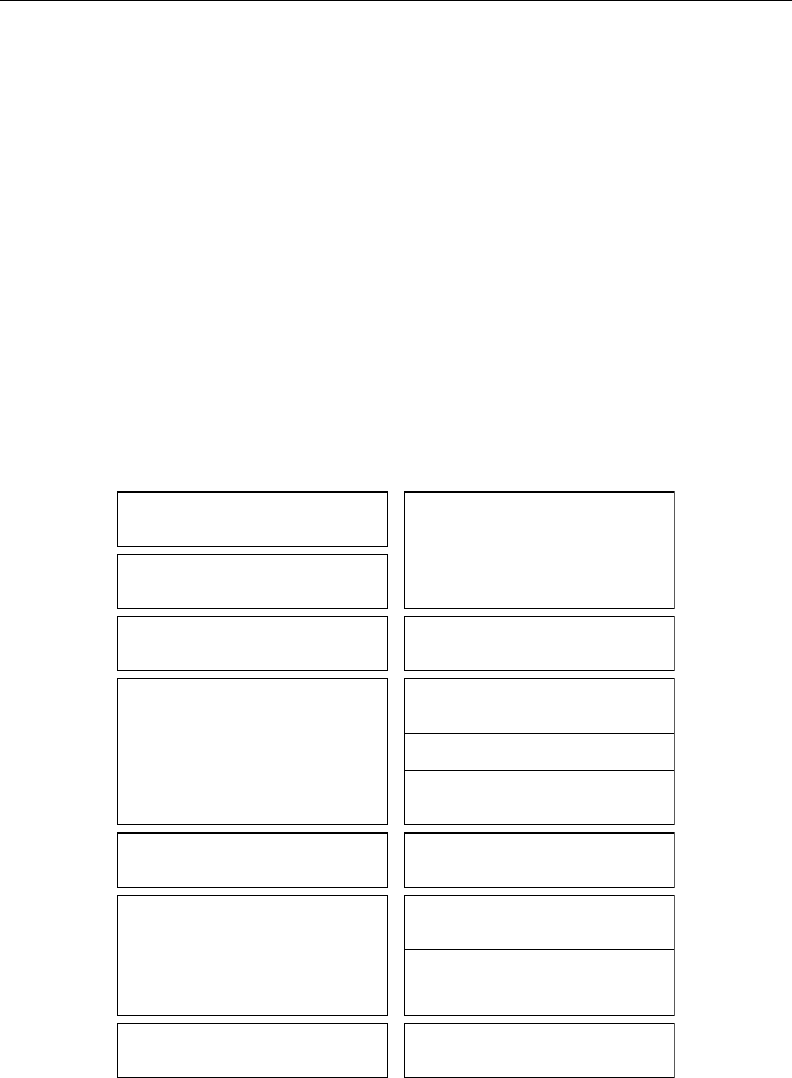

e.physical.and.logical.view.of.a.LonWorks.network.example.is.shown.in.Figure.41.2..e.network.

phy

sically

.con

sists

.of.sev

eral

.cha

nnels

.con

nected

.by.rou

ters

.and.rep

eaters.

.Log

ically,

.it.is.sep

arated

.

into.sub

nets.

.One.dom

ain

.can.con

sist

.of.up.to.255.sub

nets

.wit

h

.a.max

imum

.of.127.nod

es

.eac

h,

.whi

ch

.

res

ults

.in.a.max

imum

.of.32,

385

.nod

es

.per.dom

ain.

.Add

itionally,

.nod

es

.can.be.gro

uped.

.Per.dom

ain

.256.

gro

ups

.can.be.de

ned.

.e.exa

mple

.con

tains

.one.gro

up,

.whi

ch

.spa

ns

.thr

ee

.nod

es

.in.di

erent

.sub

nets

.

and.ch

annels.

As

.men

tioned

.bef

ore,

.di

erent

.tra

nsceivers

.sup

port

.di

erent

.com

munication

.med

ia.

.A.com

mon

.

med

ium

.is.twi

sted

.pai

r

.wit

h

.a. dat

a

.rat

e

.of.78.kbp

s,

.whe

re

.the.sign

al

.is.cod

ed

.as.vol

tage

.di

erence

.

bet

ween

.the.two.con

ductors.

.A.com

patible

.var

iant

.of.twi

sted

.pai

r

.is.Lin

k

.Pow

er,

.whi

ch

.als

o

.pro

vides

.

the.pow

er

.sup

ply

.(42

.4

.V.DC).for.the.nod

es

.ove

r

.the.twi

sted

.pai

r

.med

ium.

.For.bac

kbones,

.twi

sted

.pai

r

.

can.als

o

.be.run.wit

h

.125

0

.kbp

s,

.but.onl

y

.wit

h

.a.red

uced

.max

imum

.dis

tance

.of.130.m.amo

ng

.the.nod

es.

e

.topo

logy

.of.twi

sted

.pai

r

.net

works

.doe

s

.not.hav

e

.to.be.a.str

ict

.lin

e

.or.sta

r.

.Net

works

.can.als

o

.

be.bui

lt

.as.fre

e

.topo

logy

.con

taining

.arb

itrary

.bra

nches

.and.loo

ps.

.How

ever,

.the.max

imum

.dis

tance

.

dec

reases

.whe

n

.usin

g

.fre

e

.topo

logy.

.So,.for.exa

mple,

.a.lin

e

.bus.wit

h

.sho

rt

.bra

nches

.all

ows

.a.max

imum

.

dis

tance

.of.27

00

.m.am

ong

.th

e

.no

des,

.wh

ereas

.in.a.fr

ee

.top

ology,

.it.is.li

mited

.to.50

0

.m.

Ot

her

.sup

ported

.med

ia

.are.pow

er

.lin

e

.wit

h

.up.to.10.kbp

s,

.be

r

.opti

cs

.(1.

25

.Mbp

s),

.rad

io

.fre

quency

.

(up.to.19

.5

.kbp

s),

.an

d

.th

e

.ab

ove-mentioned

.Lo

nWorks/IP

.(1

00

.Mbp

s

.wi

th

.cu

rrent

.IP.ro

uters).

To

.inc

rease

.the.max

imum

.dis

tance

.of.Lon

Works

.net

works,

.rep

eaters

.can.be.use

d.

.ey.simp

ly

.ref

resh

.

all.inc

oming

.sign

als

.and.sen

d

.the

m

.to.the.oth

er

.net

work

.seg

ment,

.whi

ch

.has.to.be.the.sam

e

.med

ium

.

and.has.to.use.the.same.message.coding.

Since

.Lon

Talk

.imp

lements

.the.OSI.ref

erence

.mod

el,

.Lon

Works

.net

works

.can.be.con

nected

.at.hig

her

.

lay

ers,

.too..Bri

dges,

.wor

king

.on.the.dat

a

.lin

k

.lay

er,

.can.be.use

d

.to.con

nect

.net

works

.bas

ed

.on.di

erent

.

med

ia

.an

d

.co

ding.

.e

y

.al

so

.en

sure

.th

at

.on

ly

.va

lid

.me

ssages

.ar

e

.fo

rwarded

.to.th

e

.ot

her

.sid

e.

More

.com

mon

.tha

n

.pur

e

.Lon

Talk

.bri

dges

.are.rou

ters,

.whi

ch

.wor

k

.on.the.net

work

.lay

er.

.Rou

ters

.hav

e

.

the.adv

antage

.tha

t

.the

y

.do.not.onl

y

.inc

rease

.the.ran

ge

.of.the.sign

als

.or.con

nect

.di

erent

.med

ia,

.but.

the

y

.als

o

.sep

arate

.the.net

work

.tra

c

.of.di

erent

.sub

nets

.bec

ause

.rou

ters

.onl

y

.for

ward

.tho

se

.mes

sages,

.

who

se

.des

tination

.is.on.the.oth

er

.side.of.the.rou

ter.

.er

efore,

.rou

ting

.tab

les

.are.use

d.

.ey.des

cribe

.

whi

ch

.sub

nets

.or.gro

ups

.are.con

nected

.on.whi

ch

.por

t

.of.the.rou

ter.

.er

e

.are.two.met

hods

.how.rou

ting

.

tab

les

.can.be.obt

ained:

.In.con

gured router

.mod

e,

.the.tab

les

.hav

e

.to.be.de

ned

.by.the.sys

tem

.int

egrator

.

and.in.lea

rning router

.mod

e,

.the.net

work

.tra

c

.is.use

d

.to.det

ermine

.whi

ch

.sub

nets

.are.con

nected

.to.

whi

ch

.po

rt.

.Lo

nWorks

.ro

uters

.ca

n

.al

so

.op

erate

.in.br

idge

.an

d

.re

peater

.mo

de.

Channel 1

Channel 2

Channel 3

Channel 4

Repeater

1/3

1/2

1/1

2/3

2/10 2/11

3/3

3/2

3/1

4/12

2/2

2/1

Router Router

Router

s/n ... Subnet/node address

Channel 5 (backbone)

Domain ID of all nodes: 0×53

Subnet 2

Subnet 4

Subnet 3

Group 1

Subnet 1

FIGURE 41.2 Physical.and.logical.segmentation.in.LonWorks.systems.

© 2011 by Taylor and Francis Group, LLC

41-4 Industrial Communication Systems

41.3 Lontalk Protocol

e.standardized.LonTalk.protocol.implements.all.seven.layers.of.the.OSI.reference.model..Especially,.

the.stan

dardization

.of.the.uppe

r

.appl

ication-oriented

.laye

rs

.has.the.adva

ntage

.that.node

s

.from.die

rent

.

vend

ors

.are.comp

atible

.to.each.othe

r.

.Figu

re

.41.3.oppo

ses

.the.laye

rs

.of.the.OSI.refe

rence

.mode

l

.and.the.

LonT

alk

.lay

ers

.to.eac

h

.oth

er.

e

.die

rent

.laye

rs

.are.pres

ented

.in.the.next.subs

ections,

.star

ting

.from.the.botto

m

.up..Deta

iled

.

info

rmation

.can.be.fou

nd

.in.[10

].

41.3.1 Physical Layer

Since.LonWorks.supports.dierent.communication.media,.the.physical layer.is.not.xed.to.a.specic.line.cod-

ing

.meth

od.

.Inst

ead,

.each.medi

um

.can.use.its.own.meth

od.

.For.exam

ple,

.die

rential Manchester coding

.is.

used.for.twis

ted

.pair.line

s,

.spre

ad spectrum modulation

.for.powe

r

.line

,

.and.freq

uency shi keying modulation

.

for.radi

o

.freq

uency

.comm

unication.

.A.spec

ial

.case.is.LonW

orks/IP,

.wher

e

.the.LonT

alk

.pack

et

.is.not.dire

ctly

.

modu

lated

.to.a.medi

um.

.Inst

ead,

.it.is.pack

ed

.into.an.IP.pack

et

.and.tran

smitted

.over.LAN.or.the.Inte

rnet.

41.3.2 Link Layer

e.next.layer.is.the.link layer.containing.the.MAC.sublayer..is.sublayer.handles.the.medium.access,.

whic

h

.is.real

ized

.by.the.so-c

alled

.pred

ictive

.p-pe

rsistent

.carr

ier

.sens

e

.mult

iple

.acce

ss

.(CSM

A)

.meth

od

.

Layer 7

(Application layer)

Application and

presentation layer

Application interface,

network management

Session layer

Request/response service

Transport layer

(Un-)Acknowledged service

Authentication server

Transaction control sublayer

Packet order, duplicate detection

Network layer

Connectionless, topology, router

Link layer

Frame, coding, CRC

MAC sublayer

CSMA, collision avoidance,

collision detection, priorities

Physical layer

Media specific protocols

LonTalk protocolOSI model

Layer 6

(Presentation layer)

Layer 5

(Session layer)

Layer 4

(Transport layer)

Layer 3

(Network layer)

Layer 2

(Link layer)

Layer 1

(Physical layer)

FIGURE 41.3 e.OSI. reference. model. and.their. corresponding. LonTalk. layers..(From.Loy,. D..et. al.. (eds.),.

Open

Control Networks—LonWorks/EIA-709 Technology,

.Kluw

er

.Acad

emic

.Publ

ishers,

.Bost

on,

.MA,.p..76,.gure.

4-2,.200

1.

.Wit

h

.kind.per

mission

.of.Spr

inger

.Sci

ence

.and.Bus

iness

.Med

ia.)

© 2011 by Taylor and Francis Group, LLC