Вставская Е.В. Архитектура ЭВМ, систем, сетей, лекции

Подождите немного. Документ загружается.

интерфейсу выполняет такие же операции ввода и вывода, как и при обмене с

памятью. Поэтому во многих микро- и мини-ЭВМ команды ввода - вывода

отсутствуют вообще и обмен с ПУ осуществляется с помощью обычных

пересылочных команд. Регистры ПУ в этом случае рассматриваются как

обычные ячейки ОЗУ, но им присваиваются адреса из определенного диапа-

зона адресов.

В тех случаях, если команды ввода-вывода есть, их исполнение

отличается только выдачей блоком сопряжения разных синхросигналов по

управляющим шинам интерфейса. В остальном работа процессора при этих

операциях не отличается от работы при выполнении обычных пересылок.

В ЭВМ общего назначения команды ввода - вывода инициируют работу

канала ввода-вывода. При проверке состояния канала или устройства по

командам ввода - вывода формируются значения признаков результата,

которые анализируются процессором с помощью команд условного перехода.

Сами операции ввода - вывода выполняются каналом.

1.6.4 Арифметико-логические устройства

Арифметическо-логические устройства предназначены для выполнения

арифметических и логических операций над информационными словами,

представленными в одной из допустимых для конкретного АЛУ форм

представления.

Арифметическо-логические устройства обязательно входят в состав

процессора и иногда включаются в состав других операционных устройств и

спецпроцессоров. Они характеризуются разрядностью, составом операций,

форматами обрабатываемых слов, способом построения и

функционирования, быстродействием, стоимостью, надёжностью и т. п. Если

АЛУ входит в состав процессора, то его разрядность определяется длиной

слова процессора и обычно либо совпадает с ней, либо кратна ей. Состав

61

операций АЛУ вытекает из его конкретного назначения в том устройстве, где

оно используется.

Арифметическо-логическое устройство процессора должно обеспечивать

выполнение всех операций арифметическо-логической группы. В случае

арифметических операций разрядность АЛУ определяет точность, с которой

выполняются эти операции.

На структуру и способ построения АЛУ в наибольшей степени влияет

формат обрабатываемых слов или типы данных, с которыми АЛУ оперирует.

В соответствии с типами данных различают АЛУ с фиксированной точкой,

плавающей точкой и десятичные АЛУ. В составе процессора всегда есть АЛУ

с фиксированной точкой. Десятичные АЛУ и АЛУ с плавающей точкой

добавляются в состав процессора обычно только в более мощных ЭВМ из

ряда ЭВМ одного типа. В менее мощных моделях эти операции выполняются

по подпрограммам.

По способу построения и функционирования АЛУ делятся на

параллельные, последовательные и параллельно - последовательные. Кроме

того, в зависимости от наличия или отсутствия внутренней памяти, АЛУ

делятся на комбинационные и накапливающие. Арифметическо-логические

устройства с фиксированной точкой в настоящее время строятся как

параллельные, т. е. элементарная операция АЛУ выполняется параллельно

над всеми разрядами обрабатываемого слова данных.

В последовательных АЛУ обрабатываемые слова данных участвуют в

операции бит за битом. Это замедляет выполнение операции, но позволяет

существенно экономить оборудование. Последовательная обработка

применяется редко, так как развитие микроэлектроники удешевило

оборудование и уменьшило его габариты настолько, что выигрыш от

последовательной обработки стал очень незначительным. Однако

комбинированная параллельно - последовательная обработка применяется

62

довольно широко. Например, по такому принципу часто строятся десятичные

АЛУ, в которых десятичные числа участвуют в операции тетрада за тетрадой.

Наибольшее распространение получили АЛУ с магистральной

структурой. Обычно в таких АЛУ четко можно выделить три точки:

- входы. куда подключаются первый и второй операнды;

- выход комбинационной схемы АЛУ, где получается результат

элементарной операции.

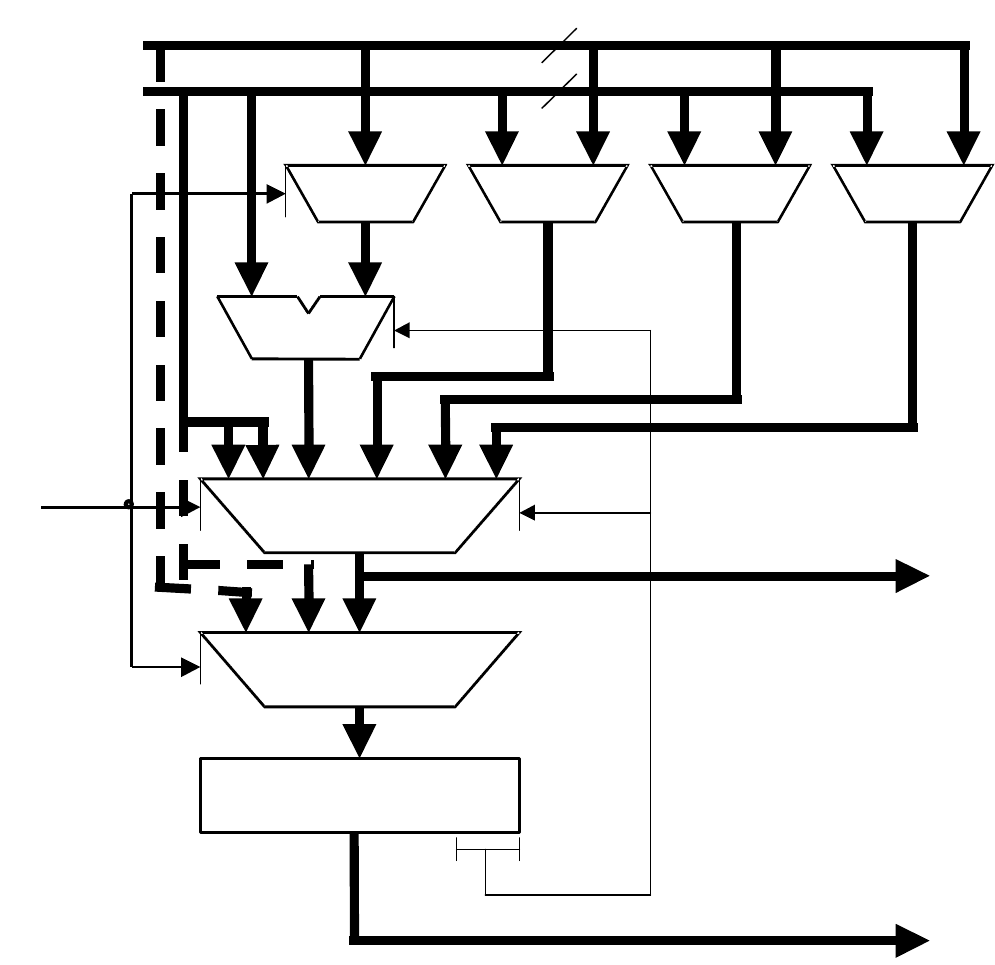

Операционный блок такого АЛУ обычно строится как комбинационная

схема и включает отдельные узлы, выполняющие операции, выходы которых

подключены к коммутатору, управляющему выбором результата. Пример

структурной схемы АЛУ комбинационного типа приведен на рис. 20. В этой

схеме СМ, К, Д, М2 обозначены соответственно сумматор и схемы,

выполняющие поразрядные операции конъюнкцию, дизъюнкцию,

суммирования по модулю 2, СП - схема преобразования операнда 2 на входе

сумматора, КМ- коммутатор результата, СВП - схема выработки признаков

результата, РП - регистр признаков результата.

Комбинационные блоки СМ, К, Д, М2 в любой момент времени

вырабатывают какой-то результат с кодами, установленными на входных

шинах. Но на выход выдается только один результат, определяемый кодом на

шине «операция», который управляет выходным коммутатором. Операнд 1

также поступает на входы коммутатора со сдвигом разрядов влево и вправо,

что позволяет, задав соответствующую операцию, передать на выходные

шины сдвинутый влево или вправо код с шин операнда 1. Схема

преобразования операнда 2 СП предназначена для выполнения над операндом

2 операции поразрядной инверсии, а также операций подстановки вместо

операнда 2 кодов, равных единице или нулю во всех разрядах. Это необходимо

для выполнения с использованием сумматора операций вычитания, прямого

и обратного счёта единиц. Схема СП также может строиться на основе

коммутатора.

63

Операнд 2 n

Операнд 1 n

СП

М2

К

Д

СМ

КМ

СВП

Результат

О

п

е

р

а

ц

и

я

РП

m . . . 0

Признаки

Рис. 20 Схема операционного блока АЛУ комбинационного типа

На рис. 20 не показаны схемы, управляющие подачей переноса на

младший разряд сумматора. Особо отмечена только связь от регистра

признаков результата (РП).

В состав процессоров микро- и мини-ЭВМ включаются обычно

комбинационные АЛУ, похожие на изображенные на рис. 20. К входной и

выходной магистрали такого АЛУ подключаются регистры из блока

регистров процессора. Естественно, что набор операций комбинационного

64

АЛУ не может включать длинных операций, требующих запоминания

промежуточных результатов (типа умножения - деления), и включает

операции, выполнение которых возможно комбинационной схемой (сложение,

вычитание, сдвиги, поразрядные операции и т. п.). Если необходимо

реализовать длинные операции, то в составе АЛУ должны обязательно быть

регистры. Если в системе команд процессора есть длинные операции, то они

обычно выполняются с использованием имеющихся регистров и алгоритмы

таких операций реализуются общим устройством микропрограммного управ-

ления процессора. Поэтому в составе процессора наиболее часто под АЛУ

подразумевается сам комбинационный операционный блок. Выделить всё

АЛУ в чистом виде обычно не удается.

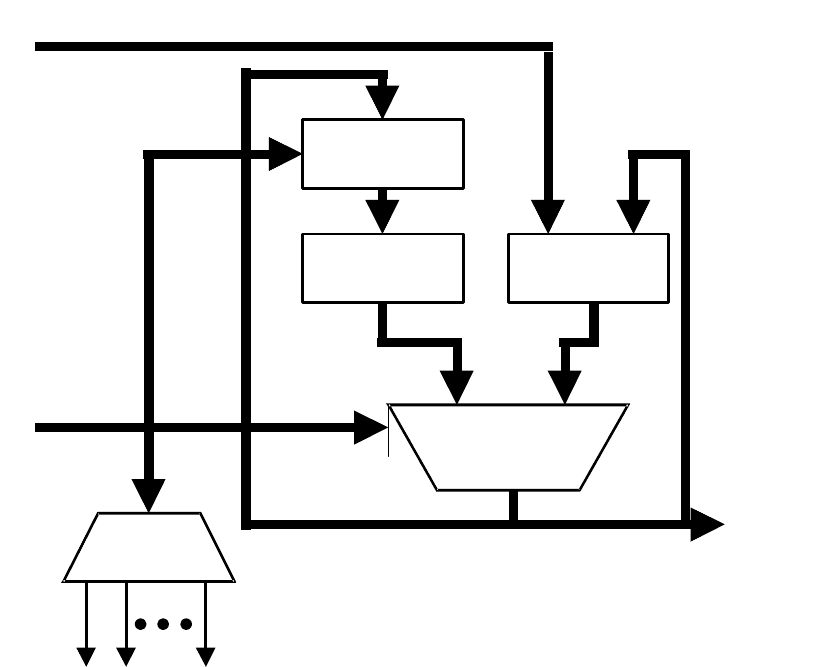

На рис. 21 изображена схема АЛУ с магистральной структурой, которая

может быть использована в составе процессора. Входная и выходная шины

данных соединяются с блоком БС (см. рис.13), а шина микроопераций и

признаки соединяются с БУ. Регистры P

1

, P

2

, …,P

N

- регистры блока регистров

процессора. Каждый регистр имеет схемы приёма с выходной шины

операционного блока (ОБ) и схемы подключения к входным шинам 1 и 2.

Управление регистрами осуществляется сигналами с дешифратора кода

микрооперации DC, связь с внешней средой - через входную и выходную

шины данных. Обычно схемы регистров допускают одновременный (в одном

такте) съём информации с них и запись новой информации, это отражается в

записи операторов присваивания, Р1:=Р1+Р2.

Любая микрооперация АЛУ включает информацию о подключении

регистров к шинам 1 и 2, записи результата на регистр и операции в

комбинационном

65

Р

1

Р

2

Р

N

ОБ

АЛУ

DC

Входная

шина

данных

Входная шина

микроопераций

Магистраль 1

Магистраль 2

Магистраль 3

Шина признаков

Выходная

шина

данных

Рис. 21 Схема АЛУ с магистральной структурой

блоке АЛУ, т. е. в микрооперацию входят три номера регистра и код

операции, в соответствии с которыми дешифратор формирует внутренние

управляющие сигналы.

Основное достоинство АЛУ с магистральной структурой заключается в

его универсальности. В то же время некоторые функции реализуются

неэффективно. Например, сдвиг с передачей бита из регистра в регистр, как

правило, не может быть сделан за 1 такт. Выдвинутый разряд запоминается в

виде признака С в регистре РП (см. рис. 20), а затем в новом такте вдвигается

в другой регистр на место освобождающегося. Это иногда существенно

снижает быстродействие АЛУ.

Так как структура такого АЛУ типовая, то она может быть изготовлена в

виде БИС. Обычно применяется ее «вертикальный» разрез (на одном

66

кристалле выполняются n=2, 4, 8,… разрядов всех регистров

комбинационного блока и дешифратор). В операционном блоке

предусматриваются входные и выходные цепи переносов при сложении и

сдвигах. Такая n-разрядная секция АЛУ называется процессорной секцией.

Соединение нескольких процессорных секций позволяет получить

многоразрядную структуру, непосредственно пригодную для построения

центрального процессора ЭВМ, а также для построения законченных АЛУ,

используемых независимо (например, в арифметических расширителях).

Структура АЛУ, показанная на рис. 21, неудобна тем, что в ней

используются регистры. При большом их количестве выгоднее применять

стандартные ЗУ. Так как в каждый момент времени из ЗУ может быть

выбрано только одно слово из одного адреса, то в АЛУ на основе блока

памяти необходимы также дополнительные регистры, с которыми

выполняется расширенный набор операций. Схема АЛУ на основе блока

памяти приведена на рис. 22. К входным шинам операционного блока

подключаются рабочий регистр, называемый регистром-аккумулятором АК,

и выход блока памяти БП. В микрооперации указывается адрес слова блока

памяти, операция АЛУ и место занесения результата. Результат может быть

возвращен в БП на место операнда, но при этом обязательно использование

буферного регистра РБ, обеспечивающего развязку входа и выхода блока

памяти. Регистр РБ может быть предусмотрен и на входе БП. С целью

увеличения функциональных возможностей АЛУ обычно состав операций с

регистрами РБ и АК расширен и включает операции сдвига, инверсии,

занесения информации с внешних входных шин, подключения к выходным

шинам и т. п. Часто содержимое регистров перед подачей на операционный

блок умножается на маску и этим обеспечивается возможность выделения

разрядов, участвующих операции. Маска может подаваться с внешних шин

или с регистра маски. Эти возможности не отражены на рис. 22.

67

В микропроцессорных БИС АЛУ в блоках памяти предусматривается

иногда две независимых схемы селекции и соответственно две системы

адресных шин и два буферных регистра. Запись результата возможна только

по одному из адресов. На входе и выходе операционного блока АЛУ

предусматриваются ком-

ОБ

АЛУ

АК

РБ

БП

DC

Входная шина данных

М

и

к

р

о

о

п

е

р

а

ц

и

я

Выходная

шина

данных

Рис.22 Схема АЛУ на основе блока памяти

мутаторы, обеспечивающие различные комбинации источников и

приёмников информационных слов. Коммутаторы управляются

микрооперацией. Интерфейсные шины АЛУ в этом случае обычно

подключаются через коммутатор к операционному блоку (а не к регистру АК,

как показано на рис. 22), чем обеспечивается возможность участия в операции

операндов непосредственно с входных шин. Это уменьшает число паразитных

пересылочных операций.

68

Исторически более ранней является структура АЛУ с жесткими или

непосредственными связями. Она позволяет получить большее

быстродействие, но обладает меньшей универсальностью. В настоящее время

структура с непосредственными связями используется для выполнения одной

операции или небольшого числа операций с наивысшим быстродействием.

Арифметическо- логическое устройство с непосредственными связями

представляет собой набор регистров и операционных блоков, жестко

соединенных между собой для выполнения заданного набора операций.

Синтез структуры и логических схем АЛУ с непосредственными связями

выполняется по исходным алгоритмам заданного множества операций или

операции.

1.6.5 Система прерываний процессора

Система прерываний процессора предназначена для организации

оперативной реакции процессора на события в самой ВС или ЭВМ и во

внешней среде. Система прерываний позволяет исключить из программы

команды опроса готовности или состояния периферийных устройств и

обеспечивает возможность параллельной работы процессора по выполнению

программы и периферийных устройств по выполнению операций ввода и

вывода данных. С этой целью в интерфейс процессора вводятся специальные

шины, по которым передаются запросы прерывания от устройств. Запросы

возникают при завершении операций по вводу - выводу (готовности уст-

ройств), при возникновении аварийных ситуаций, периодически (например,

по синхроимпульсам системных часов), асинхронно по событиям во внешней

среде.

Процессор после выполнения каждой команды делает опрос состояния

шин запроса прерываний. Если при опросе обнаруживается наличие запроса

прерывания, то процессор переключается на программу обслуживания

69

прерываний (прерывающую программу). При переключении в памяти

запоминается состояние процессора с тем, чтобы обеспечить возможность

возврата к прерванной программе. Причем прерванная программа должна

работать так же, как и при отсутствии прерываний. Для этого в процессоре

предусматривается специальная аппаратура. Состояние процессора определя-

ется состоянием его программно- доступных регистров и признаков

результата. В момент прерывания процессор должен переключиться на новую

программу. Для этого он должен сформировать новое содержимое счетчика

команд, но для обеспечения возврата текущее содержимое счетчика

необходимо запомнить. Прерывающая программа при своей работе меняет

состояние признаков результата, выработанных последней командой

прерванной программы. Если их не сохранить, то это может нарушить работу

прерванной программы. Если допустимы прерывания из нескольких

источников, имеющих разный приоритет, возможны вложенные или

многоуровневые прерывания, когда выполнение прерывающей программы

прерывается более высокоприоритетной программой. При обработке

высокоприоритетного прерывания все более низкоприоритетные прерывания

не должны оказывать воздействия на процессор.

Процессор после выполнения каждой команды делает опрос состояния

шин запроса прерываний. Если при опросе обнаруживается наличие запроса

прерывания, то процессор переключается на программу обслуживания

прерываний (прерывающую программу). При переключении в памяти

запоминается состояние процессора с тем, чтобы обеспечить возможность

возврата к прерванной программе. Причем прерванная программа должна

работать так же, как и при отсутствии прерываний. Для этого в процессоре

предусматривается специальная аппаратура. Состояние процессора определя-

ется состоянием его программно- доступных регистров и признаков

результата. В момент прерывания процессор должен переключиться на новую

программу. Для этого он должен сформировать новое содержимое счетчика

70