Механов, В.Б. Особенности архитектуры универсальных микропроцессоров

Подождите немного. Документ загружается.

41

Сегментные регистры хранят базовые (начальные) адреса

сегментов памяти: кодового сегмента CS (Code Segment), в кото-

ром содержится программа; стекового сегмента SS (Stack Seg-

ment); сегмента данных DS (Data Segment); дополнительного

сегмента ES (Extended Segment), в котором обычно содержатся

данные. Наличие сегментных регистров обусловлено разделени-

ем памяти на сегменты и используемым способом формирова-

ния адресов памяти.

Сумматор адресов осуществляет вычисление 20-битовых

физических адресов путем суммирования смещения и содержи-

мого соответствующего сегментного регистра, которое дополня-

ется четырьмя нулевыми младшими разрядами.

Указатель команд IР (Instruction Pointer) хранит смеще-

ние следующей команды в текущем кодовом сегменте, т.е. ука-

зывает на следующую по порядку команду. Он является анало-

гом стандартного программного счетчика с той лишь разницей,

что его содержимое определяет адрес команды лишь в совокуп-

ности

с содержимым регистра CS, если же CS заполнен нулями, анало-

гия становится полной. Модификация IР осуществляется шин-

ным интерфейсом так, что при обычной работе IР содержит

смещение того командного слова, которое шинный интерфейс

будет выбирать из памяти. Оно не совпадает со смещением оче-

редной команды (находящейся в этот момент на выходе очереди

команд), которую будет выполнять операционное устройство.

Поэтому при запоминании содержимого IР в стеке, например

при вызове подпрограмм, оно автоматически корректируется,

чтобы адресовать следующую команду, которая будет выпол-

няться. Эта особенность является следствием опережающей вы-

борки команд. Непосредственный доступ к IР имеют команды

передачи управления.

42

2.4. Адресное пространство МП

2.4.1. Размещение байтов и слов в памяти

Существует несколько соглашений, определяющих меха-

низм адресации в микропроцессоре.

1. Память логически организована как одномерный массив

байтов, каждый из которых имеет 20-битовый физический адрес

в диапазоне 00000–FFFFFh.

2. Любые два смежных байта в памяти могут рассматри-

ваться как 16-битовое слово.

3. Младший байт слова имеет меньший адрес, а старший –

больший.

4. Адресом слова считается адрес его младшего байта. Та-

ким образом, 20-битовый адрес памяти может рассматриваться

и как адрес байта, и как адрес слова.

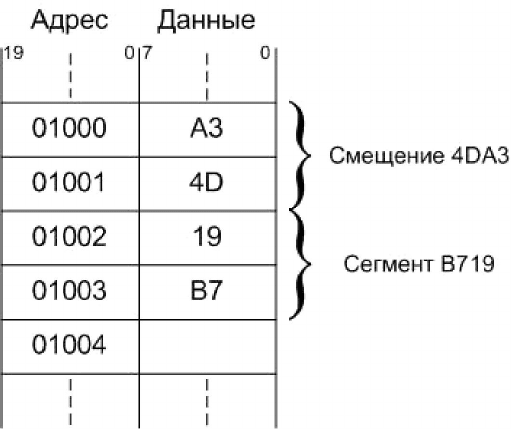

5. Полная информация, необходимая для определения фи-

зического адреса, содержится в адресном объекте «сегмент :

смещение», который называется указателем адреса и содержит

адрес сегмента и внутрисегментное смещение. Для запоминания

указателя адреса требуется два слова памяти, причем слово

с меньшим адресом всегда содержит смещение, а слово с боль-

шим адресом базовый – адрес сегмента (рис. 2.5). Каждое слово

хранится обычным образом, т.е. по принципу «младший байт –

по меньшему адресу».

43

Рис. 2.5. Пример размещения адресной информации в памяти

6. Команды, байты и слова данных можно свободно раз-

мещать по любому адресу, что позволяет экономить память бла-

годаря ее плотной упаковке. Однако для экономии времени вы-

полнения программы целесообразно размещать слова данных в

памяти по четным адресам, так как МП передает такие слова за

один цикл шины. Слово с четным адресом называется выров-

ненным на границе слов. Слова с нечетными адресами (невы-

ровненные) также допустимы, но для их передачи требуются два

цикла шины, что снижает производительность МП. Каждый

цикл имеет четыре обязательных такта Т. Отметим, что шинный

интерфейс инициирует необходимое для выборки слова число

обращений к памяти автоматически, так что двукратное обра-

щение к памяти не требует специального указания в программе.

Особенно важно иметь выровненные слова для операций со сте-

ком, так как в них участвуют только слова. Следовательно, ука-

затель стека SP необходимо всегда инициализировать на четный

адрес.

7. Команды всегда выбираются словами по четным адре-

сам, за исключением первой выборки после передачи управле-

ния по нечетному адресу, когда выбирается один байт. Поток

команд разделяется на байты при дополнении очереди команд

внутри МП, так что выравнивание команд не влияет на произво-

дительность и поэтому не используется.

2.4.2. Сегментация памяти и вычисление адре-

сов

Пространство памяти емкостью 1 Мб представляется как

набор сегментов, определяемых программным путем. Сегмент

состоит из смежных ячеек памяти и является независимой и от-

дельно адресуемой единицей памяти емкостью 64 Кб. Каждому

сегменту программой назначается начальный (базовый) адрес,

являющийся адресом первого байта сегмента в пространстве

памяти. Начальные адреса четырех сегментов, выбранных в ка-

честве текущих, записываются в сегментные регистры CS, DS,

SS и ES, тем самым фиксируются текущие сегменты кода (про-

44

граммы), данных, стека и дополнительных данных. Для обраще-

ния

к командам и данным, находящимся в других сегментах, необ-

ходимо изменять содержимое сегментных регистров, что позво-

ляет использовать все пространство памяти емкостью 1 Мб. Сег-

ментные регистры инициализируются в начале программы пу-

тем засылки в них соответствующих констант. Частный случай

загрузки всех сегментных регистров нулями приводит к органи-

зации памяти, характерной для 8080, т.е. фактически к отказу от

сегментации памяти.

В сегментном регистре хранится 16 старших битов

20-битового начального адреса сегмента. Четыре младших бита

адреса принимаются равными нулю и дописываются справа к

содержимому сегментного регистра при вычислении физических

адресов ячеек памяти. Поэтому начальные адреса сегментов все-

гда кратны 16. Поскольку других ограничений на размещение

сегментов в памяти нет, сегменты могут быть соседними (смеж-

ными), неперекрывающимися, частично или полностью пере-

крывающимися. Физическая ячейка памяти может принадле-

жать одному или нескольким сегментам.

Физический адрес ячейки памяти представляет 20-

битовое число в диапазоне 0–FFFFFh, которое однозначно опре-

деляет положение каждого байта в пространстве памяти емко-

стью

1 Мб. Так как МП 8086 является 16-битовым, то все операции

при вычислении физического адреса производятся с 16-бито-

выми адресными объектами.

Логический адрес ячейки памяти состоит из двух 16-бито-

вых беззнаковых значений: начального адреса сегмента, кото-

рый называется также просто базой или сегментом, и внутри-

сегментного смещения, которое определяет расстояние от нача-

ла сегмента до этой ячейки. Для вычисления физического адреса

база сегмента сдвигается влево на четыре бита и суммируется со

смещением, как показано на рис. 2.6, где также приведены воз-

можные источники компонентов логического адреса (ЕА – эф-

45

фективный адрес, вычисляемый в соответствии с заданным спо-

собом адресации).

Рис. 2.6. Пример вычисления физического адреса

Перенос из старшего бита, который может возникнуть при

суммировании, игнорируется. Это приводит к так называемой

кольцевой организации памяти, при которой за ячейкой с мак-

симальным адресом FFFFFh следует ячейка с нулевым адресом.

Аналогичную кольцевую организацию имеет и каждый сегмент.

Команды всегда выбираются из текущего сегмента кода в

соответствии с логическим адресом CS:IP. Стековые команды

всегда обращаются к текущему сегменту стека по адресу SS:SP.

Если при вычислении адреса ЕА используется регистр ВР, то

обращение производится также к стековому сегменту. В послед-

нем случае принцип стека «первый пришел – последним вышел»

игнорируется? и ячейки стекового сегмента рассматриваются

как ОЗУ с произвольной выборкой, что обеспечивает большую

гибкость в использовании этих ячеек.

Операнды, как правило, размещаются в текущем сегменте

данных, и обращение к ним организуется по адресу DS:EA. Од-

нако программист может заставить МП обратиться к перемен-

ной, находящейся в другом текущем сегменте. Считается, что

цепочка-источник находится в текущем сегменте данных, а ее

46

смещение задается регистром SI. Цепочка-получатель обяза-

тельно располагается в текущем дополнительном сегменте, а

смещение берется из регистра DI. Команды обработки цепочек

автоматически модифицируют содержимое индексных регист-

ров SI и DI по мере продвижения по цепочке в направлении, со-

ответствующем флагу DF.

Сегментная структура памяти обеспечивает возможность

создания позиционно независимых или динамически переме-

щаемых программ, что необходимо в мультипрограммной среде

для эффективного использования оперативной памяти. Чтобы

обеспечить позиционную независимость, все смещения в про-

грамме должны задаваться относительно фиксированных значе-

ний, содержащихся в сегментных регистрах. Это позволяет про-

извольно перемещать программу в адресном пространстве памя-

ти, изменяя только содержимое сегментных регистров.

Стек, как обычно, организуется в ОЗУ, и его положение

определяется содержимым регистров SS и SP. При каждом об-

ращении к стеку пересылается одно слово, причем содержимое

SP модифицируется автоматически: при записи (включении) в

стек оно уменьшается на два, при чтении (извлечении) из стека

– увеличивается на два.

При всех достоинствах принятой в 8086 организации памя-

ти она имеет некоторый недостаток, заключающийся в трудно-

сти манипуляции физическими адресами при необходимости их

программной обработки.

2.5. Организация ввода-вывода

Ввод и вывод данных может осуществляться двумя спосо-

бами: с использованием адресного пространства ввода-вывода и

с использованием общего с памятью адресного пространства,

т.е. с отображением на память.

При первом способе применяются специальные команды

IN (ввод) и OUT (вывод), которые обеспечивают передачу дан-

ных между аккумуляторами AL или АХ и адресуемыми портами.

При выполнении этих команд вырабатывается сигнал М/IO = 0,

47

который идентифицирует выбор пространства ввода-вывода и

в совокупности с сигналами WR и RD позволяет сформировать

системные сигналы IOW и IOR для управления операциями за-

писи данных в порт и чтения из порта.

Команды IN и OUT могут использовать прямую адреса-

цию, когда адрес порта содержится в виде константы во втором

байте команды, и косвенную адресацию, когда адрес располага-

ется

в регистре DX. В первом случае можно адресовать по 256 пор-

тов для ввода и вывода данных. Во втором обеспечивается ад-

ресное пространство до 64К 8-битовых портов или до 32К 16-

битовых портов. Косвенная адресация позволяет вычислять ад-

реса портов при выполнении программы и удобна при организа-

ции вычислительных циклов для обслуживания нескольких пор-

тов с помощью одной процедуры.

Восемь ячеек F8–FF в пространстве ввода-вывода зарезер-

вированы для системных целей, и использовать их в приклад-

ных программах не рекомендуется.

При втором способе адреса портов размещаются в общем

адресном пространстве, и обращение к ним не отличается от об-

ращения к ячейкам памяти. Это повышает гибкость программи-

рования, так как для ввода-вывода можно использовать любую

команду с обращением к памяти при любом способе адресации.

Так, команда MOV позволяет передавать данные между любым

общим регистром или ячейкой памяти и портом ввода-вывода, а

логические команды AND, OR, XOR и TEST позволяют манипу-

лировать битами в регистре порта. Однако при этом следует

учитывать, что команды с обращением к памяти имеют больший

формат и выполняются дольше, чем простые команды IN и OUT.

Микропроцессор может передавать по шине байт или сло-

во в/из внешнего устройства. Чтобы слово передавалось за один

цикл шины, адрес ВУ должен быть четным. Адрес байтового ВУ

может быть четным или нечетным, и соответственно порты этих

внешних устройств подключаются к линиям младшего и стар-

шего байта шины данных. Для раздельного обращения к этим

48

портам дешифрирование адресов осуществляется с учетом сиг-

налов на линиях ВНЕ и А0.

2.6. Организация прерываний

2.6.1. Общие сведения

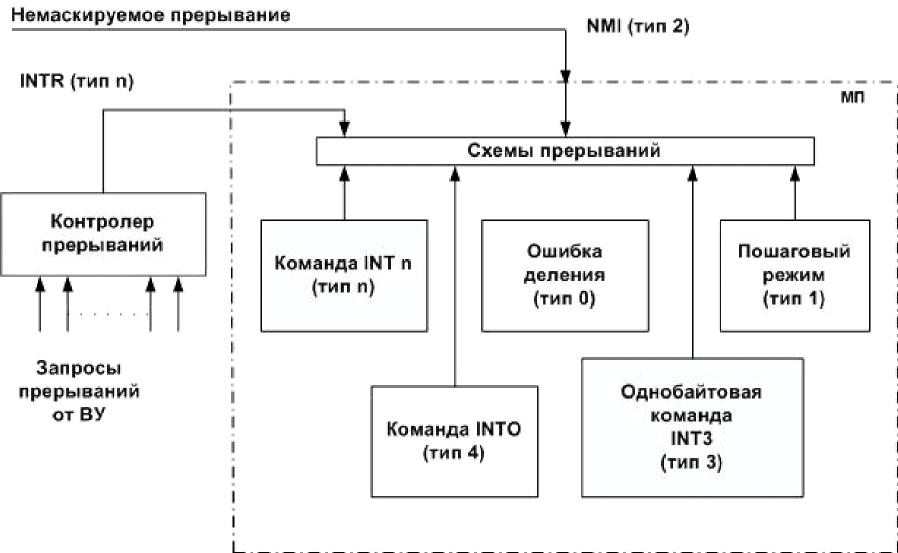

Микропроцессор 8086 имеет эффективную систему преры-

ваний, в которой каждому прерыванию поставлен в соответст-

вие код (от 0 до 255), идентифицирующий тип прерывания.

Прерывания могут инициироваться внешними устройствами

(внешние прерывания) или командами программных прерыва-

ний, а в некоторых ситуациях - автоматически самим МП (внут-

ренние прерывания). Возможные источники прерываний пока-

заны на рис. 2.7.

Прерывание заставляет МП временно прекратить выпол-

нение текущей программы и перейти к выполнению подпро-

граммы обработки прерывания, которая считается более важной

или срочной. Возобновление прерванной программы должно

быть произведено так, как будто прерывание отсутствовало.

Для этого в стеке запоминается адрес возврата (CS и IР) и

содержимое регистра флагов F, а также содержимое тех регист-

ров, которые потребуются для выполнения подпрограммы обра-

ботки прерывания. Содержимое регистров CS, IР и F запомина-

ется и восстанавливается автоматически, а для запоминания и

последующего восстановления содержимого других регистров

МП должны быть предусмотрены соответствующие команды

в начале и конце подпрограммы обработки прерываний. Следует

отметить, что в стек включается скорректированное содержимое

указателя команд IР, соответствующее адресу команды, перед

которой МП начал обслуживать прерывание. Необходимость

коррекции вызвана тем, что IР адресует команды с опережением

из-за существования внутренней очереди команд.

49

Рис. 2.7. Возможные источники прерываний

2.6.2. Внешние прерывания

Запросы на внешние прерывания поступают в МП по двум

входам: INTR и NMI, и сами прерывания делятся, соответствен-

но, на маскируемые и немаскируемые. Запросы на маскируемые

прерывания от ВУ обычно поступают на входы программируе-

мого контроллера прерываний, который формирует сигнал, по-

даваемый на вход INTR.

Когда устанавливается сигнал INTR = 1, действия МП

зависят от состояния флага IF разрешения прерываний. Однако

до завершения текущей команды МП, как правило, не предпри-

нимает никаких действий.

Если IF = 0, т.е. прерывания по входу INTR запрещены

(замаскированы), МП игнорирует запрос прерывания и перехо-

дит к следующей команде. Микропроцессор не запоминает со-

стояние сигнала INTR, поэтому этот сигнал должен оставаться

активным, пока прерывающее ВУ не получит сигнала подтвер-

ждения INTA или само не снимет запрос.

Если IF = 1, то МП распознает запрос прерывания и обра-

батывает его. Состоянием флага IF программист может управ-

50

лять с помощью команд STI (установка) и CLI (сброс). Кроме

того, программируемый контроллер прерываний может осуще-

ствлять селективное маскирование запросов прерывания от от-

дельных устройств, если в контроллер послан соответствующий

приказ.

Микропроцессор подтверждает запрос прерывания, вы-

полняя два последовательных цикла INTA.

Имеется несколько случаев, когда сигнал INTR распознает-

ся только при завершении следующей команды. Имеются два

особых случая, когда запрос прерывания распознается во время

выполнения команд, относящихся к цепочечной команде с по-

вторением и к команде WAIT, которые могут выполняться в те-

чение значительного времени. В этих случаях прерывания вос-

принимаются после любой законченной цепочечной операции

(т.е. после очередной операции с элементом цепочки) или после

цикла проверки сигнала на входе TEST (каждый цикл проверки

занимает время 5Т).

Запросы на немаскируемое прерывание поступают по

входу NMI и обычно используются для прерывания работы МП

при «катастрофических» событиях, требующих немедленной ре-

акции, таких как аварийное пропадание питания, обнаружение

ошибки памяти и т.д. Вход NMI воспринимает переход сигнала

от низкого уровня к высокому (положительный фронт), чтобы

текущая программа не прерывалась от одного сигнала NMI = 1

несколько раз. Запросы NMI запоминаются в МП и имеют более

высокий приоритет, чем прерывания по входу INTR. Обработка

немаскируемого прерывания не зависит от состояния флага IF.

Немаскируемому прерыванию присваивается фиксированный

код типа 2, который автоматически формируется внутри МП.

Поэтому в ответ на NMI циклы шипы подтверждения прерыва-

ния INTA не формируются, что ускоряет реакцию МП на запро-

сы немаскируемых прерываний.

Если, например, одновременно возникают немаскируемое

и маскируемое прерывания, МП начинает выполнение немаски-

руемого прерывания как имеющего высший приоритет и маски-

рует внешние прерывания сбросом флага IF. В этом случае за-