Гласман К.Ф., Алексеева Л.А., Покопцева М.Н. Цифровые устройства и микропроцессоры (часть 2)

Подождите немного. Документ загружается.

ПОСЛЕДОВАТЕЛЬНОСТНЫЕ УСТРОЙСТВА

11

4.2. Счетчики

Счетчиками называются устройства для счета числа импульсов.

Каждый счетчик представляет собой схему, для которой установлена связь

между числом поступивших на вход импульсов и кодовой комбинацией,

появившейся на выходах. Если число различных комбинаций выходных

переменных, определяющих состояние схемы, равно , то с помощью

счетчика можно считать число импульсов в диапазоне от 0 до

n

)1(

−

n

.

Количество различных состояний схемы определяет модуль счета.

Взаимосвязь между числом входных импульсов и входным кодом

может быть произвольной. На практике выбирают такой способ

кодирования, при котором обеспечивается удобство и простота

выполнения различных операций с выходными кодовыми словами.

Наиболее распространенным является двоичное кодирование, при котором

число импульсов отображается в двоичном коде. При этом возможны

различные направления счета. Например, после каждого входного

импульса выходное число увеличивается на единицу. Такой счетчик,

ведущий прямой счет, называется суммирующим. Вычитающий счетчик

производит обратный счет. Число, представляемое выходным кодом этого

счетчика, уменьшается на единицу после каждого входного импульса.

Реверсивный счетчик может работать в режимах прямого и обратного

счета.

Схемы счетчиков создаются на базе триггеров. JK-триггер при

J=K=1 представляет собой простейшую счетную схему, имеющую два

состояния (рис. 2.18 [1]). Из одного состояния в другое она переходит под

действием входного импульса. Ее модуль счета равен двум. Увеличение

модуля счета может быть достигнуто объединением нужного числа

триггеров в единую систему. Различные счетчики отличаются друг от

друга главным образом способом связей между триггерами.

4.2.1. Асинхронный двоичный счетчик

В двоичном счетчике число поступивших импульсов отображается

в двоичном коде. Взаимосвязь между числом импульсов и кодовыми

комбинациями выходных переменных для суммирующего

счетчика с модулем 16 приведена в таблице 4.2.

n

03

QQ −

Анализ таблицы позволяет отметить следующее:

− переменная

0

Q

меняет свое значение после каждого входного

импульса:

12

− переменная

i

Q

(

1≥i

) меняет свое значение тогда, когда

переменная в соседнем младшем разряде

1−i

Q

переходит из

единичного состояния в нулевое.

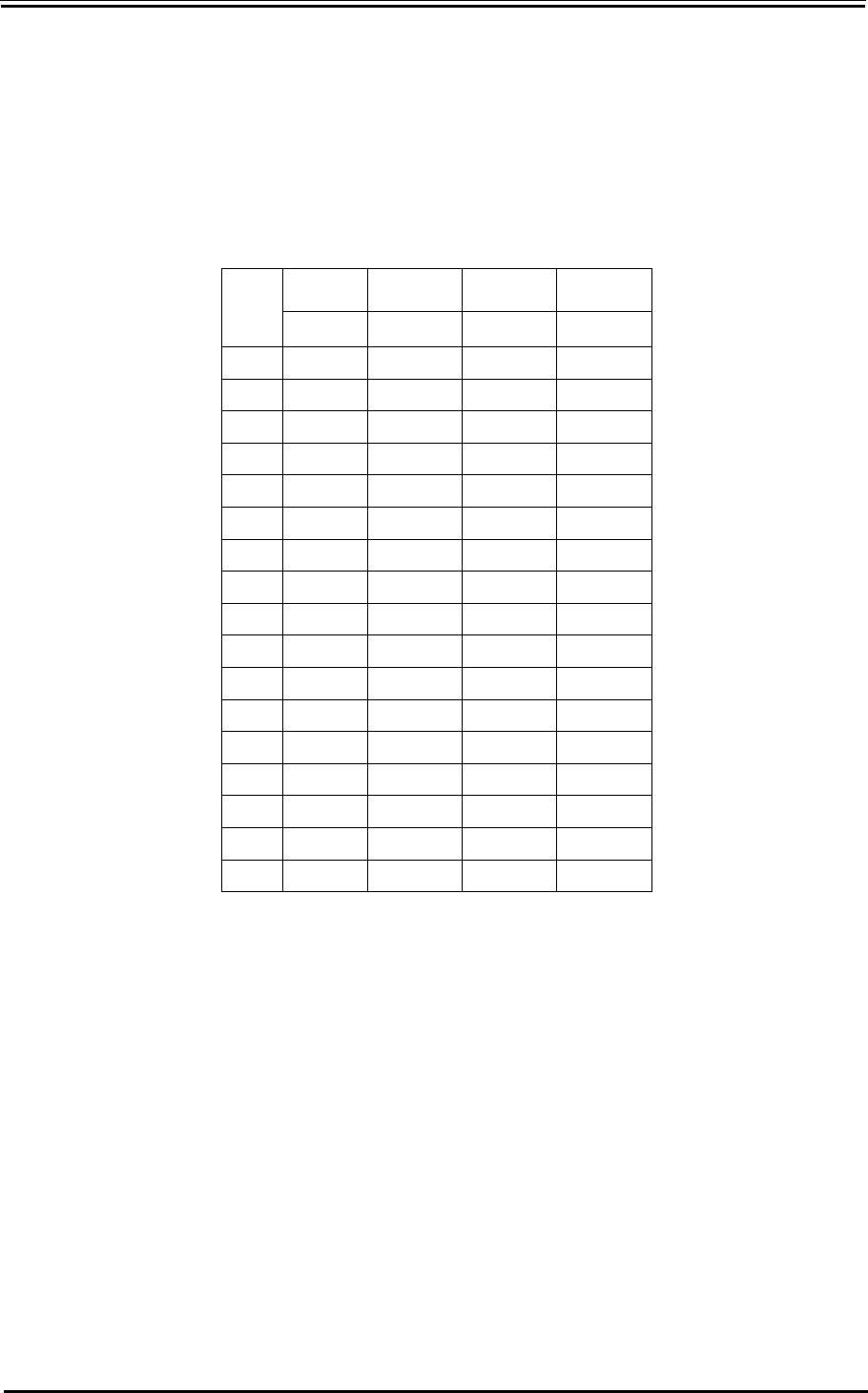

Таблица 4.2

Таблица состояний 4-разрядного двоичного суммирующего

счетчика

3

Q

2

Q

1

Q

0

Q

n

3

2

2

2

1

2

0

2

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

10 1 0 1 0

11 1 0 1 1

12 1 1 0 0

13 1 1 0 1

14 1 1 1 0

15 1 1 1 1

16 0 0 0 0

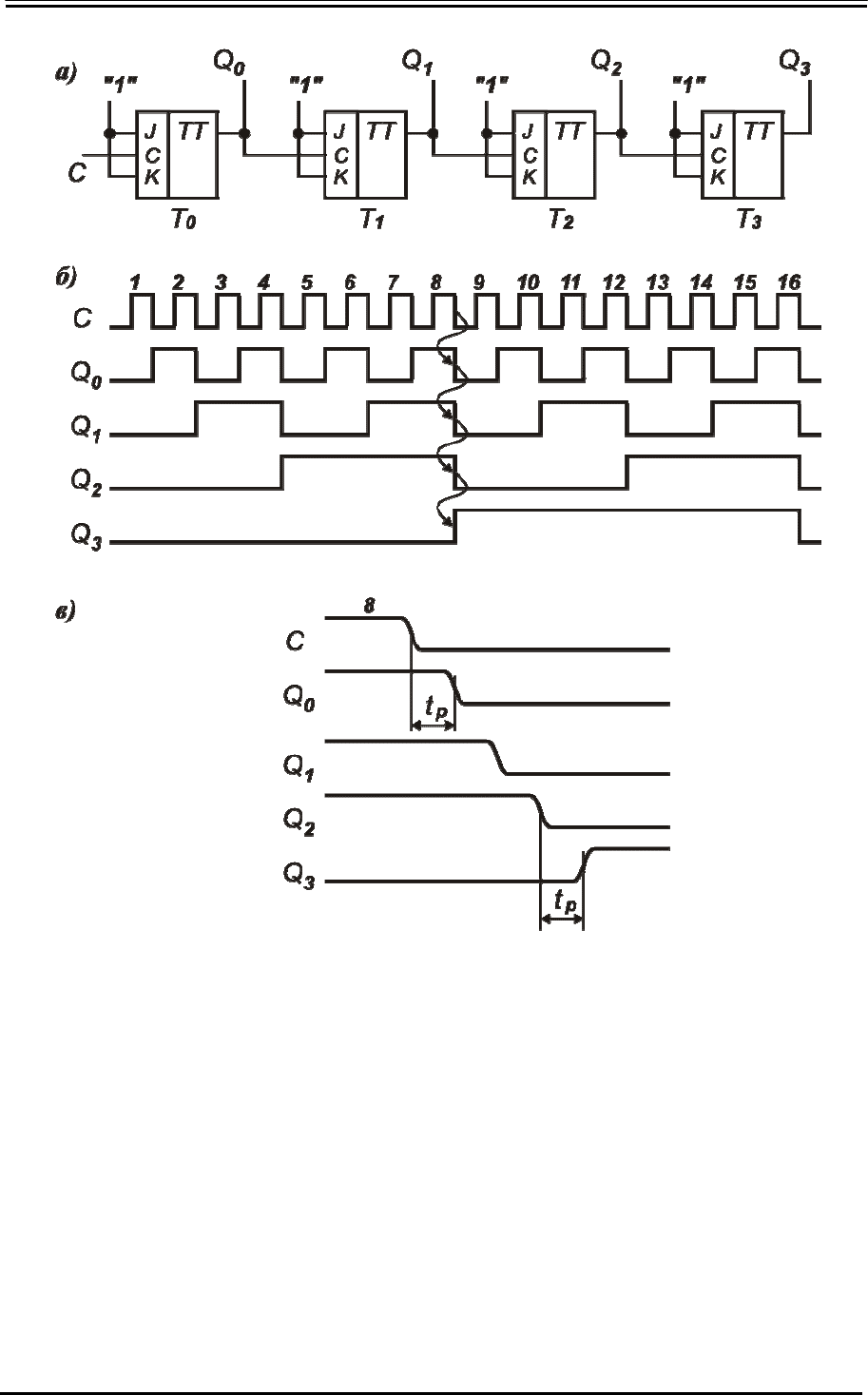

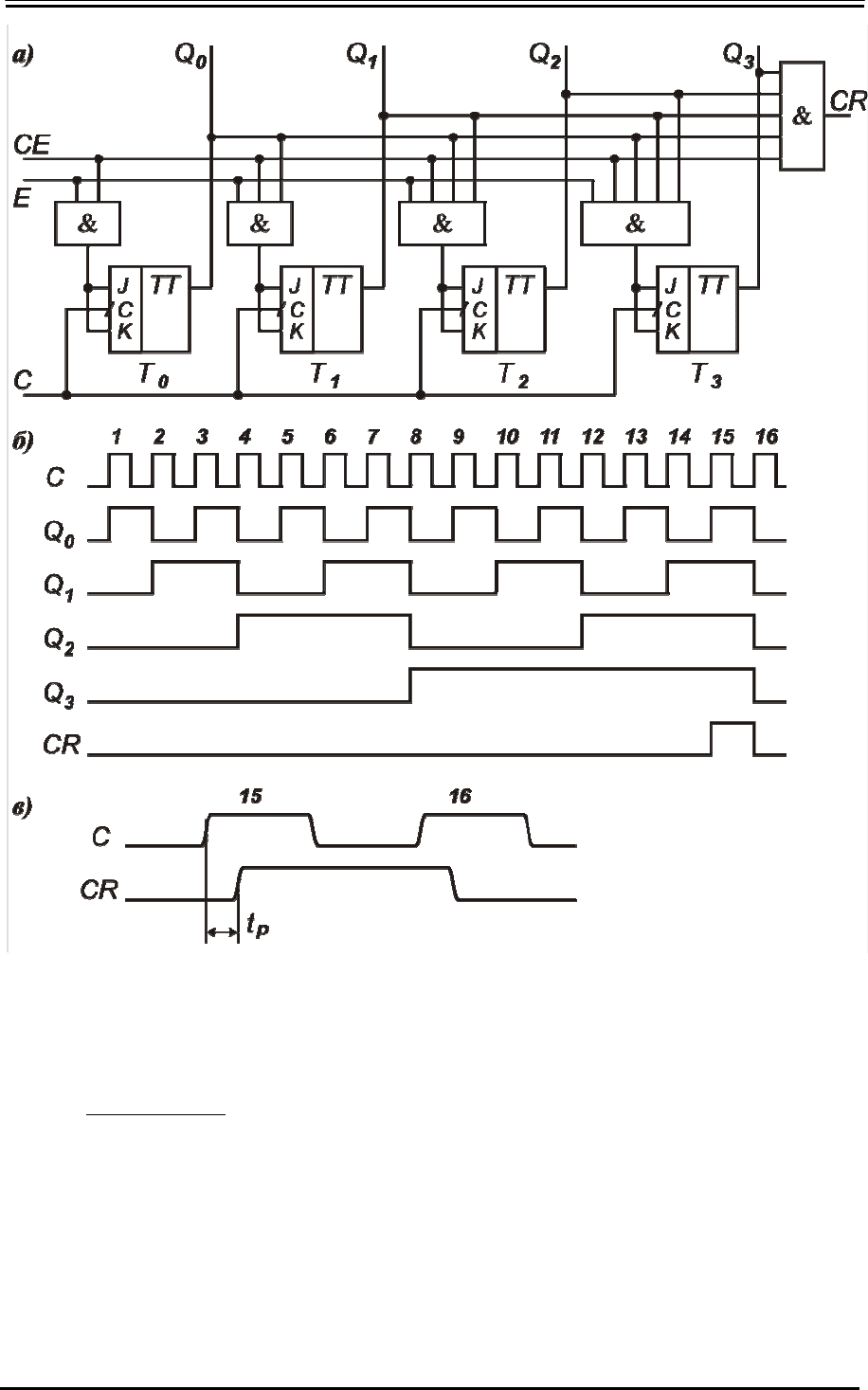

Эти закономерности реализованы в схеме, показанной на рис.4.7.

JK-триггер типа M-S работает так, как показано на рис. 2.18 [1], т.е.

срабатывает по срезу каждого импульса . Следующий триггер

переключается по отрицательному перепаду выхода . и т.д. (рис. 4.7 б).

До 15-го импульса счет проходит в соответствии с таблицей. После

каждого 16-го импульса на всех выходах устанавливаются нули, и счетчик

возвращается в исходное состояние. Но при этом отрицательный перепад

мог бы привести к переключению младшего триггера счетчика

следующей ступени, т.е. произошел бы перенос единицы в разряд счетчика

с весовым коэффициентом 2

4

=16.

C

0

Q

3

Q

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 2

ПОСЛЕДОВАТЕЛЬНОСТНЫЕ УСТРОЙСТВА

13

Рис. 4.7. 4-х разрядный двоичный асинхронный

счетчик: а – схема, б, в – временные

диаграммы

После каждого импульса кодовая комбинация представляет

собой число поступивших импульсов в двоичной форме. Выходной код

можно подавать в другие устройства для дальнейшей обработки или,

например, преобразовать его с помощью дешифратора в код индикатора

для отображения числа импульсов. Счетчик может использоваться и в

качестве делителя частоты. Например, на выходе частота импульсов в

16 раз меньше частоты входного сигнала.

03

QQ −

3

Q

14

Если после некоторого импульса изменяется несколько разрядов

кода, то переключение соответствующих триггеров в схеме рис. 4.7а

происходит последовательно во времени. Например, по срезу 8-го

импульса с задержкой происходит переключение , по срезу с

задержкой переключается и т.д. (рис. 4.7в). Поэтому счетчики,

собранные по схеме рис. 4.7а, называются асинхронными, или

последовательными. Неодновременное переключение триггеров из-за

покаскадной задержки распространения переноса по цепочке триггеров

приводит к ограничению частоты счета. В многоразрядных счетчиках

последний триггер может не успеть переключиться до прихода

следующего импульса. Поэтому период следования входных импульсов

должен превышать время задержки распространения переноса в счетчике.

Если счетчик используется только для деления частоты, то

неодновременное переключение триггеров не является недостатком. В

этом случае предельная частота входных импульсов будет определяться

только граничной частотой первого триггера.

р

t

0

T

0

Q

р

t

1

T

Для построения вычитающего счетчика, работающего в режиме

обратного счета, нужно использовать закономерности табл. 4.3:

− переменная

0

Q

меняет свое значение после каждого входного

импульса;

− переменная

i

Q

(

1≥i

) меняет свое значение тогда, когда

переменная в соседнем младшем разряде

1−i

Q

переходит из

нулевого состояния в единичное.

Схема рис. 4.7а превратится в вычитающий счетчик, если триггеры

типа M-S, срабатывающие по срезу тактовых импульсов, заменить на

триггеры, переключающиеся по фронту. Для этого достаточно эти входы

подключить к инверсным входам предыдущих триггеров.

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 2

ПОСЛЕДОВАТЕЛЬНОСТНЫЕ УСТРОЙСТВА

15

Таблица 4.3

Таблица состояний 4-разрядного двоичного вычитающего счетчика

3

Q

2

Q

1

Q

0

Q

n

3

2

2

2

1

2

0

2

0 1 1 1 1

1 1 1 1 0

2 1 1 0 1

3 1 1 0 0

4 1 0 1 1

5 1 0 1 0

6 1 0 0 1

7 1 0 0 0

8 0 1 1 1

9 0 1 1 0

10 0 1 0 1

11 0 1 0 0

12 0 0 1 1

13 0 0 1 0

14 0 0 0 1

15 0 0 0 0

16 1 1 1 1

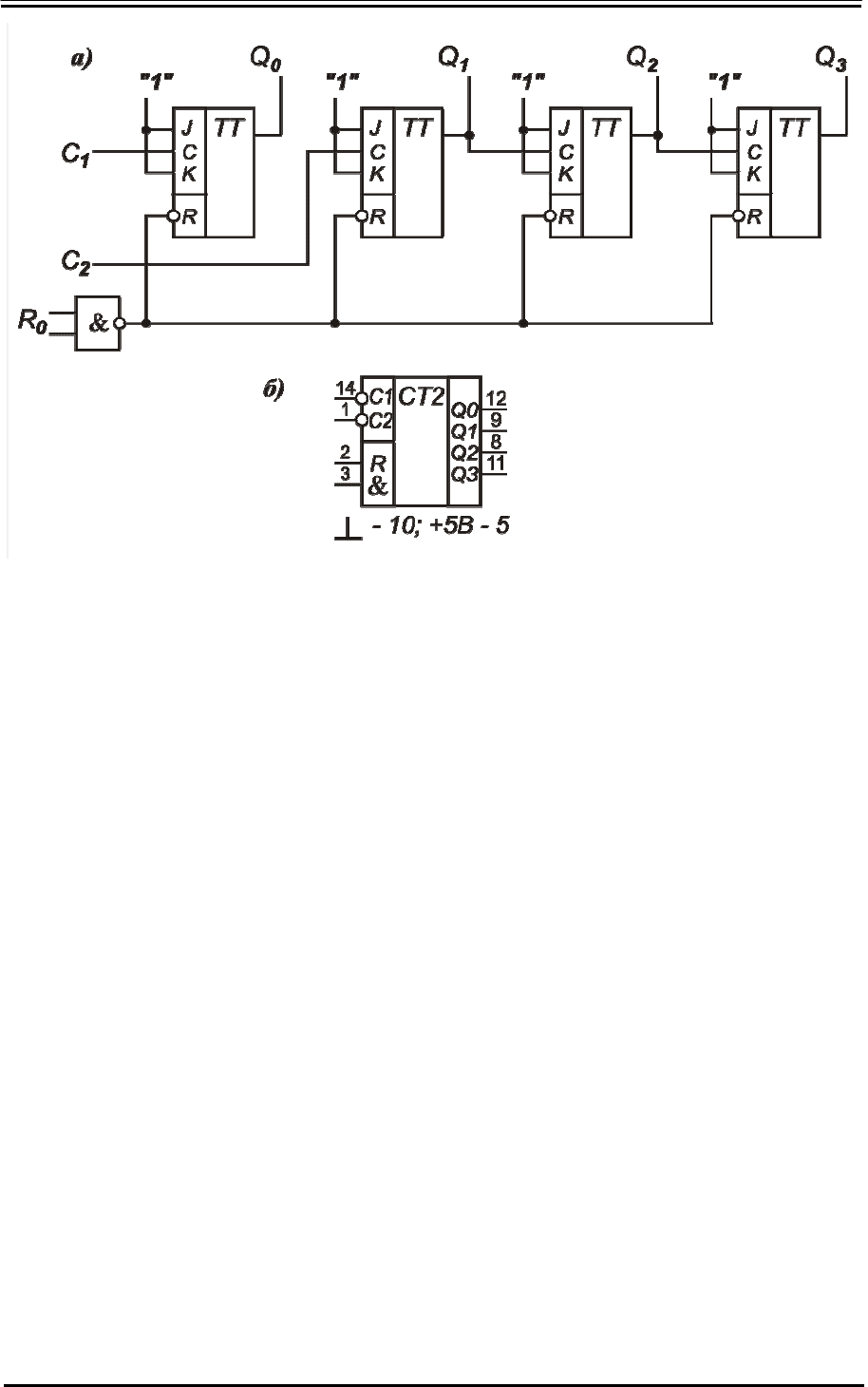

Пример ИС:

К155ИЕ5 – 4–разрядный двоичный асинхронный суммирующий

счетчик (рис.4.8).

ИС содержит 4 JK-триггера типа M-S с логикой 2И на входах

сброса. В режиме счета хотя бы один из входов должен иметь нулевой

уровень, для сброса (установки счетчика в нулевое состояние) на обоих

входах должен быть единичный уровень. Три триггера, включенных

последовательно, образуют 3-разрядный счетчик. Для получения

4-разрядного счетчика необходимо с помощью внешней коммутации

подключить к (или к , тогда будет выходом старшего

разряда, а

C - счетным входом схемы).

0

R

0

Q

2

2

C

3

Q

1

C

0

Q

16

Рис. 4.8. 4-разрядный двоичный асинхронный

суммирующий счетчик К155ИЕ5:

а – схема, б – УГО

4.2.2. Синхронный двоичный счетчик

Триггеры счетчика будут переключаться синхронно, если входные

импульсы поступят одновременно на тактовые входы триггеров всех

разрядов. Для того чтобы выходные переменные соответствовали таблице

состояний, т.е. чтобы все триггеры не переключались одновременно,

необходимо использовать дополнительные схемы формирования переноса

из младших разрядов в старшие. Такой способ объединения триггеров в

единую систему отличает схемы синхронных, или параллельных,

счетчиков. Их можно строить на основе следующих закономерностей

табл. 4.2:

− переменная

0

Q

меняет свое значение после каждого входного

импульса;

− переменная

i

Q

(

1≥i

) меняет свое значение при поступлении

очередного

k

-го импульса в том случае, если после (

1−k

)-го

импульса переменные всех младших разрядов имели единичное

значение.

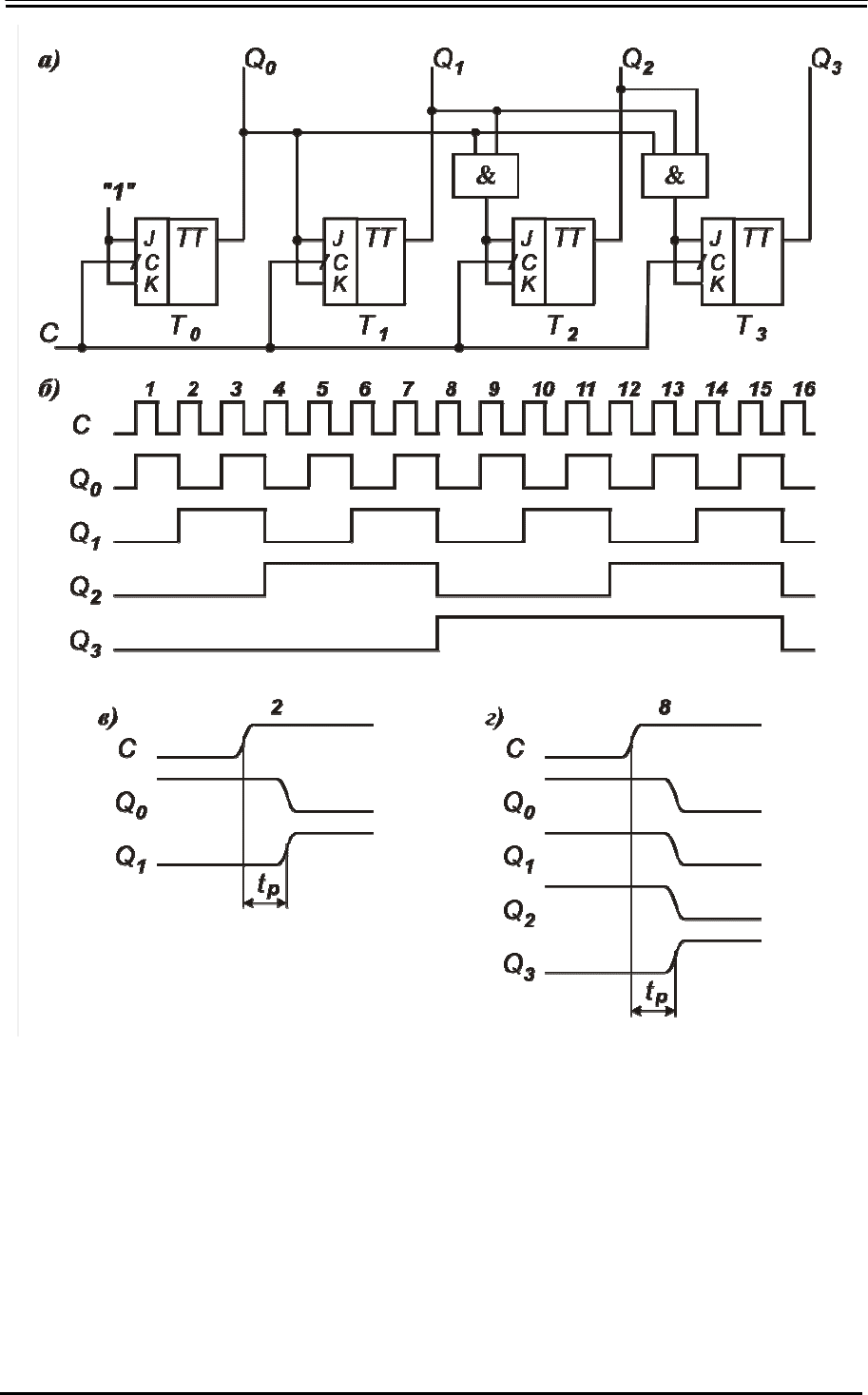

Схема синхронного суммирующего счетчика, составленная с

учетом приведенных закономерностей, приведена на рис. 4.9а.

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 2

ПОСЛЕДОВАТЕЛЬНОСТНЫЕ УСТРОЙСТВА

17

Рис. 4.9. 4-разрядный двоичный синхронный

счетчик: а – схема, б, в, г – временные

диаграммы

Счетчик построен на динамических JK-триггерах, срабатывающих

по фронту тактового сигнала. На информационных входах триггера

уровни , поэтому он меняет свое состояние с каждым импульсом

(рис. 4.9б). Так как время задержки переключения динамического триггера

больше времени удержания (рис.2.20 [1]), то в интервале фронта 1-го

импульса на входах и

0

T

1== KJ

J

K

всех триггеров - нулевой уровень. Поэтому

18

после первого импульса переключается только триггер

.

Разрешение на

переключение триггера дается сигналом (при

0

T

1

T

0

Q

1

0

=

=

=

QJ

C

1

== Q

K

0

Q

0

триггер

меняет свое состояние по фронту тактового импульса , при

триггер находится в режиме хранения). Первый раз триггер

переключается по фронту 2-го импульса (рис.4.9б). При этом происходит

перенос единицы из разряда в разряд . Разрешение на переключение

триггеров и формируется с помощью элементов 2И и 3И

соответственно. Перенос в разряд происходит при , в

при

Q

. Переключение всех триггеров (при переносе единицы

из младшего разряда в старший ) происходит одновременно.

Значения меняются спустя время задержки после фронта тактовых

импульсов (рис.4.9г).

1

T

0

0

=Q

1

T

3

Q

CR

1

T

1

Q

Q

0

Q

CE

1

3

Q

Q

2

T

=

i

3

T

1

2

Q

1

20

== Q

0

Q

р

t

Счетчик, построенный по схеме рис.4.9а, может считать число

импульсов от 0 до 15. Значительное наращивание разрядности в

соответствии с этой схемой невозможно из-за отсутствия многовходовых

элементов И. Поэтому многоразрядные счетчики строят путем соединения

4-х разрядных секций, каждая из которых имеет выход переноса и

вход разрешения переноса (рис.4.10а). Если

=

CE

C

, то триггеры

меняют свое состояние под действием входных импульсов . Когда

значения всех разрядов секции равны 1 и

1

=

CE

(во всех младших секциях

все триггеры находятся в единичном состоянии), формируется сигнал

переноса в старшую секцию счетчика. С помощью выхода переноса

и входа разрешения переноса можно создавать счетчики произвольной

разрядности. Показанный на рис.4.10а счетчик имеет также вход

разрешения счета

1=CR

E

. При

0

=

E

счет запрещен (в счетчике хранится

записанная информация), при

1

=

E

- разрешен. Сигнал на входе

разрешения счета не влияет на формирование переноса .

CR

Временные диаграммы, иллюстрирующие работу счетчика с

выходом переноса , приведены на рис. 4.10б, в. После 15-го импульса

все триггеры переходят в единичное состояние и на выходе появляется

единичный уровень. По фронту 16-го импульса происходит перенос

единицы в младший разряд следующей по старшинству секции (этот

разряд имеет весовой коэффициент 2

4

=16) и одновременно триггеры

возвращаются в нулевое состояние. При этом на выходе переноса

появляется нулевой уровень и по фронту 17-го импульса срабатывает

только младший триггер данной секции.

CR

CR

3

T

0

T

CR

−

0

T

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 2

ПОСЛЕДОВАТЕЛЬНОСТНЫЕ УСТРОЙСТВА

19

Рис 4.10. 4-разрядный двоичный синхронный

счетчик: а – схема, б, в, – временные

диаграммы при Е = СЕ = 1

Пример ИС:

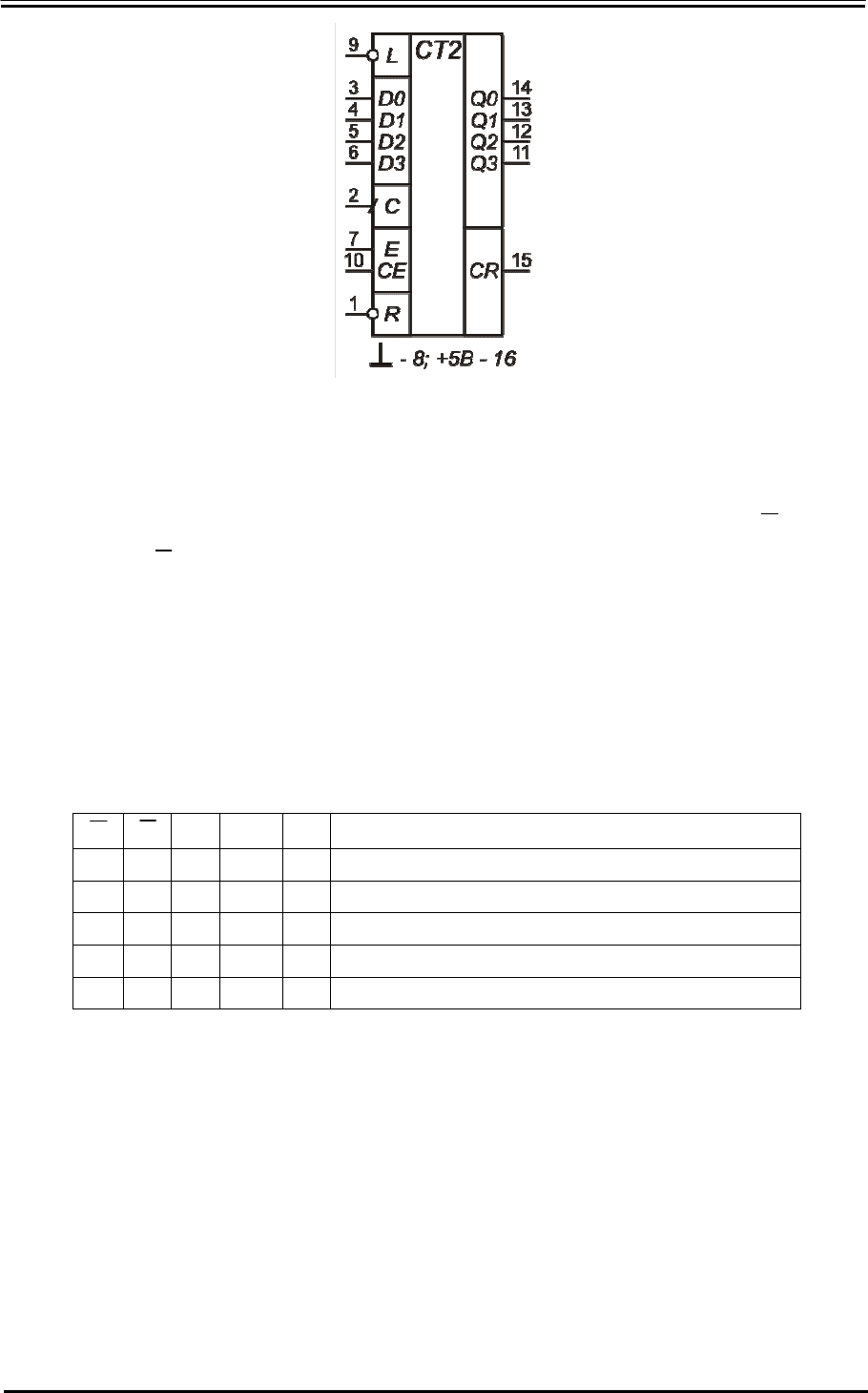

К555ИЕ10 - 4-разрядный двоичный синхронный суммирующий

счетчик (рис. 4.11).

20

Рис. 4.11. 4-разрядный двоичный синхронный

суммирующий счетчик К555ИЕ10

Кроме описанных выше входов и выходов, ИС счетчика имеет вход

асинхронной установки триггеров в нулевое состояние

R

, вход

управления

L

и информационные входы

30

DD

−

параллельного ввода

(предустановки). Значения уровней на входах управления,

соответствующие различным режимам работы счетчика, приведены в табл.

4.4. Режим параллельного ввода данных в счетчик (предустановки) будет

рассмотрен в разделе 4.2.7.

Таблица 4.4

Режимы работы счетчика К555ИЕ10 (К155ИЕ9)

R

L

E

CE

C

Режим

0 х х х х Установка в нуль

1 0 х х

↑

Параллельный ввод

1 1 0 х х Остановка счета

1 1 х 0 х Остановка счета, запрещение переноса

1 1 1 1

↑

Счет

4.2.3. Синхронный двоичный реверсивный счетчик

Синхронный счетчик, работающий в режиме обратного счета,

может быть построен на основе следующих закономерностей табл. 4.3:

− переменная

0

Q

меняет свое значение после каждого входного

импульса;

− переменная

i

Q

(

1≥i

) меняет свое значение при поступлении

очередного

k

-го импульса в том случае, если после (

1−k

)-го

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 2