Егоров В.А. Основы микропроцессорных систем управления

Подождите немного. Документ загружается.

полями

51

содержит: Устройство управления (УУ), арифметико-логическое устройство (АЛУ),

регистр для размещения исполняемой команды (регистр команд), регистр для

размещения одного из операндов или результата операции (аккумулятор) и вентили

Yn, открываемые одноимённым управляющим сигналом уровня логической единицы.

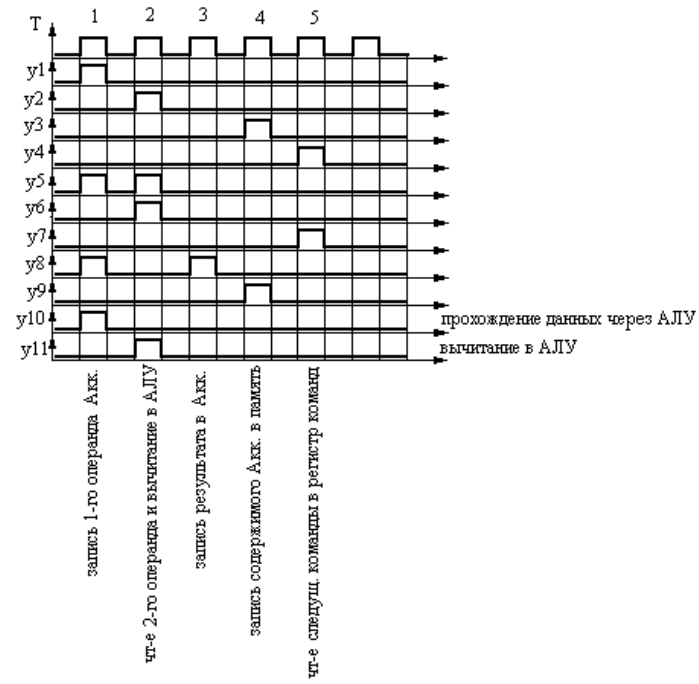

Рассмотрим работу процессора после загрузки в регистр команд команды 1 из

памяти. (Пусть команда 1 – команда вычитания).

Поле кода операции дешифрируется УУ и оно переходит в режим генерации

управляющих сигналов Yn:

Такт 1: сигналы y1,y5,y10,y8 обеспечивают пересылку из памяти

уменьшаемого, проходящего через АЛУ (y10) и запись в аккумулятор;

Такт 2: сигналы y2,y5,y6,y11 обеспечивают пересылку из памяти вычитаемого

и вычитание этого значения (y11) из содержимого аккумулятора;

Такт 3: сигналом y8 разность заносится в аккумулятор;

Такт 4: сигналы y3 и y9 обеспечивают пересылку разности из аккумулятора в

ячейку памяти, на которую указывает четвёртое поле команды;

Такт 5: сигналы y4 и y7 обеспечивают чтение в регистр команд следующей

команды программы.

Рис. 45. Временная диаграмма работы УУ для команды вычитания

Существенным недостатком рассмотренного процессора является непомерно

большая разрядность шины данных, обусловленная необходимостью хранения всех

полей команды в одной ячейке памяти. Так, например, при ёмкости памяти в 64К

52

каждое адресное поле будет содержать 16 двоичных разрядов, и для хранения только

адресной части команды необходима 64-х разрядная ячейка памяти, а для передачи в

процессор – 64-х разрядная шина данных. В связи с этим в современных

микропроцессорах число адресных полей уменьшено до одного за счёт усложнения

структуры и алгоритмов функционирования процессора.

Соображения для исключения трёх последних адресных полей команды:

1) Если размещать команды программы в памяти друг за другом, то адрес

следующей команды будет отличаться от адреса текущей команды на единицу.

Добавив в процессор счётчик команд, можно хранить в нём адрес текущей команды и

наращивать его содержимое на единицу перед чтением следующей команды. Это

позволит исключить из команды поле адреса следующей команды.

2) Содержимое регистра аккумулятора можно по умолчанию использовать, как

второй операнд, и результат операции оставлять в аккумуляторе. Это позволит

исключить из команды поле адреса второго операнда и поле адреса результата

соответственно.

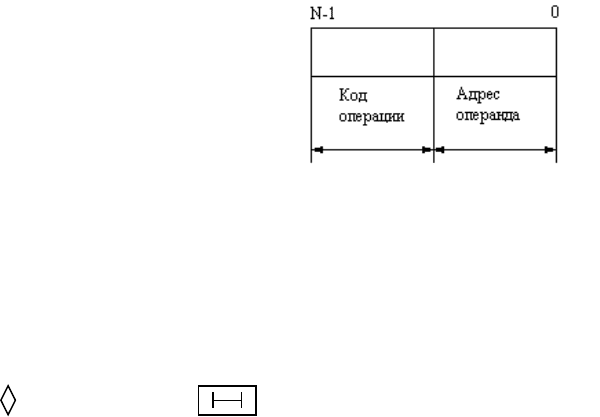

5.2. Процессор, работающий с одноадресными командами

Формат команды процессора имеет вид:

Рис. 46. Формат команды процессора с одноадресными командами

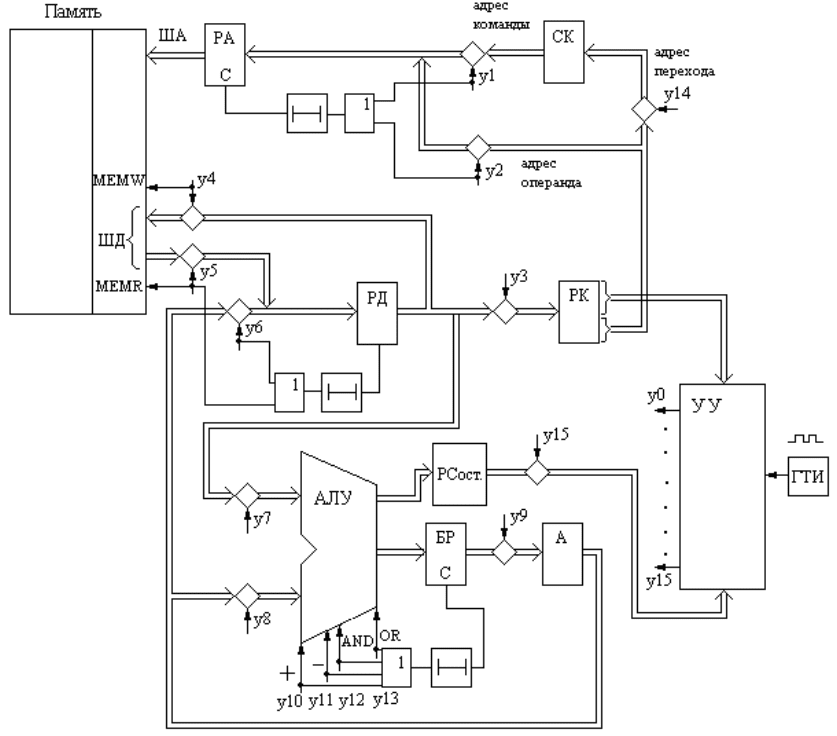

Структурная схема процессора изображена на рис. 47. Процессор содержит

следующие элементы: РА – регистр адреса; СК – счетчик команд; РД – регистр

данных; РК – регистр команд; АЛУ - арифметико-логическое устройство; РСост –

регистр состояния (флагов); БР – буферный регистр; A – регистр аккумулятор; УУ -

устройство управления; ГТИ – генератор тактовых импульсов; Yn – управляющие

сигналы; -коммутатор; - элемент задержки.

5.2.1. Описание работы

1) Загрузка кода операции и операнда. Подготовка регистров к выполнению

команды

В исходном состоянии счётчик команд СК, предназначенный для хранения

адреса команды, обнулён, т.е. выполнение программы начинается с команды,

расположенной в нулевой ячейке. Наращивание СК на единицу производится

сигналом у0, формируемым после выполнения очередной инструкции. Адрес из

счётчика команд запоминается для хранения в регистре адреса РА сигналом у1 и

поступает на шину адреса ША. В соответствии с выставленным на шине адреса

кодом, происходит выборка из памяти команды, предназначенной для выполнения. Эта

команда последовательно переносится в регистр данных РД и регистр команд РК по

управляющим сигналам у5 и у3 соответственно. Адресная часть, необходимая для

53

выборки из памяти операнда, помещается в регистр адреса РА сигналом у2. Выбор

операнда из памяти в регистр данных происходит сигналом у5.

Рис. 47. Структура процессора, работающего с одноадресными командами

Код операции поступает в устройство управления, где происходит его дешифрация.

На этом подготовительная часть, включающая в себя загрузку из памяти

инструкции, предназначенной для выполнения, и операнда считается завершенной.

Дальнейшая работа процессора происходит в соответствии с загруженной командой.

Рассмотрим её на примере операции сложения содержимого аккумулятора с памятью.

2) Выполнение команды

После завершения подготовительной части в регистре данных уже находится

операнд, с которым происходит сложение содержимого аккумулятора. Сигналом у7

второй операнд передаётся в АЛУ. Содержимое аккумулятора поступает на нижний

вход АЛУ по сигналу у8. Далее по сигналу у10 производится сложение. Результат

автоматически передаётся в буферный регистр БР, предназначенный для хранения

промежуточных результатов вычислений. По сигналу у9 содержимое этого регистра

копируется в аккумулятор.

54

5.2.2. Примеры реализации некоторых команд

1) Команда пересылки содержимого аккумулятора в ячейку памяти (MOV

M ,A)

Схема команды: (А→М)

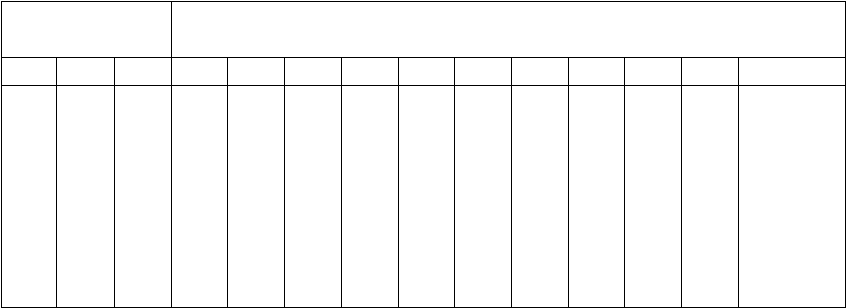

Таблица 17

Такт Управляющие

сигналы

Действия

1 y1 СК →РК

2 y0 СК+1→СК

3 y5 (MEM[PA]) →РД

4 y3 РД→РК

5 y2 Адр. частьРК→РА

6 y6 А→РД

7 y4 РД→( MEM[PA])

2) Команды сложения (вычитания) содержимого аккумулятора с операндом

в ячейке памяти, адресуемой в команде (ADD M (SUB M))

Схема команды: (А+М→А (А-М→А))

Таблица 18

Такт Управляющие

сигналы

Действия

1 y1 СК →РК

2 y0 СК+1→СК

3 y5 (MEM[PA]) →РД

4 y3 РД→РК

5 y2 Адр. частьРК→РА

6 y5 (MEM[PA]) → РД

7 y10(y11),y7,y8 А+РД→ БР (А-РД→ БР)

8 y9 БР→А

3) Команды логического умножения (логического сложения) содержимого

аккумулятора с операндом в памяти AND M; OR M;

Схема команды: (А and М→А (А or М→А))

Таблица 19

Такт Управляющие

сигналы

Действия

1 y1 СК →РК

2 y0 СК+1→СК

3 y5 (MEM[PA]) →РД

4 y3 РД→РК

5 y2 Адр. частьРК→РА

6 y5 (MEM[PA]) → РД

7 y12(y13),y7,y8 А and РД→ БР (А or РД→ БР)

8 y9 БР→А

55

4) Команда пересылки содержимого ячейки памяти в аккумулятор (MOV A,M)

Схема команды: (М→А)

Таблица 20

Такт Управляющие

сигналы

Действия

1 y1 СК →РК

2 y0 СК+1→СК

3 y5 (MEM[PA]) →РД

4 y3 РД→РК

5 y2 Адр. частьРК→РА

6 y5 (MEM[PA]) →РД

7 y10,y7 РД→БР

8 y9 БР→A

5) Команда безусловного перехода на метку Addr (JMP Addr)

Таблица 21

Такт Управляющие

сигналы

Действия

1 y1 СК →РК

2 y0 СК+1→СК

3 y5 (MEM[PA]) →РД

4 y3 РД→РК

5 y14 Адр. частьРК→СК

5.3. Реализация устройства управления

(управляющий автомат с жёсткой логикой)

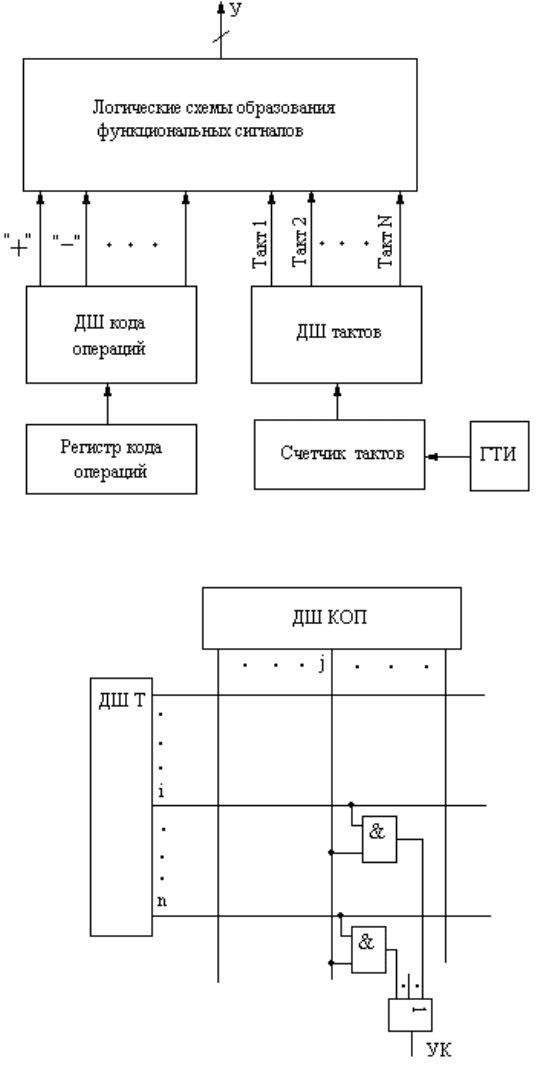

В состав схемы (рис. 48) входят регистр кода операции, являющийся частью регистра

команд, счётчик тактов, дешифратор тактов и дешифратор кода операции, а также

логические схемы образования управляющих функциональных сигналов (логическая

матрица).

На счётчик тактов поступают импульсы от ГТИ, и счётчик с каждым импульсом

увеличивает своё содержимое на 1. Состояния счётчика представляют собой номера

тактов, изменяющиеся от 1 до n. Дешифратор формирует на i-м выходе единичный

сигнал при i-м состоянии счётчика тактов, т.е. во время i-го такта.

Дешифратор кода операции вырабатывает единичный сигнал на j-м выходе, если

исполняется j-я команда.

Принцип построения логических схем образования управляющих

функциональных сигналов поясняет рис. 49.

56

Рис. 48. Структурная схема автомата

Рис. 49. Формирование сигнала Yk в i-м и n-м тактах выполнения j-й команды

Здесь показан фрагмент схемы, обеспечивающий выработку управляющего

сигнала Yk в i-м и n-м тактах выполнения j-й команды.

Недостатком рассмотренной схемы является одинаковое число тактов для каждой

команды. Это требует выравнивания числа тактов исполнения команд по наиболее

длинной команде, что ведёт к непроизводительным затратам времени. Чтобы устранить

этот недостаток, схемы строят с использованием нескольких счётчиков тактов.

57

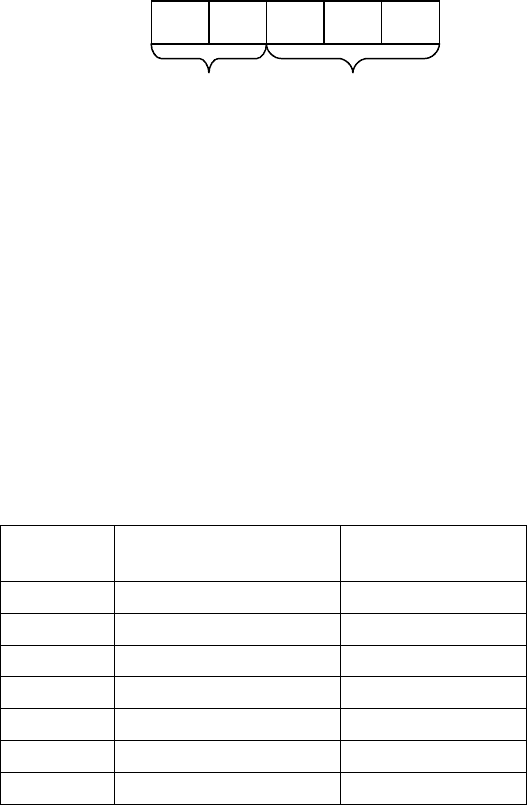

5.4. Пример реализации устройства управления

(для процессора с одноадресными командами)

Пусть требуется реализовать пятиразрядный процессор с одноадресными

командами по схеме рис. 47, имеющий формат команды:

Рис. 50. Формат команды пятиразрядного процессора

Процессор должен выполнять следующую последовательность действий:

1) переслать первый операнд из памяти в аккумулятор;

2) сложить содержимое аккумулятора со вторым операндом, выбираемым из памяти;

3) поместить результат из аккумулятора в память.

Для реализации указанных действий воспользуемся командами MOV A,M; ADD

M; MOV M,A, описанными выше. Закодируем команды цифрами 2, 1 и 0

соответственно. Учитывая, что процессор стартует с нулевого адреса, изобразим

заполнение памяти:

Таблица 22

Адрес

ячейки

Содержимое

ячейки

Кодировка

содержимого

0 MOV A,M 10 100

1 ADD M 01 101

2 MOV M,A 00 110

3 не используется

4 1-ый операнд (8) 01000

5 2-ой операнд (9) 01001

6 результат (17) 10001

Первые три ячейки занимают команды: первая из них – помещает содержимое

ячейки с адресом 4 (100(В)) в аккумулятор; вторая – прибавляет к содержимому

аккумулятора содержимое ячейки с адресом 5 (101(В)); третья – сохраняет результат в

ячейку ОЗУ с адресом 6 (110(В)).

Определим длительность команд в тактах (8, 8, 7). Следовательно, дешифратор

тактов имеет 3-входа, 8-выходов, а счетчик тактов – трехразрядный.

Так как под кодировку команды отведено два разряда - дешифратор кода команды

имеет 2-входа, 4-выхода.

Таким образом, матрица, формирующая сигналы управления Yn, имеет 8 строк и

4 столбца.

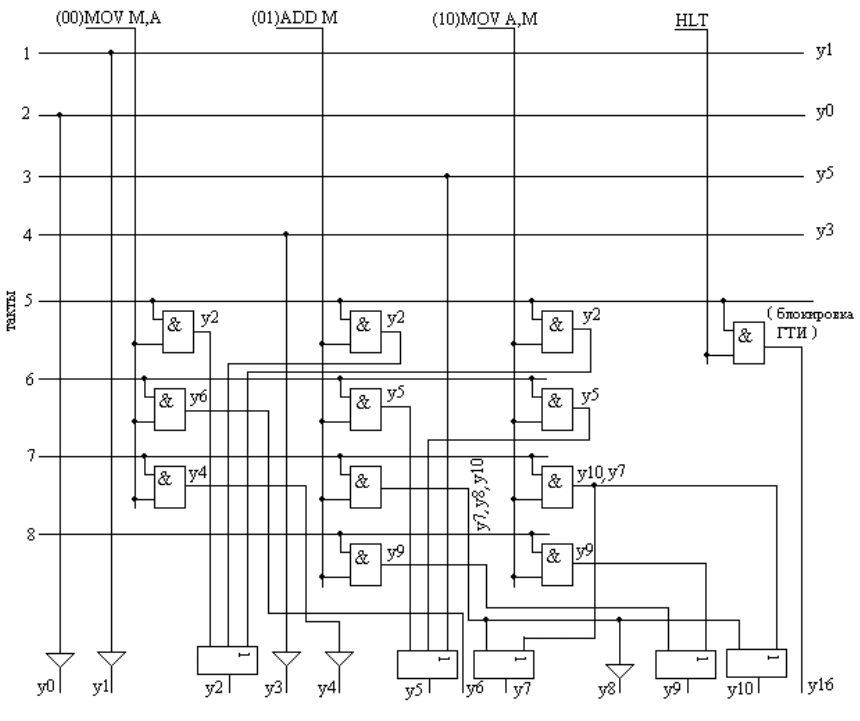

Матрицу удобно заполнять по столбцам, имея перед собой последовательность

формирования управляющих сигналов по тактам, для конкретной команды. На

пересечении столбца, соответствующего реализуемой команде, со строками,

Слово1 D4 D3 D2 D1 D0

Код Адрес операнда

операции в памяти

58

соответствующими тактам, включаются элементы “2-И”, на выходе которых

подписывают управляющие сигналы, соответствующие данному такту. Когда все

столбцы сформированы, объединяют одноименные управляющие сигналы из всех

точек на элементе “ИЛИ”.

Руководствуясь данным принципом, на рис. 51 составлена схема логической

матрицы устройства управления пятиразрядного процессора с одноадресными

командами.

Рис. 51. Схема матрицы, формирующей сигналы управления

Приведенная схема упрощена, так как первые четыре такта всех реализуемых

команд формируют одинаковые управляющие сигналы.

5.5. Вопросы для повторения

1. Перечислите регистры микропроцессора. Поясните их назначение.

2. В чем особенность регистра аккумулятора?

3. Каково назначение коммутатора?

4. Каково назначение устройства управления?

5. Поясните принцип работы управляющего автомата с жесткой логикой.

59

6. КОНТРОЛЬНАЯ РАБОТА

Цель работы - ознакомление с основными методами представления информации в

микропроцессорных системах управления, освоение правил перевода чистовых данных

из одной системы счисления в другую, изучение методов повышения надежности

передачи информации по линиям связи, изучение методики записи и преобразования

логических выражений, анализ таблиц истинности и составление логических схем.

6.1. Задания к контрольной работе

Контрольная работа включает четыре задания.

Задание 1

Два числа, одно из которых - номер Вашей зачётной книжки, а другое

представляет собой сумму числа 40 и числа из двух последних цифр номера зачётной

книжки, перевести в двоичную, восьмеричную и шестнадцатеричную системы

счисления. Сложить эти числа в двоичной системе счисления и результат перевести в

десятичную систему счисления, а затем записать в двоично-десятичном коде.

Задание 2

Пользуясь таблицей кодов КОИ-7 (см. табл. 1) записать свою фамилию и имя,

разделенные пробелом, в виде последовательности двоичных и шестнадцатеричных

кодов. Дополнить полученную последовательность кодов восьмым контрольным

разрядом для контроля на четность и записать новые последовательности кодов по-

вышенной надежности.

Задание 3

Записать логическое выражение для функции F(X,Y,Z) согласно заданной таблице

истинности (табл. 23). Полученное логическое выражение упростить и составить по

нему логическую схему. Вариант значений логической функции при различных

значениях аргументов X,Y и Z определяется по последней цифре номера Вашей

зачетной книжки.

Таблица 23

Значения

аргументов

Значения функции для различных вариантов

X Y Z 0 1 2 3 4 5 6 7 8 9 Пример

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1

0

1

0

0

0

1

0

0

1

0

0

1

0

0

1

0

1

0

1

0

0

1

0

0

0

1

0

1

1

0

0

1

0

0

1

1

0

0

0

0

0

1

0

0

0

1

1

0

1

0

1

0

1

0

0

0

0

0

0

1

1

0

1

1

1

0

0

0

0

1

0

1

0

1

0

0

1

0

0

1

1

0

0

0

1

0

1

60