Егоров В.А. Основы микропроцессорных систем управления

Подождите немного. Документ загружается.

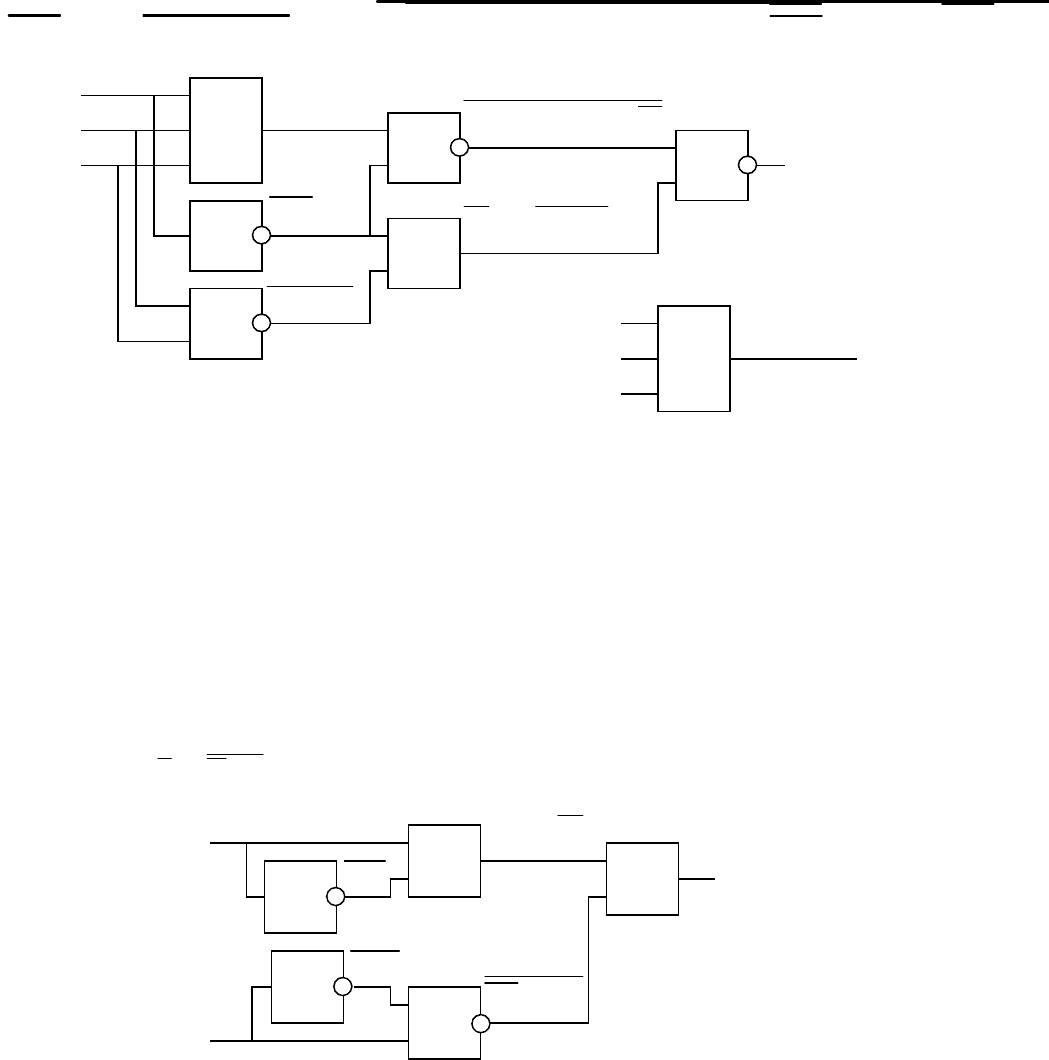

3.7. Составление логических выражений по бесконтактным схемам

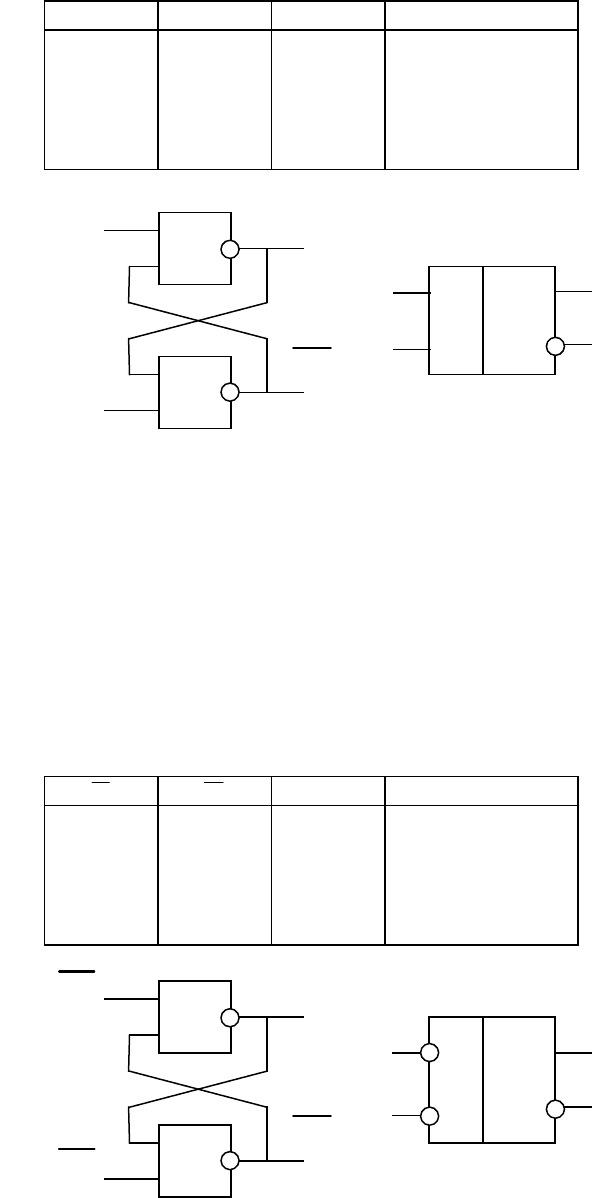

Логическое выражение может быть составлено по схеме на бесконтактных

логических элементах. Для этого, двигаясь от входов к выходу, проводят анализ

преобразования сигналов на отдельных логических элементах. Пример такого анализа

приведен на рис. 8.

Полученная на выходе логическая функция может быть в дальнейшем упрощена

согласно законам алгебры логики.

.Z*Y*XZ*Z*Y*XY*Z*Y*X)ZY(*Z*Y*X)ZY(

*)X*XX*Z*Y*X()ZY(*X*)X)Z*Y*X(()ZY(*X

*)X)Z*Y*X(())ZY(X()X)Z*Y*X(()Z,Y,X(F

Рис. 8. Пример анализа схемы на логических элементах

Таким образом, исходная схема (рис. 8, а) является избыточной и её логическая

функция может быть реализована одним логическим элементом (рис. 8, б). Алгебра логики

является эффективным средством анализа и минимизации схем дискретной автоматики.

3.8. Построение схем по логическому выражению

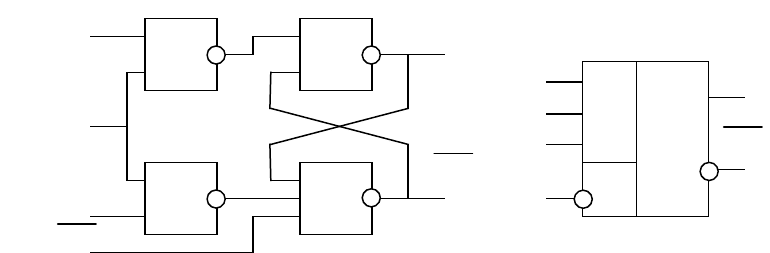

Построение схем по логическому выражению (синтез схем) начинают также с

входов, при этом их количество равно количеству аргументов (каждый вход - это

отдельный независимый сигнал-аргумент). Затем последовательно ставят логические

элементы, которые будут преобразовывать поступающие сигналы согласно приоритету

логических операций в исходном логическом выражении. Например, для выражения

)(*)(),( YXYXYXF

схема будет иметь вид, представленный на рис. 9.

Рис. 9. Пример синтеза схемы на логических элементах

Первый элемент

нулевой ячейки

Ячейка с адресом 2

б)

а)

F

X)Z*Y*X(

)ZY(X

ZY

X

X*Y*Z

X

&

1

1

Y

Z

1

1

1

F=X*Y*Z

X

&

Y

Z

Y

Y

F

YX

YX

X

X

1

1

1

&

1

21

3.9. Составление таблицы истинности по логическому выражению

Составление таблицы истинности по логическому выражению заключается в

подстановке значений аргументов для данной строки таблицы в логическое выражение

и его вычислении. Например, для выражения

)YX(*)YX()Y,X(F

в строке, где

Х = 0 и Y = 1, получаем

.00*01*0)11(*)00()10(*)10()1,0(F

Полученный результат записывается в столбец значений функции. Такие

вычисления выполняют для каждой строки (напоминаем, что при n - аргументах

таблица истинности будет иметь 2

n

строк).

3.10. Вопросы для повторения

1. Дайте определения понятию логические переменные. Приведите технические и

другие примеры явлений, которые описываются логическими переменными.

2. Назовите три основные логические операции. Каков приоритет этих операций в

сложных логических выражениях?

3. Каково назначение таблицы истинности и сколько в ней строк?

4. ТИПОВЫЕ УЗЛЫ ЦИФРОВОЙ МИКРОСХЕМОТЕХНИКИ

4.1. Комбинационные схемы

4.1.1. Понятие о комбинационной схеме

Комбинационная схема – это устройство цифровых систем, у которых

совокупность выходных сигналов в дискретный момент времени определяется

входными сигналами, поступившими на входы в тот же дискретный момент времени.

Реализуемый в этих схемах способ обработки информации называется

комбинационным, так как результат обработки зависит только от комбинации входных

сигналов и вырабатывается сразу при подаче входной информации.

Закон функционирования комбинационной схемы определен, если задано

соответствие между входом и выходом, например в виде таблицы или в аналитической

форме в виде логического выражения.

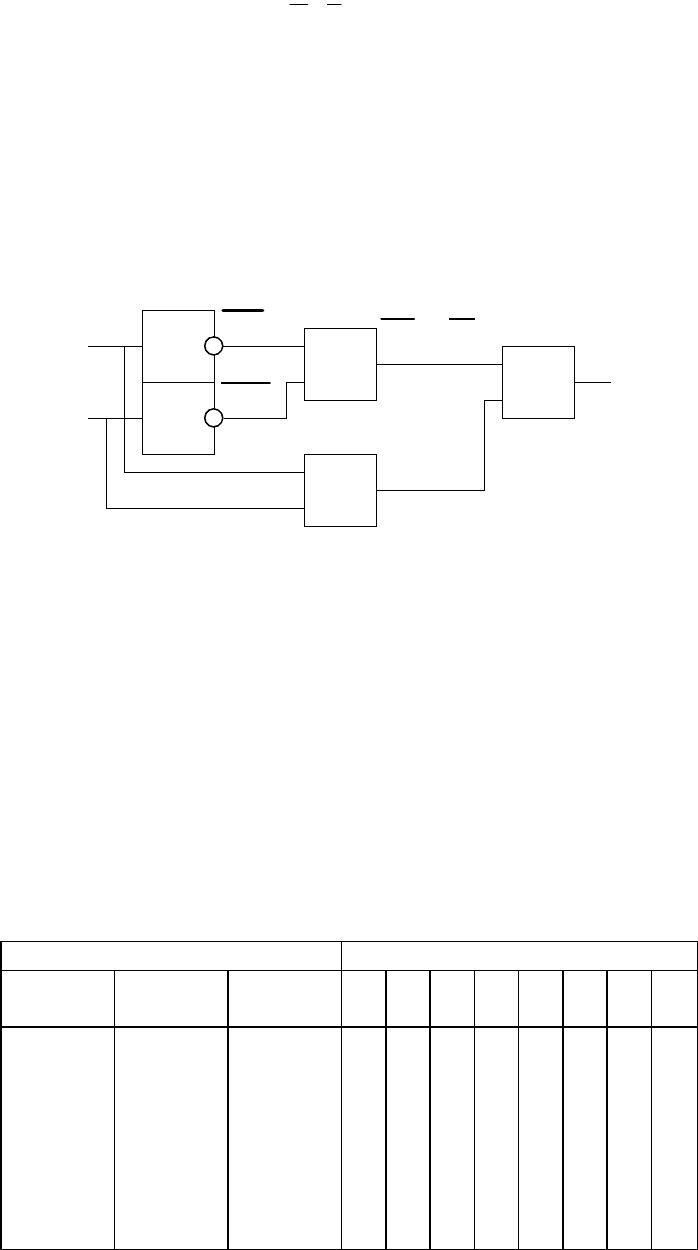

4.1.2. Схема совпадения кодов

В качестве примера комбинационной схемы рассмотрим схему совпадения двух

двоичных сигналов, которая реализует логическую функцию двух переменных,

называемую «эквивалентность». Эта функция равна 1, если входные сигналы

совпадают, и равна 0, если не совпадают. Таблица истинности этой функции F

отражает зависимость её от значений входных переменных X и Y (табл. 7).

Таблица 7

X Y F(X,Y)

0

0

1

1

0

1

0

1

1

0

0

1

Первый элемент

нулевой ячейки

Ячейка с адресом 2

22

Запишем логическое выражение. Для этого по табл. 8 составим логическую

сумму, где слагаемыми являются логические произведения аргументов, взятых из

строк, где функция равна 1. При этом если в этой строке аргумент равен 0, то он

берется с инверсией. В данном случае F равна 1 в первой и последней строке, причем в

первой строке оба аргумента равны нулю. Поэтому логическое выражение имеет вид:

.Y*XY*XF

Для аппаратной реализации логических выражений используем бесконтактные

логические элементы, при этом учитываем правило приоритета: сначала выполняются

действия в скобках (в данном случае их нет), затем операции логического отрицания

(инверсии), далее выполняется логическое умножение и последним логическое

сложение. Такая последовательность операций для нашего выражения дает схему (рис.

10).

Такие схемы используются для контроля точного совпадения двоичных кодов,

при этом количество таких схем равно разрядности кодов, а выходы схем

объединяются на элементе И.

Рис.10. Схема совпадения (эквивалентность)

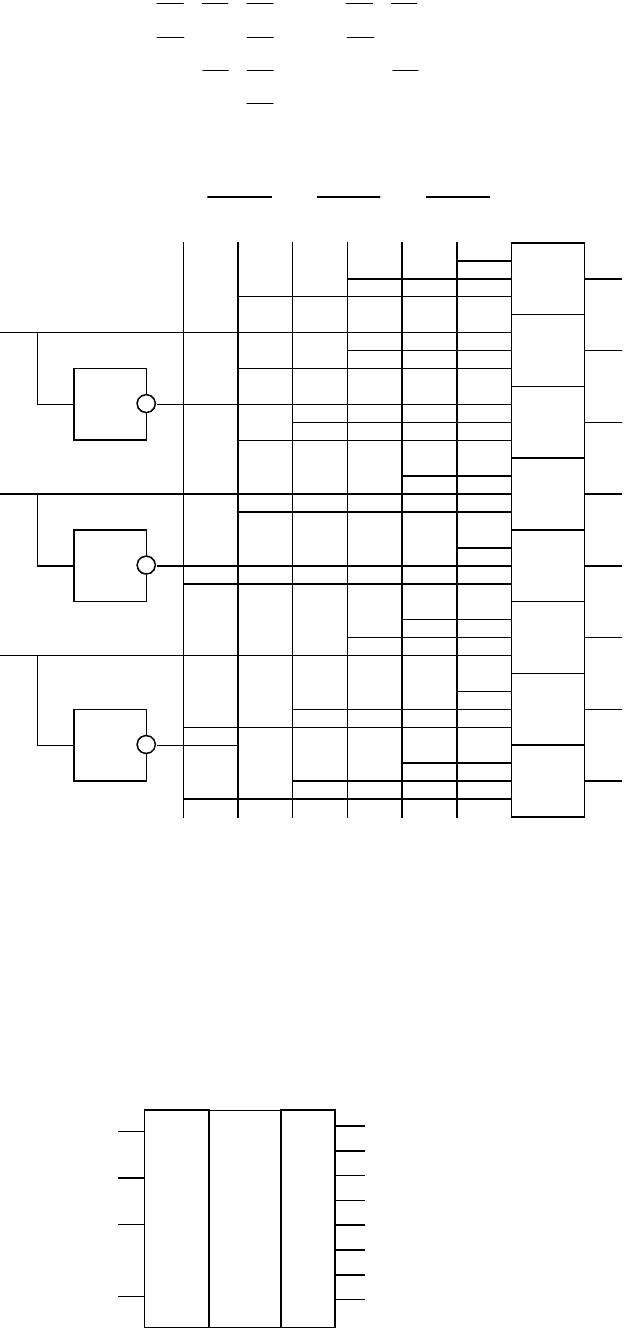

4.1.3. Дешифратор

Дешифратор - это комбинационная схема, имеющая n входов и m выходов и

преобразующая комбинацию входных сигналов (код) в выходной сигнал на отдельном

выходе, номер которого является десятичным эквивалентом двоичного кода на входе.

То есть каждому предусмотренному набору входных сигналов соответствует один

вполне определенный возбужденный выход. Дешифратор называется полным, если он

имеет столько выходов m, сколько различных комбинаций может иметь n – разрядное

двоичное число на его входах, то есть m = 2

n

.

Если дешифратор имеет три входа, то максимально он будет иметь восемь

выходов. Все состояния такого дешифратора приведены в табл. 8.

Таблица 8

Входы Выходы

X

2

X

1

X

0

P

0

P

1

P

2

P

3

P

4

P

5

P

6

P

7

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1 1

1

1

1

1

1

1

F

Y

X

1

Y

Y*X

Y*X

X

1

&

&

1

Первый элемент

нулевой ячейки

Ячейка с адресом 2

23

Аналитически его работа описывается логическими выражениями:

.X*X*XP;X*X*XP

;X*X*XP;X*X*XP

;X*X*XP;X*X*XP

;X*X*XP;X*X*XP

01270126

01250124

01230122

01210120

Согласно этим выражениям схема дешифратора на три входа имеет вид,

изображённый на рис. 11.

Рис.11. Схема полного дешифратора на три входа

Дешифратор широко применяется в цифровых устройствах в системах

преобразования сигналов и выбора элементов, поэтому он выпускается в виде

отдельной микросхемы. Следует также отметить, что дешифратор может имнеть

дополнительные вспомогательные входы (например вход синхронизации или выбора

микросхемы), которые расширяют возможности его использования. Дешифраторы

имеют условное обозначение (рис.12). Здесь дешифратор имеет дополнительный вход

выбора микросхемы “CS”. При наличии на входе “CS” логического нуля, все выходы

будут иметь состояние логического нуля, независимо от входной комбинации.

0

1

2

3

4

5

6

7

2

2

2

1

2

0

СS

X

2

X

1

X

0

DC

P

0

P

1

P

2

P

3

P

4

P

5

P

6

P

7

2

X

1

X

0

X

1

X

0

X

0

X

2

X

1

X

2

X

P

0

&

1

P

1

&

P

2

&

P

3

&

P

4

&

P

5

&

P

6

&

P

7

&

1

1

Первый элемент

нулевой ячейки

Ячейка с адресом 2

24

Рис.12. Условное графическое обозначение дешифратора на три входа (3:8)

Первый элемент

нулевой ячейки

Ячейка с адресом 2

25

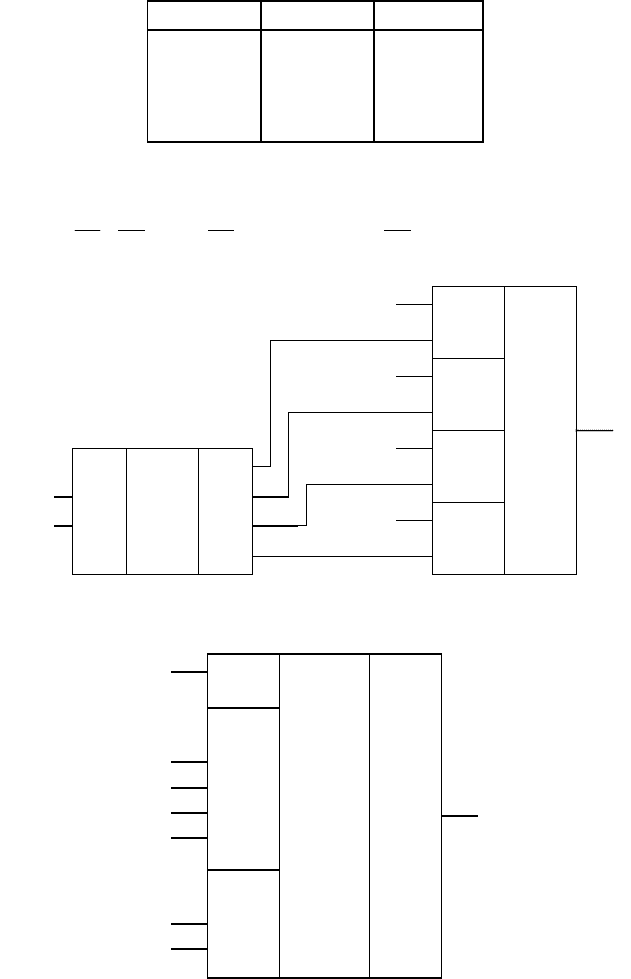

4.1.4. Мультиплексор

Мультиплексор - это комбинационная схема, обеспечивающая выбор и

подключение сигнала с одной из нескольких входных линий на выходную. Как

правило, мультиплексор (его еще называют селектором) имеет n управляющих и m=2

n

информационных входов и один выход. На управляющие входы подается число в

двоичном коде, которое указывает, какой из информационных входов подключить к

выходу (какой из входных информационных сигналов передать на выход).

Например, мультиплексор с двумя управляющими входами (n = 2) может иметь

четыре информационных входа (m= 2

n

), и его работа описывается табл. 9, где X

1

, X

0

-

управляющие входы, D

3

,D

2

,D

1

,D

0

- информационные входы, Y - выход.

Таблица 9

X

1

X

0

Y

0

0

1

1

0

1

0

1

D

0

D

1

D

2

D

3

В соответствии с табл. 9 логическое выражение, описывающее работу

мультиплексора на четыре информационных входа, имеет вид:

.D*X*XD*X*XD*X*XD*X*XY

301201101001

Рис. 13. Схема мультиплексора на четыре информационных входа

X

1

X

0

D

3

D

2

D

1

D

0

Y

1&

&

&

&

DC 0

1

2

3

2

1

2

0

D

0

D

1

D

2

D

3

Y

X

0

X

1

MS

DI

0

1

2

3

E

A

0

1

DO

Первый элемент

нулевой ячейки

Ячейка с адресом 2

26

Рис. 14. Условное графическое обозначение мультиплексора

Согласно этому выражению схема мультиплексора может быть реализована

следующий образом (рис. 13).

Дешифратор, как и мультиплексор, может иметь дополнительные управляющие

входы, например вход синхронизации E. Условное графическое обозначение

мультиплексора изображено на рис. 14.

4.1.5. Вопросы для повторения

1. Какое устройство называется комбинационной схемой?

2. Как задается закон функционирования комбинационной схемы?

3. Как составить логическое выражение по таблице?

4. Что учитывается при составлении схем по логическому выражению?

5. Какая схема называется дешифратором?

6. Какой дешифратор называется полным?

7. Какая схема называется мультиплексором?

8. Каково назначение управляющих и информационных входов?

9. Как обозначаются на схемах дешифраторы и мультиплексоры, если они

выполнены отдельной микросхемой?

4.2. Триггеры

4.2.1. Общие сведения о триггерах

Триггер – это простой цифровой автомат с памятью, то есть схема, состояние

входов которой зависит не только от состояния входов в данный момент времени, но и

от состояния самого устройства в предыдущие моменты времени.

Триггер является элементом, который может находиться в одном из двух

устойчивых состояний. Одному из этих состояний приписывается значение 1, а

другому 0.

Состояние триггера распознается по его выходу.

Под влиянием входного сигнала триггер скачкообразно переходит из одного

устойчивого состояния в другое. При этом скачкообразно изменяется уровень

напряжения его выходного сигнала.

Для удобства использования в схемах вычислительных устройств триггеры

обычно имеют два выхода – прямой Q и инверсный

Q

. В единичном состоянии

триггера на выходе Q высокий уровень сигнала (логическая единица), а в нулевом

состоянии - низкий (логический нуль), на выходе

Q

– наоборот. Существует несколько

различных типов триггеров. Рассмотрим некоторые из них.

4.2.2. Асинхронный RS – триггер

Триггеры этого типа имеют два входа, обозначаемые буквами S (от английского

set - установить) и R (от reset - сбросить) и используемые соответственно для

установки триггера в единицу и ноль. Работа такого триггера описана в табл. 10.

Схема RS – триггера может быть получена из двух логических элементов ИЛИ-

НЕ (см. рис. 15, а), соединенных таким образом, что возникают положительные

обратные связи, благодаря которым в устойчивом состоянии выходной транзистор у

одной схемы ИЛИ-НЕ закрыт, а у другой - открыт. При отсутствии сигналов на входах

Первый элемент

нулевой ячейки

Ячейка с адресом 2

27

(R=0, S=0) это состояние сохраняется сколько угодно долго, пока есть питание на

схеме.

Таблица 10

S R Q Режим

0

0

1

1

0

1

0

1

х

0

1

-

Хранение

Запись 0

Запись 1

Комбинация

запрещена

Рис.15. Схема (а) и условное графическое обозначение (б) асинхронного RS – триггера

на элементах ИЛИ-НЕ

При подаче сигнала на один из входов происходит подтверждение установки

триггера или его переключение. При R=1, S=1 (запрещенный режим) оба выхода

триггера устанавливаются в нулевое состояние и нельзя с определенностью сказать, в

каком состоянии будет триггер после одновременного снятия входных сигналов. На

рис. 15, б приведено условное обозначение асинхронного RS - триггера.

Часто триггеры этого типа реализуются на элементах И-НЕ (см. рис. 16, а); для

них таблица переходов (табл. 11) и условное обозначение (рис. 16, б) будут иными.

Таблица 11

S

R

Q Режим

0

0

1

1

0

1

0

1

-

1

0

х

Комбинация

запрещена

Запись 1

Запись 0

Хранение

Рис.16. Схема (а) и условное графическое обозначение (б) асинхронного RS – триггера

на элементах И-НЕ

Q

Q

&

&

S

R

Q

Q

T

а) б)

б)а)

R

S

Q

Q

S

R

T

R

Q

Q

1

S

1

Первый элемент

нулевой ячейки

Ячейка с адресом 2

28

В отличие от предыдущего случая здесь управление триггером осуществляется

подачей на один из входов логического нуля.

4.2.3. Синхронный RS – триггер

Для повышения надежности и более четкой работы цифровые устройства

переключаются в фиксированные моменты времени, задаваемые тактовыми

импульсами или импульсами синхронизации. Введение синхронизации для RS –

триггера осуществляется установкой на входе двух элементов И-НЕ (рис. 17, а).

Рис.17. Схема (а) и условное графическое обозначение (б) синхронного RS – триггера

В этой схеме вход C является входом синхронизации. При состоянии входа C = 0

оба входных элемента И-НЕ на своих выходах имеют единичное состояние и,

следовательно, RS – триггер (вторая часть схемы) находится в состоянии хранения

информации. Установка триггера в состояние 0 или 1 возможна только при подаче на

вход C тактового импульса (C = 1). Действительно, допустим, что на вход подано S =

0, R = 1, и с приходом тактового импульса верхний элемент будет иметь на выходе 1, а

нижний – 0, что приведет к переводу триггера в нулевое состояние. По окончании

тактового импульса триггер опять закроется и перейдет в режим хранения. При наличии

импульсов синхронизации таблица переходов синхронного RS – триггера

соответствует табл. 10.

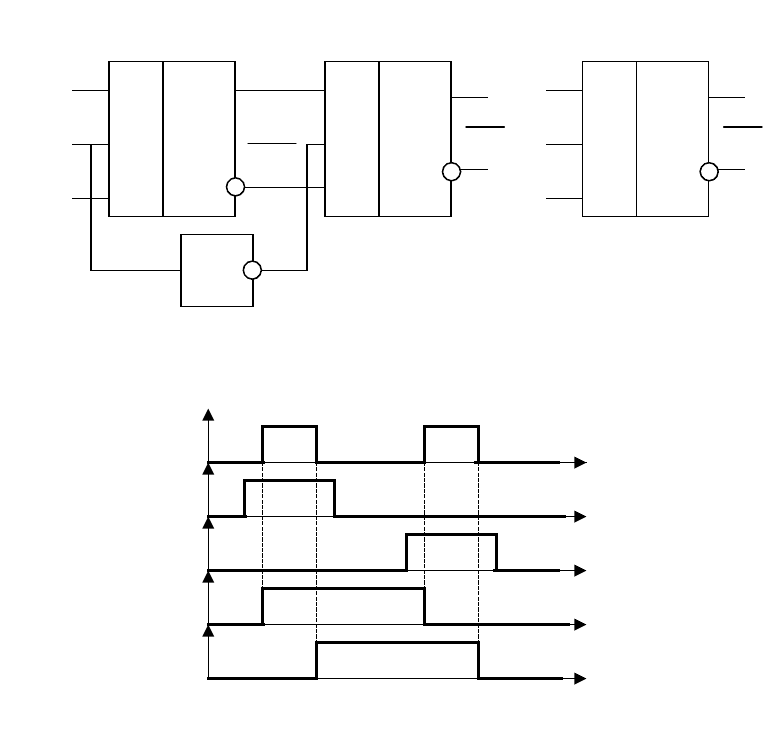

4.2.4. Двухтактный RS – триггер

В некоторых случаях новое состояние триггера оказывается логически зависимо

от состояния своего выхода. В этих случаях используют двухтактные схемы (рис. 18, а).

Двухтактный RS – триггер состоит из двух включенных последовательно

синхронных однотактных триггеров, образующих две ступени. Причем вход

синхронизации второй ступени подключен к входу синхронизации схемы через

инвертор. Поэтому при отсутствии импульса синхронизации (C = 0) входы схемы

закрыты, а на вход C второй ступени подается 1, и она открыта, поэтому состояние

первой и второй ступени одинаковое. При подаче импульса синхронизации (C = 1)

открывается первая ступень и закрывается вторая, что обеспечивает сохранение

предыдущей информации до конца действия импульса синхронизации и прием новой

информации на первую ступень. По окончании импульса синхронизации происходит

закрытие первой ступени, открытие второй и перезапись новой информации с первой

ступени на вторую. Следовательно, на выходе всей схемы устанавливается новая

информация. Таким образом, в данной схеме информация заносится в два приема:

а) б)

R

R

C

S

Q

Q

&

&&

&

Q

Q

S

C

R

T

Первый элемент

нулевой ячейки

Ячейка с адресом 2

29

сначала на первую ступень триггера, а затем на вторую. Наглядно это можно показать

временной диаграммой (рис. 19).

Рис.18. Схема (а) и условное графическое обозначение (б) синхронного двухтактного

RS – триггера

Рис. 19. Временная диаграмма работы двухтактного RS – триггера.

Из диаграммы видно, что в отличие от однотактных схем в двухтактных -

информация устанавливается по заднему фронту импульса синхронизации. Это

гарантирует отсутствие повторного изменения состояния схемы за один цикл

синхронизации даже в том случае, когда входные сигналы через внешние цепи зависят

от выходных.

На условном графическом обозначении (рис.18, б) двухтактные триггеры

обозначаются двумя буквами Т.

4.2.5. Универсальный JK-триггер

Общей особенностью RS - триггера является наличие запрещенного состояния на

входах (S =1, R=1), когда может возникнуть неопределенное состояние. В JK -

триггерах этот режим соответствует инверсии (изменение на противоположное) его

состояния, так называемому счетному режиму, так как триггеры с таким режимом

применяются в счетчиках. Это достигается введением перекрестных обратных связей с

выходов на входы через элементы “И” (рис. 20,а) для двухтактного RS - триггера.

а) б)

Q

Q

S

C

R

TT

R

C

S

Q

’

'Q

S

C

R

T

Q

Q

S

C

R

T

1

Запись 1 Запись 0

t

t

t

t

t

С

Q

Q

’

R

S

Первый элемент

нулевой ячейки

Ячейка с адресом 2

30