Егоров В.А. Основы микропроцессорных систем управления

Подождите немного. Документ загружается.

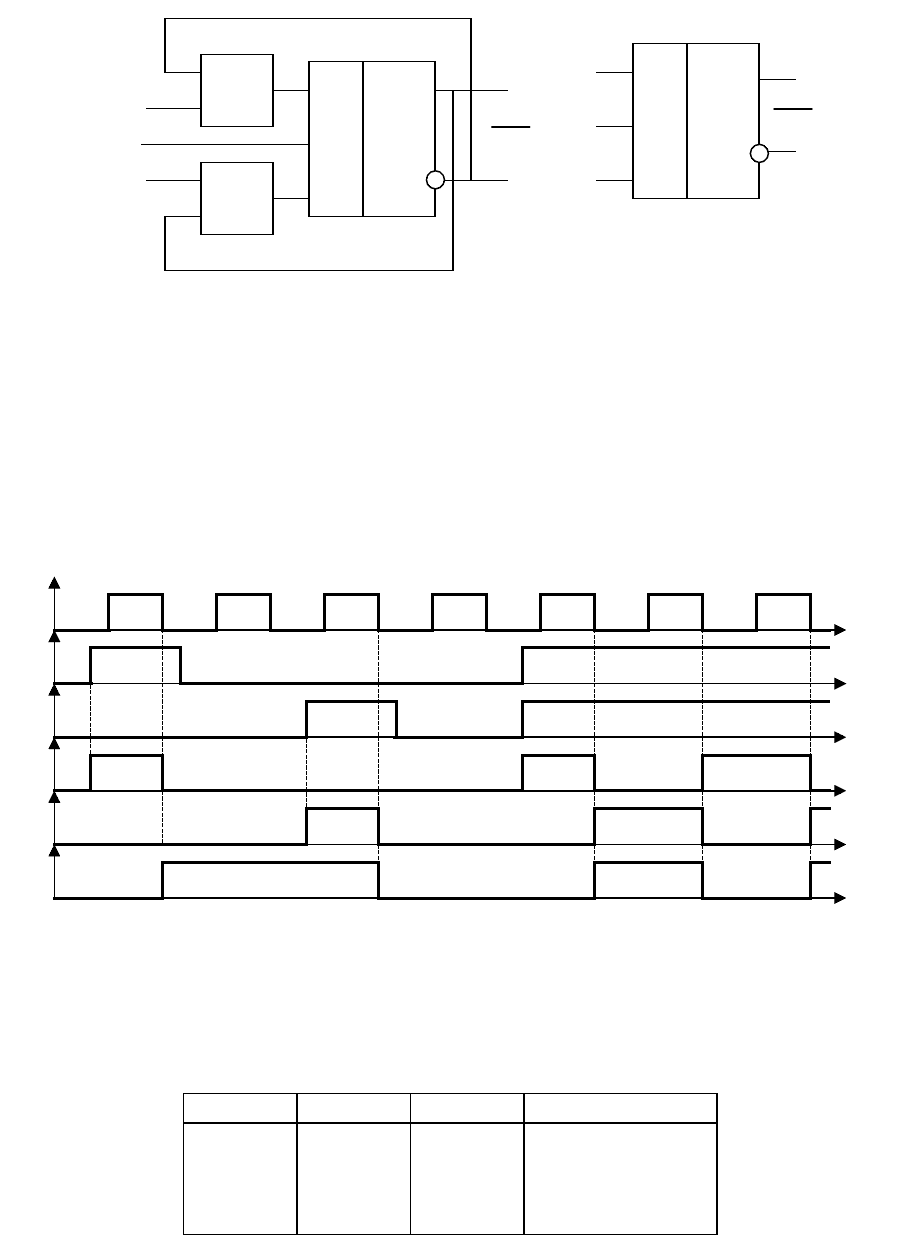

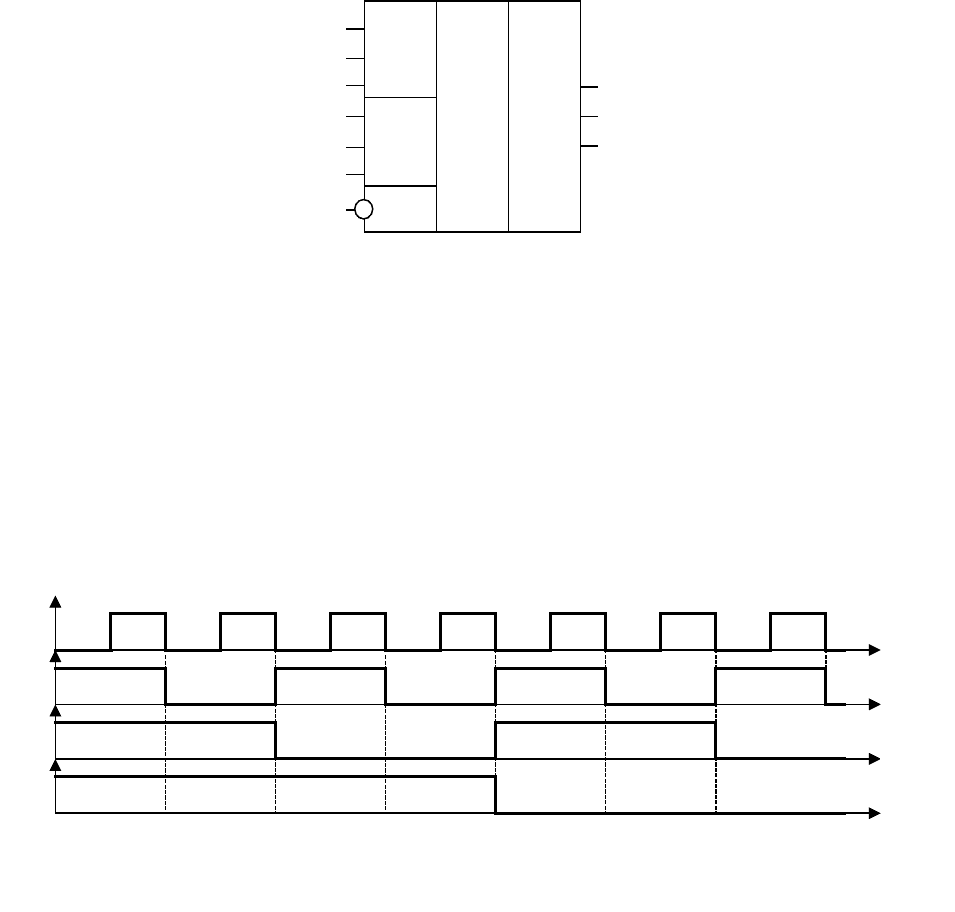

Рис.20. Схема (а) и условное графическое обозначение (б) синхронного двухтактного

JK – триггера

Для данной схемы в нулевом состоянии открыт вход J, а вход K закрыт, в

единичном состоянии – наоборот. Таким образом, если на входы J и K будут

одновременно поданы единицы, то действовать в течение одного цикла синхронизации

будет только одна из них по отрытому входу, что обеспечивает перевод триггера в

противоположное состояние. Работа JK - триггера соответствует временной

диаграмме, представленной на рис. 21.

Рис. 21. Временная диаграмма работы JK –триггера

Состояния для JK – триггера ( при С=1) представлены в табл. 12, условное

обозначение приведено на рис. 20, б.

Таблица 12

J(S) K(R) Q Режим

0

0

1

1

0

1

0

1

х

0

1

x

Хранение

Запись 0

Запись 1

Счётный

JK-триггер удобен тем, что при различных вариантах подключения его входов

можно получить схемы, функционирующие как RS-, D- и T- триггер, поэтому его ещё

называют универсальным триггером.

б)

Q

Q

J

C

K

TT

а)

J

C

K

Q

Q

S

C

R

TT

&

&

Q

t

t

t

t

t

С

R

S

K

J

t

Первый элемент

нулевой ячейки

Ячейка с адресом 2

31

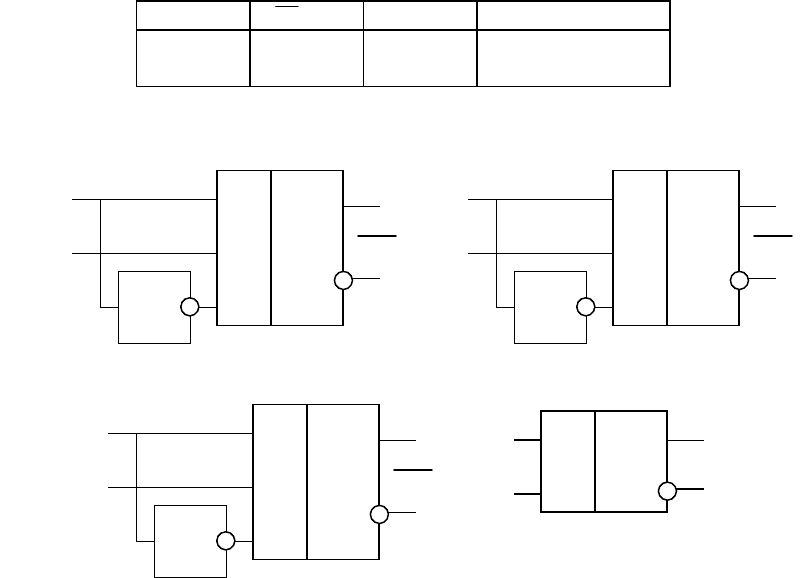

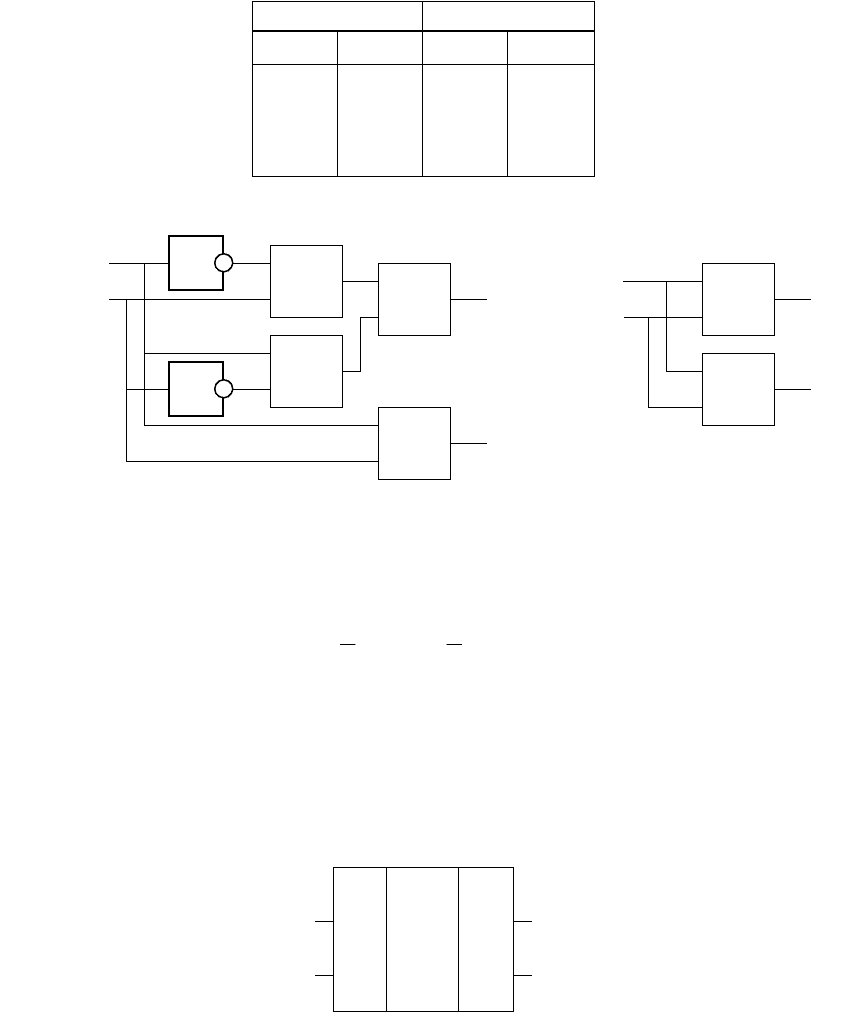

4.2.6. Информационный D-триггер

Этот тип триггера имеет один информационный вход D и по импульсу

синхронизации принимает состояние этого входа. D -триггер всегда имеет вход

синхронизации и широко используется как запоминающий элемент при построении

цифровых схем (в регистрах и блоках регистровой памяти). Он может быть реализован

как на однотактном RS -триггере (рис. 22, а), так и на двухтактных RS и JK -триггерах

(рис. 22). Здесь всегда вход S имеет состояние входа D, а вход R - противоположное

состоянию D. Таким образом, для RS -триггеров в этих схемах есть только два

режима: установки 0 и установки 1 (табл. 13).

При работе однотактные D -триггеры обеспечивают задержку одного сигнала на

полцикла синхронизации (на время паузы), а двухтактные - на один цикл

синхронизации. Условное обозначение D -триггера приведено на рис. 22, г.

Таблица 13

D (S)

D

(R) Q Режим

0

1

1

0

0

1

Запись 0

Запись 1

Рис.22. Схемы (а, б, в) и условное графическое обозначение (г) двухтактного

D – триггера

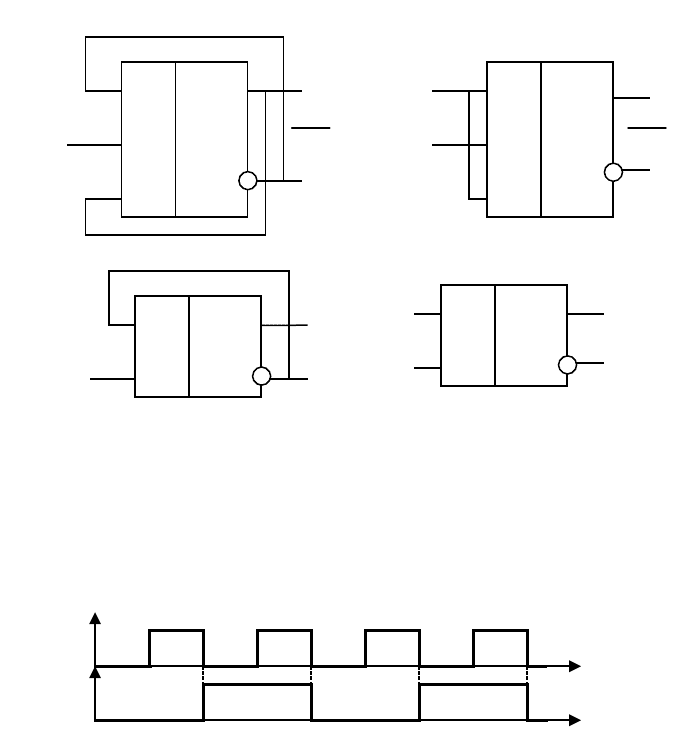

4.2.7. Счётный Т-триггер

У этого типа триггеров тоже только один информационный вход Т - счетный, и

иногда есть дополнительные управляющие: синхронизации (или разрешение на счет),

установки нуля и т.д. Этот триггер может быть построен на основе RS, JK или D-

триггеров (рис. 23). При этом здесь только один режим - счетный.

На рис. 23 приведены схема построения несинхронного Т-триггера на основе RS

и D-триггеров (рис. 23, а, в), а также схема синхронного Т-триггера на основе JK-

триггера (рис. 23, б) и его условное графическое обозначение (рис. 23, г).

а)

D

C

Q

Q

S

C

R

T

1

б)

D

C

Q

Q

S

C

R

TT

1

в)

D

C

Q

Q

J

C

K

TT

1

г)

Q

Q

D

C

TT

Первый элемент

нулевой ячейки

Ячейка с адресом 2

32

Рис. 23. Схемы (а, б, в) и условное графическое обозначение (г) T– триггера

Режим работы Т-триггера соответствует счетному режиму JK -триггера; с каждым

импульсом на входе Т (при наличии импульса синхронизации) триггер меняет свое

состояние на противоположное. Сказанное иллюстрирует временная диаграмма (рис.

24).

Рис. 24. Временная диаграмма работы T– триггера

Все схемы Т-триггера (рис. 23) имеют обратные связи с выхода на вход, поэтому

Т-триггер может быть только двухтактным. Учитывая, что все двухтактные триггеры

срабатывают по заднему фронту, становится понятным, почему моменты переключения

совпадают со спадом импульса на входе Т (рис. 24).

Сопоставляя периоды входной и выходной частот на диаграмме (рис. 24) можно

отметить эффект деления частоты на два.

Описанные свойства Т-триггера позволяют использовать его, как базовый

элемент для построения счётчиков и делителей частоты.

4.2.8. Вопросы для повторения

1. Дайте определение понятию триггер.

2. Как определить состояние триггера?

3. Чем отличается работа асинхронного RS -триггера на элементах "И-НЕ" от

RS -триггера на элементах ''ИЛИ-НЕ"?

4. Какие сигналы на входе необходимы для перевода синхронного RS -триггера в

единичное состояние?

5. Чем отличается работа однотактного и двухтактного RS -триггера?

6. Составьте временную диаграмму работы для JK -триггера.

7. Чем отличается работа RS и D-триггера?

а)

б)

в)

T

C

Q

Q

J

C

K

TT

г)

T

Q

Q

S

C

R

TT

Q

Q

T

C

TT

Q

T

Q

D

C

TT

t

t

T

Q

Первый элемент

нулевой ячейки

Ячейка с адресом 2

33

8. Составьте схему Т-триггера на основе D –триггера и поясните её принцип работы.

9. Составьте временную диаграмму работы Т-триггера.

Первый элемент

нулевой ячейки

Ячейка с адресом 2

34

4.3. Регистры

Регистром называется устройство, предназначенное для запоминания

многоразрядного двоичного слова, а также для выполнения над словом некоторых

преобразований. Регистр представляет собой совокупность D –триггеров, число

которых соответствует количеству разрядов в слове, и вспомогательных схем,

обеспечивающих выполнение некоторых операций, среди которых могут быть:

установка регистра в 0 ("сброс"), приём слова из другого устройства (регистра,

сумматора и т.д.), передача слова в другой регистр, сдвиг слова вправо или влево на

требуемое число разрядов, преобразование последовательного кода слова в

параллельный и наоборот.

Рис. 25. Схема универсального трехразрядного регистра

На рис. 25 приведена схема трехразрядного регистра, позволяющая вводить и

выводить информацию в последовательном и параллельном кодах, сдвигать слова по

разрядам вправо, устанавливать регистр в 0. Регистр выполнен на трёх D-триггерах,

имеет 3 информационных входа D2, D1, D0 и 3 выхода Q2, Q1, Q0, а также

управляющие входы:

R

- установка нуля, С - синхронизации и V – задания режима

работы.

В рабочем состоянии на вход

R

постоянно подается 1. При задании

R

= 0

происходит установка всех триггеров в нулевое состояние, то есть сброс регистра в

нуль.

Для перевода регистра в режим параллельного ввода необходимо подать на вход

V уровень логической единицы. При этом на верхние элементы "И" логических

элементов "2-2И-ИЛИ" поступит 1, и они подключат к входам D-триггеров входы

регистра D2, D1, D0.

Запись параллельного двоичного кода производится в следующем порядке. На

входы D2, D1, D0 выставляют разряды кода. Подают импульс на вход

Q

1

V

C

D

2

D

1

D

0

Q

0

D

C

TT

1&

&

D

C

TT

1&

&

Q

2

D

C

TT

1

R

Первый элемент

нулевой ячейки

Ячейка с адресом 2

35

синхронизации С. По окончании импульса (триггеры двухтактные) по его заднему

фронту триггеры примут состояние входов, и информация будет записана.

Для последовательного ввода информации необходимо на вход V подать

логический нуль, тогда нуль поступит на верхние элементы "И" и закроет их,

отключая тем самым входы D-триггеров от входов регистра D2, D1, D0. В то же

время, пройдя через инвертор, сигнал V откроет нижние элементы "И" и соединит

входы D-триггеров с выходами предыдущих D-триггеров.

Теперь, чтобы ввести информацию, необходимо на вход D2 подать значение

первого разряда вводимого кода, затем подать импульс синхронизации. На первом

триггере установится значение первого разряда. Далее на вход D2 подают значение

второго разряда и снова формируют синхроимпульс. При этом информация с первого

триггера перепишется на второй, а на первом – установится значение вводимого

второго разряда. Аналогично вводится третий разряд кода, при этом по окончании

третьего импульса первый разряд кода запишется в первый триггер, второй разряд – во

второй триггер, а третий (старший) разряд – в третий триггер. При последовательном

вводе надо подавать столько импульсов, сколько разрядов в последовательном коде

или триггеров в регистре (обычно их число совпадает).

Таким образом, при параллельном вводе информация вводится за один такт, но

требуется n входов, где n - разрядность регистра (кода), а при последовательном вводе

требуется n тактов, но всего один вход. Обычно параллельная передача информации

применяется при коротких линиях связи (внутри вычислительных систем), а

последовательная - при длинных линиях связи.

Считывание информации из регистра в параллельном коде осуществляется

одновременным снятием сигналов с выходов Q2, Q1, Q0.

Считывание в последовательном коде выполняется с выхода Q0 в следующем

порядке: с Q0 считывается значение первого разряда, подается импульс на вход С для

сдвига информации по триггерам на один разряд, с выхода Q0 считывается значение

второго разряда, затем снова подается импульс для сдвига, и опять считывание с Q0

значения третьего разряда. Для считывания n -разрядного числа необходимы n

считываний и n сдвигов.

При сдвиге информация в регистре не сохраняется. Для сохранения информации

необходим кольцевой сдвиг.

Регистр, выполненный в виде отдельной микросхемы, имеет следующее условное

графическое обозначение на принципиальной схеме (рис. 26).

Рис. 26. Условное графическое обозначение регистра

4.3.1. Вопросы для повторения

RG

C

V

D0

D1

D2

Q0

Q1

Q2

Первый элемент

нулевой ячейки

Ячейка с адресом 2

36

1. Для чего предназначены регистры?

2. Какие операции выполняют регистры?

3. На каких элементах строятся регистры?

4. Чем отличается параллельный ввод информации от последовательного, в каких

случаях они применяются?

5. Как считывается информация из регистра?

6. Какие регистры называются кольцевыми?

4.4. Счётчики

Счетчик - это устройство, которое служит для подсчета количества импульсов,

поступающих на его вход. По своему назначению счетчики делятся на суммирующие,

вычитающие и реверсивные. В суммирующих счетчиках происходит сложение

поступающих на вход импульсов с числом, которое хранится в счетчике. Вычитающие

счетчики производят вычитание поступивших на вход импульсов из начального числа.

Реверсивные могут как складывать, так и вычитать в зависимости от управляющего

сигнала, который переключает счетчик либо в режим сложения, либо в режим

вычитания.

Двоичные счетчики строятся на основе триггеров со счетным входом и

дополнительных логических схем. Триггеры, входящие в счетчики, образуют его разряды.

Максимально возможное число N , которое может быть зафиксировано счетчиком,

называется его емкостью и для двоичных счетчиков определяется N = 2

n

- 1, где n -

число разрядов.

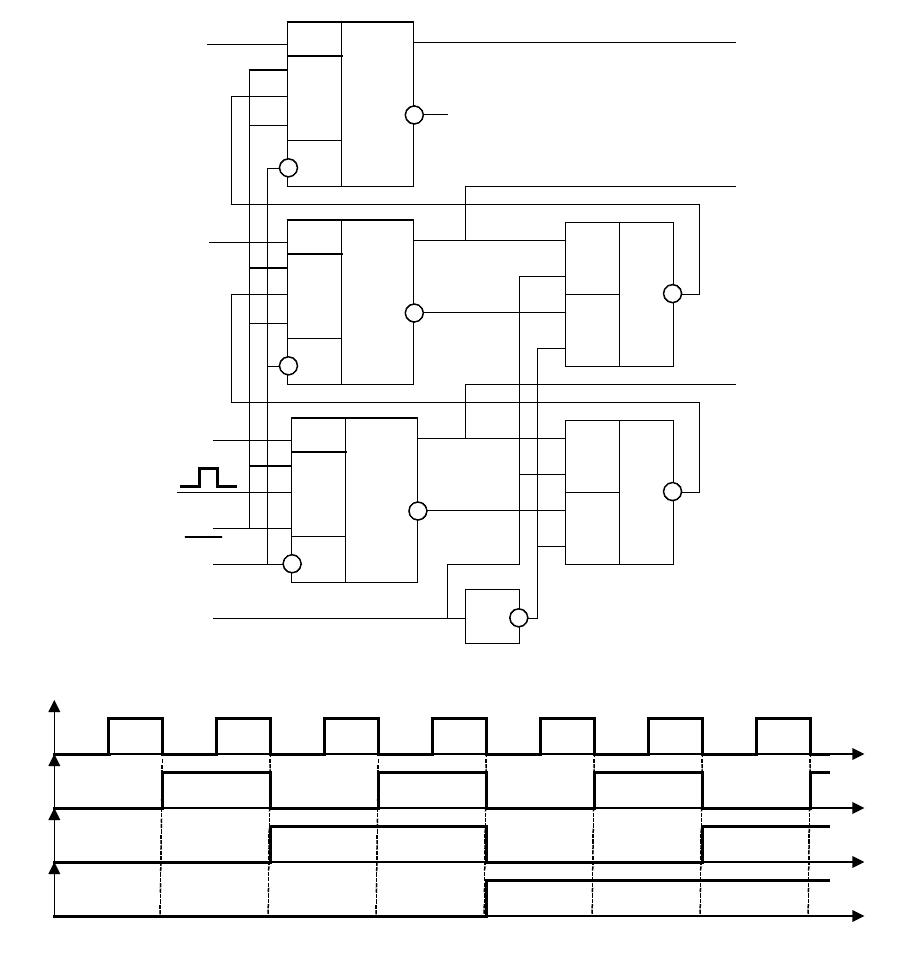

Рассмотрим схему реверсивного счетчика (рис. 27), выполненного на трех JK-

триггерах, работающих в счетном режиме.

На входы J и K всех триггеров подается логическая единица, которая задает

счетный режим триггеров. Установка счетчика в нулевое состояние осуществляется

подачей нулевого импульса по линии

R

, так как соответствующие входы триггеров -

инверсные. В режиме счета

R

= 1.

Начальная установка двоичного числа в счетчик производится следующим

образом. На вход P - "Счет" устанавливается уровень логического нуля, блокирующий

счёт. Начальное число преобразуется в двоичный код и выставляется на входы D2,

D1, D0 счётчика, являющиеся входами установки триггеров. Причём, младший

разряд кода подается на вход D0.

Режим работы счетчика задается управляющим входом V. Если V = 0, то по

линии "Вычитание" на верхние элементы "И" поступают 0, и они будут закрыты, а по

линии "Сложение" будет поступать 1 на нижние элементы "И", которые будут

работать и передавать сигнал с инверсного выхода предыдущего триггера. Учитывая

инверсию на выходе элемента "2-2И-ИЛИ-НЕ", получаем, что на вход С

следующей ступени поступает сигнал, соответствующий состоянию предыдущего

триггера.

В схеме используются двухтактные триггеры, которые срабатывают по заднему

фронту синхроимпульса, то есть при переходе предыдущего триггера из единичного

состояния в нулевое. Учитывая это, строим временную диаграмму для режима

сложения (рис. 28). Первый триггер меняет свое состояние по заднему фронту

импульсов, поступающих на вход С, второй триггер - при переходе первого триггера из

1 в 0, третий - при переходе второго из 1 в 0. Нетрудно убедиться, что состояния

триггеров в двоичном коде соответствуют количеству поступивших импульсов. Из

временной диаграммы хорошо видно, что на выходе каждого триггера частота

Первый элемент

нулевой ячейки

Ячейка с адресом 2

37

1

1

1

7

0

1

1

6

1

0

1

5

0

0

1

4

1

1

0

3

0

1

0

2

1

0

0

1

Q

2

Q

1

t

t

С

Q

0

t

t

t

импульсов в 2 раза меньше, чем на входе, и поэтому на выходе третьего триггера

частота будет уже в 8 раз ниже. Дня n- разрядного счетчика частота будет уже в 2

n

раз

ниже, чем на входе. Поэтому другая область применения счетчиков - деление частоты.

Рис. 27. Схема реверсивного счетчика

Рис. 28. Временная диаграмма работы счетчика в режиме сложения

C

P

R

V

D

2

D

1

D

0

Q

0

S

J

C

K

TT

1&

&

Q

1

S

J

C

K

TT

1&

&

Q

2

S

J

C

K

TT

1

Первый элемент

нулевой ячейки

Ячейка с адресом 2

38

Для перевода счетчика в режим вычитания необходимо на вход V подать

логическую единицу. Тогда через инвертор на линию "Сложение" будет подаваться 0,

который закроет нижние элементы "И", а единица со входа по линии "Вычитание"

поступит на верхние элементы "И", которые будут работать и передавать сигнал с

прямого выхода предыдущего триггера. Учитывая инверсию в элементе "2-2И-ИЛИ-

НЕ", находим, что задний фронт для импульсов на входе С будет соответствовать

переходу предыдущего триггера из 0 в 1. Работа первого триггера не изменится. Если

построить временную диаграмму, то можно легко убедиться, что изменение состояния

триггеров будет соответствовать вычитанию на 1 с приходом каждого импульса. Во

временной диаграмме предполагалось, что вначале в счетчик было занесено число 7

(рис. 29).

Информация со счетчика снимается с выходов Q2, Q1, Q0. Если счетчик выполнен

в корпусе отдельной микросхемы, то он имеет условное графическое обозначение (рис.

30).

Рис. 30. Условное графическое обозначение счётчика

4.4.1. Вопросы для повторения

1. Для чего предназначены счетчики?

2. Перечислите типы счетчиков.

3. На каких элементах строятся счетчики?

4. Как устанавливается начальное двоичное число в счетчик?

5. Какой коэффициент деления частоты у счётчика на 6 разрядов?

6. Нарисуйте условное графическое обозначение счётчика на принципиальной схеме.

4.5. Арифметико-логическое устройство

D0

D1

D2

CT2

C

V

P

1

2

4

1

2

4

Q0

Q1

Q2

Первый элемент

нулевой ячейки

Ячейка с адресом 2

1

1

1

7

1

0

0

1

0

1

0

2

1

1

0

3

0

0

1

4

1

0

1

5

0

1

1

6

Q

2

Q

1

t

t

С

Q

0

t

t

t

Рис. 29. Временная диаграмма работы счетчика в режиме вычитания

39

Арифметико-логическое устройство (АЛУ) предназначено для выполнения

арифметических и логических операций над двумя двоичными кодами одинаковой

разрядности.

Основными операциями АЛУ являются: сложение, вычитание, логическое

умножение, логическое сложение и инверсия.

Операция сложения выполняется сумматором.

4.5.1. Сумматор

Сумматор – это цифровой элемент для сложения двух одноразрядных двоичных

чисел. Он может быть разбит на две одинаковые части – полусумматоры.

Полусумматор имеет два входа А и В, на которые поступают складываемые

операнды и два выхода: выход сигнала суммы S

’

и выход сигнала переноса в старший

разряд Р

’

.

Схема полусумматора может быть получена из таблицы операции двоичного

сложения (табл. 14).

Таблица 14

Вход Выход

А В

Р

’

S

’

0

0

1

1

0

1

0

1

0

0

0

1

0

1

1

0

Рис. 31. Схема полусумматора: (а) на элементах "И", "ИЛИ", "НЕ"; (б) на элементах

"И", "исключающее ИЛИ"

Табл. 14 соответствуют следующие логические выражения (в дизъюнктивной

нормальной форме):

.B*AP

;BAB*AB*AS

'

'

Таким образом, для реализации полусумматора необходимы логические

элементы: "исключающее ИЛИ" и элемент "И". Варианты реализации

полусумматора приведены на рис. 31.

Условное графическое изображение полусумматора изображено на рис. 32.

а) б)

P

’

S

’

A

&

1

&

1

1

&

B

S

’

P

’

A

&

B

=1

HS

A

B

S

’

P

’

Первый элемент

нулевой ячейки

Ячейка с адресом 2

40