Ченцов С.В. Автоматизированное проектирование средств и систем управления

Подождите немного. Документ загружается.

ТЕМА 3. МОДЕЛЬНОЕ ПРЕДСТАВЛЕНИЕ СРЕДСТВ И СИСТЕМ УПРАВЛЕНИЯ (ССУ)

Лекция 5. Методы формирования моделей ССУ

Автоматизированное проектирование средств и систем управления. Курс лекций

81

ния этих матриц можно автоматизировать. При этом, если уравнения законов

Кирхгофа составлены с помощью топологических матриц, то эти уравнения

всегда будут линейно независимыми и, образованная с их помощью матема-

тическая модель объекта не будет вырожденной, т. е. всегда будет иметь ре-

шение. Каждое из уравнений сечений (5.7)

будет отличаться от других тем,

что содержит ток ветви дерева I

ВД

, которого нет в других уравнениях (в соот-

ветствии с принципом построения сечений дерева), а каждое из контурных

уравнений (5.6)

будет отличаться от других тем, что содержит напряжение на

хорде, которого нет в других уравнениях (в соответствии с принципом по-

строения главных контуров).

Базис метода переменных состояния составляют переменные состоя-

ния – переменные типа потока через элементы типа С(I

C

), переменные типа

разности потенциалов на элементах типа L(U

L

) и производные переменных

состояния.

Метод переменных состояния – единственный из методов формирова-

ния ММ системы (устройства), который позволяет получить математическую

модель в нормальной форме. В общем случае методика получения ММ сис-

темы в нормальной форме состоит из двух этапов. Пусть имеется система то-

пологических и компонентных уравнений, причем компонентными уравне-

ниями реактивных элементов служат дифференци

альные зависимости

dt

dI

L;U

dt

dU

CI

L

L

C

C

.

(5.8)

Первый этап заключается в том, что на основе законов Кирхгофа пере-

менные состояния выражаются через токи и напряжения остальных ветвей:

1

f I

C

(остальные переменные);

2

fU

L

(остальные переменные).

(5.9)

На втором этапе I

C

и U

L

заменяются производными в соответствии

с (5.8)

, а остальные переменные с помощью комбинирования законов Кирх-

гофа и компонентных уравнений выражаются через U

С

и I

L

. В результате

вместо системы топологических и компонентных уравнений получим ММ

системы в нормальной форме:

(t))(t),I(Uf

Ldt

dI

(t))(t),I(Uf

Cdt

dU

LC

L

LC

C

2

1

1

1

.

(5.10)

ТЕМА 3. МОДЕЛЬНОЕ ПРЕДСТАВЛЕНИЕ СРЕДСТВ И СИСТЕМ УПРАВЛЕНИЯ (ССУ)

Лекция 5. Методы формирования моделей ССУ

Автоматизированное проектирование средств и систем управления. Курс лекций

82

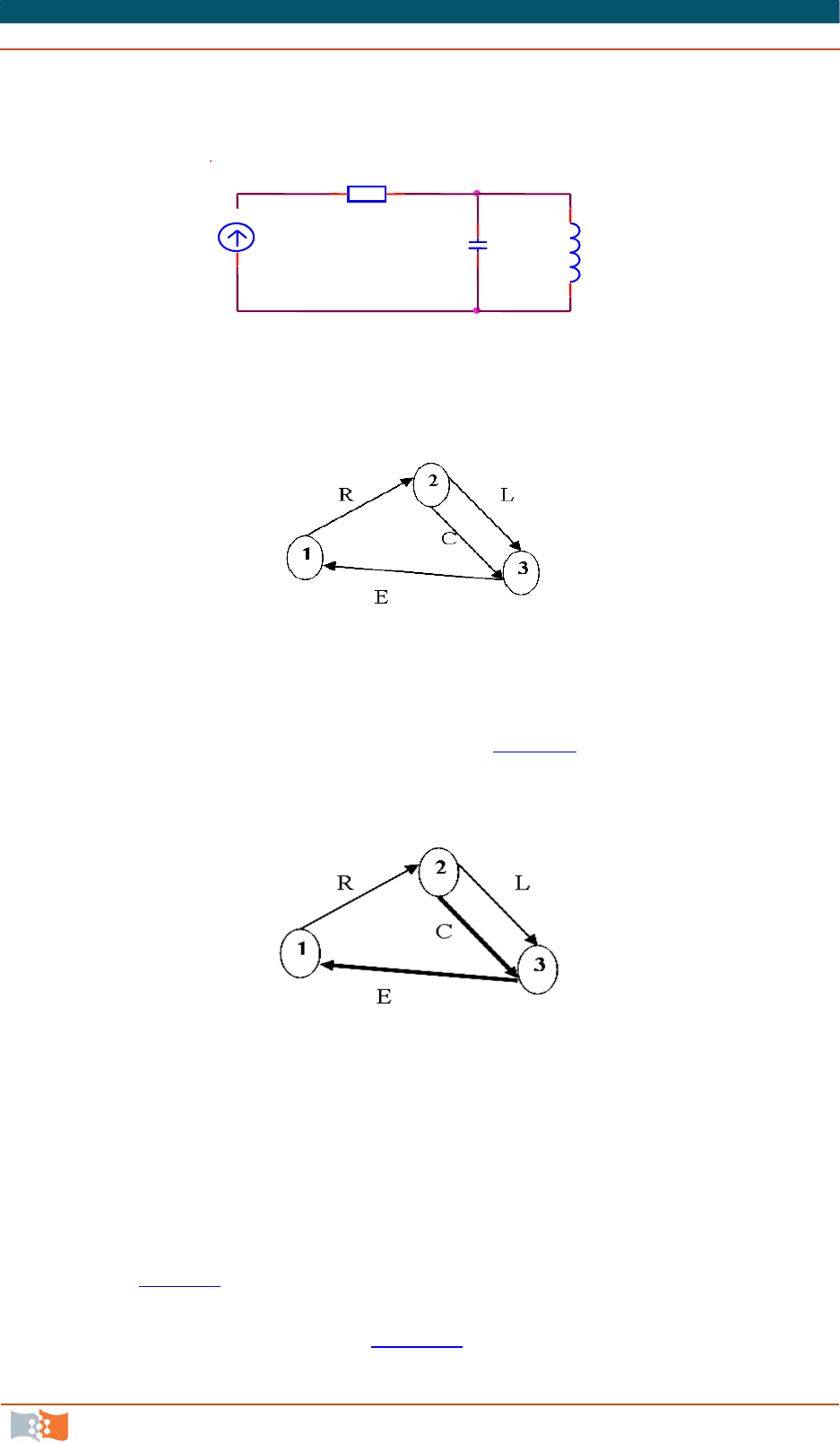

Рассмотрим получение ММС на примере RLC-схемы.

1. Составим эквивалентную схему объекта

Рис 5.6

Рис. 5.7

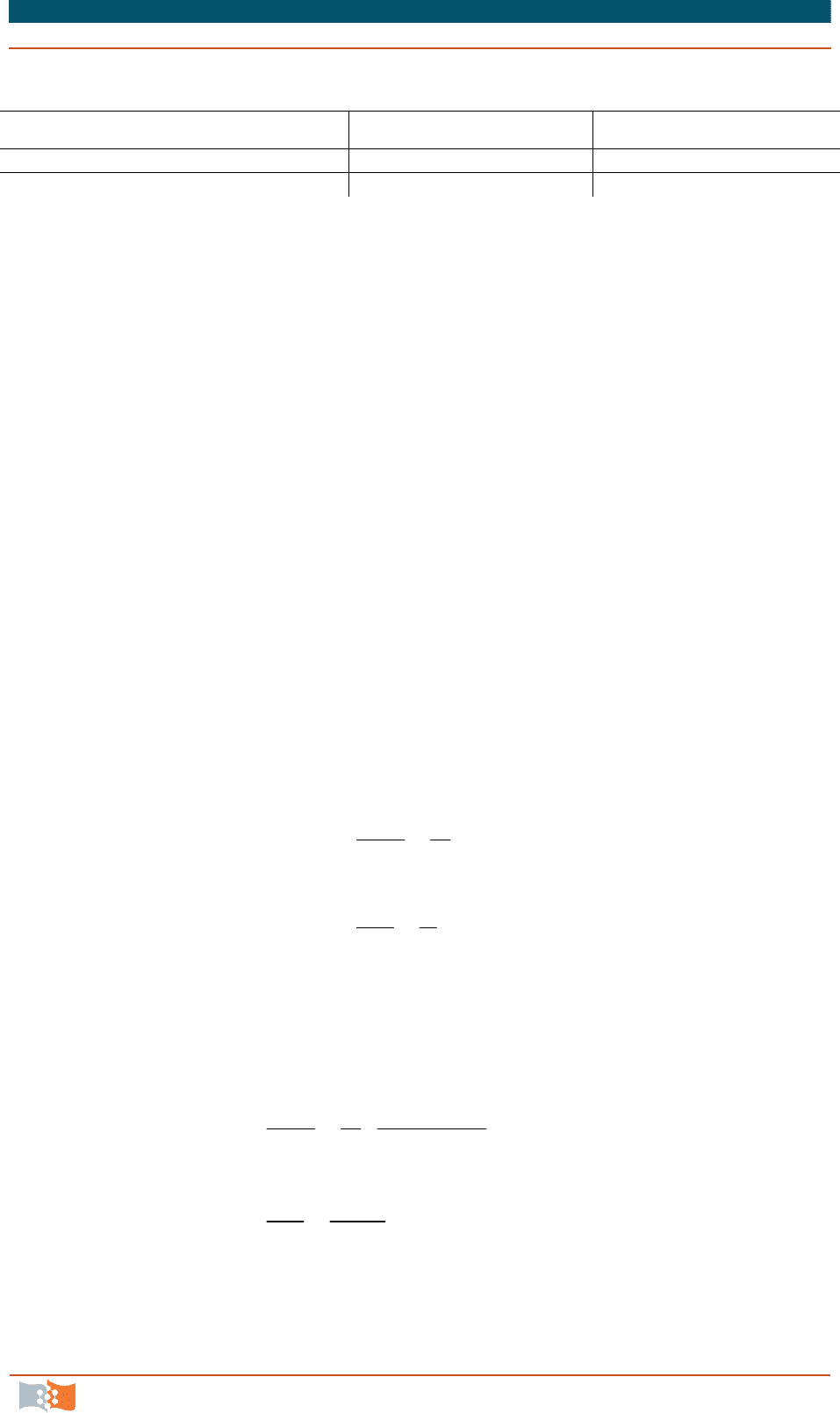

2. Строим граф эквивалентной схемы (рис. 5.7

). Граф практически по-

вторяет эквивалентную схему, но без условных изображений ветвей.

Рис. 5.8

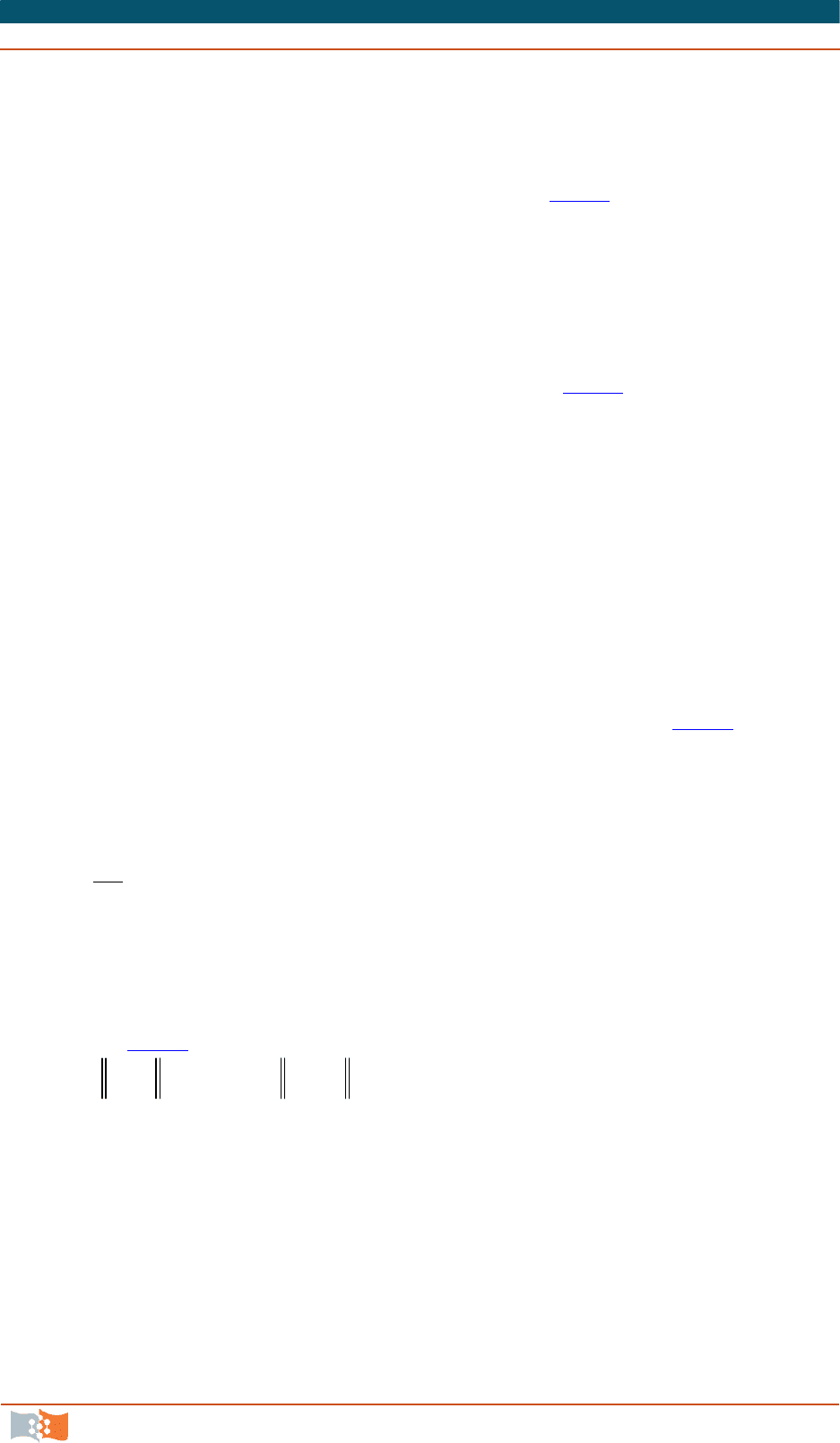

3. Выбираем нормальное дерево графа. Если в схеме имеются контуры

из U-элементов или звезды из I-элементов, то необходимо преобразование

одного из U-элементов в I-элемент и исключение его из дерева или соответ-

ственно преобразование одного из I-элементов в U-элемент и включение его

в дерево. На рис. 5.8

ветви дерева представлены утолщенными линиями.

4. Строим матрицу контуров и сечений, где столбцы соответствуют

ветвям дерева, а строки – хордам (табл. 5.3

).

C

L

2

3

R

1

E

ТЕМА 3. МОДЕЛЬНОЕ ПРЕДСТАВЛЕНИЕ СРЕДСТВ И СИСТЕМ УПРАВЛЕНИЯ (ССУ)

Лекция 5. Методы формирования моделей ССУ

Автоматизированное проектирование средств и систем управления. Курс лекций

83

Таблица 5.3

Обозначение Ветвь Е Ветвь С

Хорда R + 1 + 1

Хорда L 0 – 1

5. Для получения топологических уравнений ск

анируем М-матрицу по

строкам и столбцам. При сканировании по строкам получаем уравнения не-

прерывности (неразрывности), при сканировании по столбцам – уравнения

равновесия. При получении уравнений непрерывности знаки элементов мат-

рицы меняются на противоположные:

0,

0,

0,

0.

ECR

CL

ER

CRL

UUU

UU

II

III

6. Добавляем компонентные уравнения всех ветвей:

const,

,

1

,

1

.

E

RR

C

C

L

L

U

UIR

dU

I

dt C

dI

U

dt L

7. Получаем нормальную форму Коши, раскрывая правые части по-

следних двух уравнений с комбинированием топологических и оставшихся

компонентных уравнений:

1

,

.

CEC

L

C

L

dU U U (t)

I

(t)

dt C R

U(t)

dI

dt L

Далее, используя численный метод интегрирования, получаем ММС в

алгебраизованной форме. Таким образом, в методе переменных состояния

ТЕМА 3. МОДЕЛЬНОЕ ПРЕДСТАВЛЕНИЕ СРЕДСТВ И СИСТЕМ УПРАВЛЕНИЯ (ССУ)

Лекция 5. Методы формирования моделей ССУ

Автоматизированное проектирование средств и систем управления. Курс лекций

84

предварительная алгебраизация компонентных уравнений не требуется, по-

этому при программной реализации метода библиотека математических мо-

делей элементов не связана с библиотекой методов интегрирования.

Назовем основные недостатки метода переменных состояния:

1. Сложность формирования ММС в виде (5.10)

. Нормальная форма

Коши не может быть получена, если в ветви дерева попадет ветвь типа L или

в хорды – ветвь типа C.

2. Ориентация на явные методы решения системы уравнений ММС.

Явные методы практически нельзя использовать для расчета схем с большим

разбросом постоянных времени, т. е. жестких ММС, из-за ограничений на

шаг расчета.

3. Реализация неявных методов для системы (5.10)

затруднительна из-

за сложности вычисления матрицы Якоби.

Узловой метод формирования ММ сист

емы – метод, базис которого

составляют переменные типа потенциала (узловые потенциалы). В основе

узлового метода лежит уравнение равновесия, т. е. су

мма переменных типа

потока в уз

лах эквивалентной схемы равна нулю

)

I

( ,

(5.11)

где I – вектор переменных типа потока, – вектор переменных типа потен-

циала, характеризующих состояние узла.

Теоретическая модель-алгоритм, используемая для расчета схемы,

обычно формируется в виде, соответствующем решению (5.11)

методом

Ньютона

)I()ΔY(

PPP

,

(5.12)

где

I

Y

– матрица узловых проводимостей, p – индекс ньютоновских

итераций,

1

Δ

PP P

– вектор поправок,

()

P

I

– вектор узловых токов

(вектор невязок).

После этого считаем, что

1

Δ

PPP

, и снова формируем и реша-

ем систему (5.12)

. Цикл заканчивается при выполнении одного из следующих

условий

1

Δ

P

, либо

2

()I

или по их комбинации, где

1

– задавае-

мая норма вектора приращений,

2

– задаваемая норма вектора невязок. Цикл

также может быть завершен неудачно по превышению числа итераций.

Таким образом, для получения математической модели объекта в узло-

вом базисе необходимо сформировать матрицу узловых проводимостей и

вектор невязок.

Методика формирования ММС состоит в последовательном рассмот-

рении каждого элемента схемы и определения его вклада в вектор узловых

токов и матрицу узловых проводимостей.

ТЕМА 3. МОДЕЛЬНОЕ ПРЕДСТАВЛЕНИЕ СРЕДСТВ И СИСТЕМ УПРАВЛЕНИЯ (ССУ)

Лекция 5. Методы формирования моделей ССУ

Автоматизированное проектирование средств и систем управления. Курс лекций

85

Формирование вектора узловых токов состоит в образовании для каж-

дого узла схемы суммы полюсных токов элементов, соединенных с данным

узлом. При этом считается, что ток, втекающий в узел, входит в узловой ток

данного узла со знаком «–», а вытекающий – со знаком «+».

При формировании матрицы узловых проводимостей используется

принцип позиционного суммирования, заключающийся в том, что элемент

ik

Y

матрицы Y() получается суммированием всех проводимостей элементов

схемы, включенных между узлами i и k, в том числе взаимной проводимости

ik

y , которая входит в состав матрицы

npj

Y

–полюсника, если i и k являются его

полюсами. Аналогично в состав элемента

ii

Y матрицы Y() входит как сла-

гаемое собственная проводимость

nii

y

–полюсника, если i-й узел схемы одно-

временно является полюсом n–полюсника. Например, любой биполярный

транзистор можно рассматривать как трехполюсник с матрицей проводимо-

стей

КК

y

КБ

y

ЭК

y

КБ

y

ББ

y

ЭБ

y

ЭК

y

ЭБ

y

ЭЭ

y

Y

ТР

.

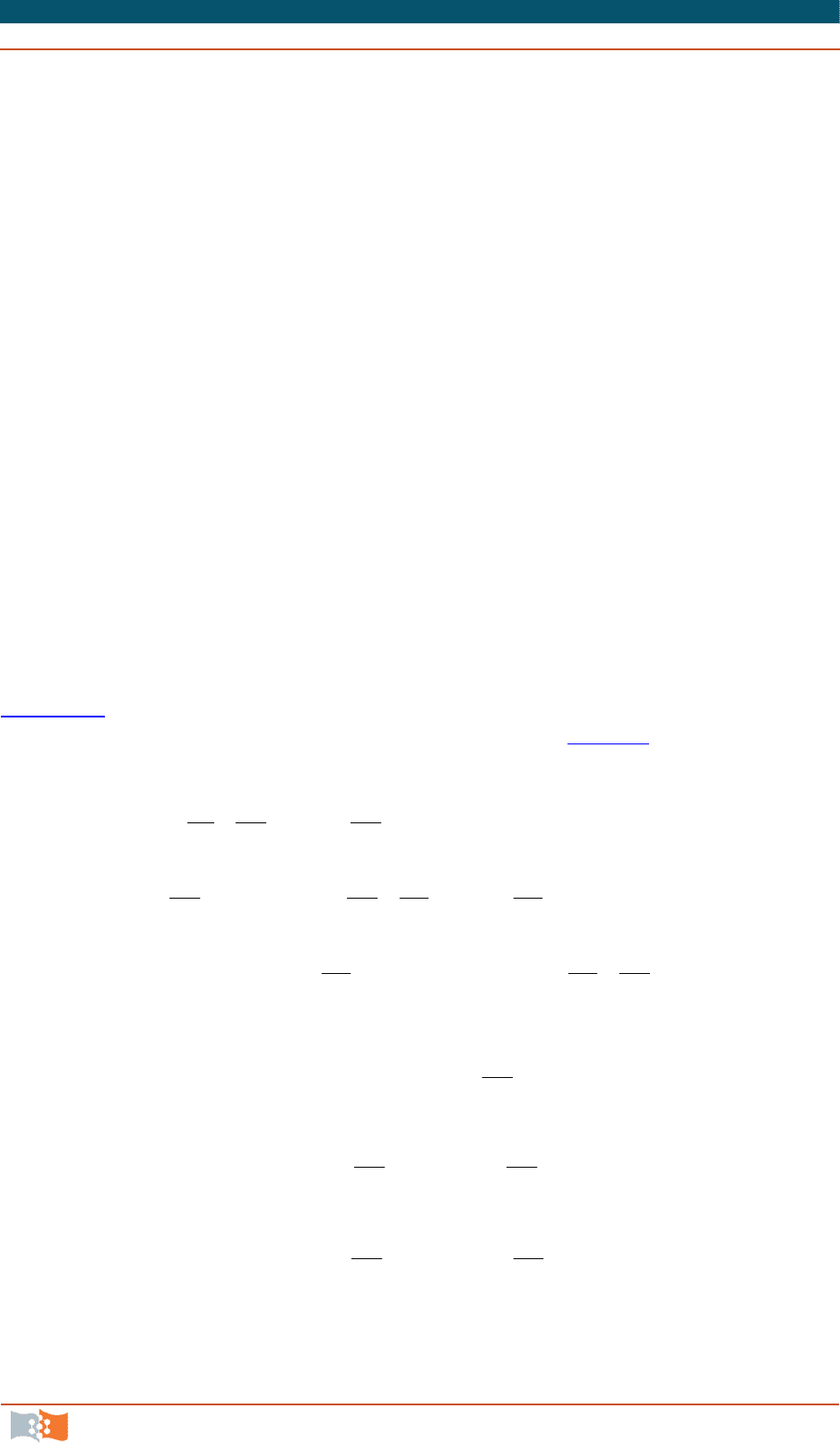

Рассмотрим формирование ММС для схемы, представленной на

рис.5.5, а

. Размерность математической модели определяется числом узлов

схемы минус 1, т. е. в нашем случае она равна трем (рис. 5

.9).

Рис.5.9

3

4

1

32

2

1

32

2

2

1

32

2

1

21

2

1

21

3

2

1

4

1

3

1

322

3

1

0

2

3

1

3

1

2

1

2

2

1

0

2

1

2

1

1

1

1

C

Y

R

C

Y

R

)-(

C

Y

R

)(

R

)(

R

)(I

Δ

Δ

Δ

RR

C

Y

C

Y

C

Y

R

C

Y

RRR

C

Y

R

RRR

C

Y

I

Y

Рис. 5.9

ТЕМА 3. МОДЕЛЬНОЕ ПРЕДСТАВЛЕНИЕ СРЕДСТВ И СИСТЕМ УПРАВЛЕНИЯ (ССУ)

Лекция 5. Методы формирования моделей ССУ

Автоматизированное проектирование средств и систем управления. Курс лекций

86

Как следует из (5.11), допустимый вид компонентного уравнения

I = I(

), т. е. напрямую узловой метод может быть применен к анализу стати-

ческих состояний. Но одна из основных задач анализа объекта на макроуров-

не – это анализ объекта во временной области, т. е. анализ динамических ха-

рактеристик. Динамические процессы в объекте определяются реактивными

элементами типа C и L. Если привести компонентные уравнения элементов C

и L к виду I = I(

), то можно говорить и об анализе динамики. Компонентное

уравнение для элемента типа C дискретизируем с помощью какого-либо

метода численного интегрирования, например, с помощью неявного метода

Эйлера:

n

h

Cn

U

Cn

U

dt

Cn

dU

1

, h

n

– шаг интегрирования в n-й момент

времени:

11

Cn

U

n

h

C

ji

n

h

C

Cn

U

Cn

U

n

h

C

Cn

I .

Таким образом, на одном шаге численного интегрирования мы получи-

ли компонентное уравнение в допустимом виде, и модель элемента типа С

может быть представлена в виде

1

1

Cn

U

n

h

C

ji

n

h

C

Cn

U

n

h

C

ji

n

h

C

Δ

Δ

h

C

h

C

h

C

h

C

j

i

nn

nn

.

Аналогично для элемента типа L:

1

Ln

I

Ln

I

n

h

L

dt

Ln

dI

L

Ln

U

или

ji

L

n

h

Ln

I

Ln

I

1

.

Математическая модель для элемента L выглядит следующим образом:

ji

L

n

h

Ln

I

ji

L

n

h

Ln

I

Δ

Δ

L

h

L

h

L

h

L

h

j

i

nn

nn

1

1

.

ТЕМА 3. МОДЕЛЬНОЕ ПРЕДСТАВЛЕНИЕ СРЕДСТВ И СИСТЕМ УПРАВЛЕНИЯ (ССУ)

Лекция 5. Методы формирования моделей ССУ

Автоматизированное проектирование средств и систем управления. Курс лекций

87

Основные достоинства узлового метода:

1. Малая размерность математической модели объекта;

2. Отсутствие проблемы топологических вырождений, поскольку узло-

вые потенциалы независимо от топологии схемы всегда образуют невырож-

денный базис;

3. Простота формирования ММ системы (ММС) в виде алгоритма, ко-

торому соответствует ММС в неявной форме и, как следствие, простота реа-

лизации неявных методов решения ОДУ;

4. Простые алгорит

мы работы с многополюсными элементами, что по-

зволяет разрабатывать библиотеки ММЭ с вложенными элементами.

Недостатки узлового метода:

1. Ограничение на вид компонентного уравнения;

2. Методы численного интегрирования ОДУ при формировании ММС

встраиваются в компонентные уравнения реактивных ветвей.

Современные автоматизированные методы формирования дискретных

устройств СУ в САПР основаны на использовании входных языков логиче-

ского уровня, которые чаще всего создаются как непроцедурные. Логиче-

ский уровень характеризуется испо

льзованием моделей, составляемых из

моделей отдельных логических элементов (триггеров, элементов И-HE, ИЛИ-

HE) Эти модели могут отражать выполнение логических функций с учетом

временных задержек. Модель, отражающая протекающие в схеме процессы,

называется асинхронной. Модель, отражающая отдельные состояния схемы

(чаще всего установившиеся), называет

ся синхронной. Другими словами,

асинхронная модель – это имитационная модель, представленная средствами

функционально-логического уровня.

Описание схемы на входном языке задаются в виде списка элементов

моделируемой схемы. В каждой строке списка указывают: тип очередного

элемента, его имя или имена его выходов, связи входов элементов с выхода-

ми други

х элементов, возможно указание задержки. Все связи имеют свои

имена, обычно совпадающие с именами соответствующих выходов элемен-

тов. Отдельные строки служат для перечисления выходов элементов, являю-

щихся выходами всей схемы, и задания входных последовательностей, реак-

ция на которые должна быть получена как результат моделирования.

Примером языка моделирования дискретных электронных устройств

на логическом уровне мож

ет служить язык VHDL (Very high-speed integrated

circuits Hardware Design Language), ут

вержденный в качестве международно-

го стандарта IEEE 1076 в 1987 году. Язык VHDL успешно используется и при

синтезе устройств [2

].

В дальнейшем стандарт корректировался и расширялся, новые версии

приняты в 1993 и 1999 годах. Так, версия 1999 году, получившая индекс

IEEE 1076.1, содержит средства описания аналоговых и смешанных моделей.

ТЕМА 3. МОДЕЛЬНОЕ ПРЕДСТАВЛЕНИЕ СРЕДСТВ И СИСТЕМ УПРАВЛЕНИЯ (ССУ)

Лекция 5. Методы формирования моделей ССУ

Автоматизированное проектирование средств и систем управления. Курс лекций

88

Эти описания вместе с базовым вариантом языка VHDL образуют язык

VHDL-AMS (VHDL – Analog and Mixed Signal).

VHDL – не единственный язык проектирования дискретных устройств

СУ. Так, для проектирования интегральных схем широко применя

ется

Verilog, близкий к C++ язык SystemC, язык описания цепей EDIF, языки про-

ектирован

ия устройств на ПЛИС и др., но для сквозного проектирования на

всех треб

уемых для СБИС уровнях функционального проектирования (выше

схемот

ехнического) наибольшее распространение получили VHDL и Verilog.

В VHDL имеются средства для поведенческих и структурных описа-

ний. Описание схемы на языке VHDL включает две части.

Первая часть – описание схемы как компонента некоторой надсистемы,

т. е., прежде всего, описание интерфейсов схемы с внешн

ей средой. Вид этой

части, называемой сущностью, – entity:

entity имя_сущности is

<декларации>

...

end имя_сущности;

Назначение второй части – описание внутренних свойств схемы

(структуры или функций), она называется архитектурным те

лом:

architecture имя_ахитектурного_тела of имя_сущности is

<декларации>

...

begin

описание_схемы_или_алгоритма

end имя_архитектурного_тела;

У одной схемы (сущности) может быть несколько архитектурных тел,

так как могут быть описаны разные аспекты (структура или алгоритмы) и

версии объекта, причем на разных иерархических уровнях.

В декларациях архитектурного тела объявляются типы, фигури

рующие

в данном архитектурном теле. Ими могут быть используемые типы компо-

нентов (объекты), параметры и сигналы. В декларации могут входить также

описания процедур, функций, типов данных.

Различают структурное и поведенческое описание сущностей. Струк-

турные описания служат для представ

ления структурных схем, а поведенче-

ские описания слу

жат для представления функций и алгоритмов, выполняе-

мых устройством.

ТЕМА 3. МОДЕЛЬНОЕ ПРЕДСТАВЛЕНИЕ СРЕДСТВ И СИСТЕМ УПРАВЛЕНИЯ (ССУ)

Лекция 5. Методы формирования моделей ССУ

Автоматизированное проектирование средств и систем управления. Курс лекций

89

Ф

Ф

о

о

р

р

м

м

и

и

р

р

о

о

в

в

а

а

н

н

и

и

е

е

м

м

а

а

т

т

е

е

м

м

а

а

т

т

и

и

ч

ч

е

е

с

с

к

к

и

и

х

х

м

м

о

о

д

д

е

е

л

л

е

е

й

й

с

с

и

и

с

с

т

т

е

е

м

м

у

у

п

п

р

р

а

а

в

в

л

л

е

е

н

н

и

и

я

я

При рассмотрении системы управления на верхнем (первом при ис-

пользовании нисходящего проектирования) уровне описания (рис. 4.3

) про-

исходит дальнейшее абстрагирование от физических особенностей функцио-

нирования устройств и элементов системы [6

; 12]. На этом уровне описыва-

ются в основном информационные процессы в СУ при прохождении фазовой

переменной типа сигнал от входа к выходу. Математическое описание СУ

зависит от применяемого математического аппарата, который в свою очередь

определяет и методы формирования ММ СУ. Необходимо отметить, что по-

лучение математических моделей на первом уровне описания СУ наиболее

трудноф

ормализуемый процесс, по сравнению с подходами, принятыми на

низших уровнях описания: уровень элементов и уровень устройств системы

[10

].

При формировании описания СУ на первом уровне используют ряд уп-

рощений и допущений, главные из которых формулируются следующим об-

разом:

1) однонаправленность в передаче сигналов, т. е. использование моде-

лей, в которых отсутствует влияние выходных переменных на состояние

входных переменных;

2) отсутствие влияния нагрузки на параметры и состояние моделируе-

мого объекта;

3) использование вм

есто фазовых переменных двух типов U и I, пере-

менных одного типа, называемых сигналом;

4) линейность моделей инерционных элементов.

Для математических моделей первого уровня характерны те же типы

уравнений, что и для ММ уровня устройств СУ, но эти уравнения включают

фазовые переменные, описывающие состояние укрупненных элементов сис-

темы. Если определен закон непрерывного перехода объекта из одн

ого со-

стояния в другое, то для анализа ММ СУ используют аппарат передаточных

функций, а при рассмотрении состояний объекта в дискретные моменты вре-

мени ОДУ и их системы переходят в разностные уравнения относительно

значений фазовых переменных в эти моменты времени. В случае дискретного

множества состояний объектов прим

еняют также аппарат математической

логики и конечных автоматов.

Иногда для сложных информационных систем удается перейти к дис-

кретному представлению фазовых переменных. Тогда ММ СУ становится

системой логических соотношений (СЛС), описывающей процессы преобра-

зования сигналов. Использование СЛС применительно к таким сложным сис-

темам более экономично, чем описание изменения в электрических цепях

ТЕМА 3. МОДЕЛЬНОЕ ПРЕДСТАВЛЕНИЕ СРЕДСТВ И СИСТЕМ УПРАВЛЕНИЯ (ССУ)

Лекция 5. Методы формирования моделей ССУ

Автоматизированное проектирование средств и систем управления. Курс лекций

90

информационной системы напряжений и токов как непрерывных функций

времени при помощи ОДУ или их систем.

Значит, для формирования математических моделей СУ на первом

уровне описания используются те же методы, что и для ММ второго уровня

описания СУ, где в качестве базовых будут рассматриваться укрупненные

элементы системы.

Получение имитационных ММ и ММ массового обслуживания, описы-

вающие функционирование сложных вычисли

тельных и информационных

систем, производственных участков, линий, цехов, предприятий и их объе-

динений, возможно на основе универсальных языков программирования, но

получающаяся при этом программная реализация имитационных моделей

СМО оказывается громоздкой, длительность разработки может превысить

разумные пределы. Поэтому применяют проблемно ориентированные языки

имитационного моделирования: общецелевые предназначенные дл

я модели-

рования различных объектов, представляемых моделями СМО (GPSS,

СТРУМ и др.); специализированные языки, ориентированные на анализ узко-

го класса объектов, например, для моделирования вычислительных систем

(язык МПЛ/ВС). При этом увеличивается эффективность в разработке и ис-

полнении программ.

При разработке сложных моделей перед кодированием имитационной

модели объекта на выбранном языке моделирования ц

елесообразно увеличи-

вать наглядность и представлять структуру модели с помощью сетей Петри.

Графическое изображение сети Петри удобно для восприятия и легко преоб-

разуется в исходную программу имитационного моделирования. Для кодиро-

вания применяются специальные языки сетей Петри и общецелевые языки

имитационного моделирования.