Wilamowski B.M., Irwin J.D. The Industrial Electronics Handbook. Second Edition: Industrial Communication Systems

Подождите немного. Документ загружается.

18-4 Industrial Communication Systems

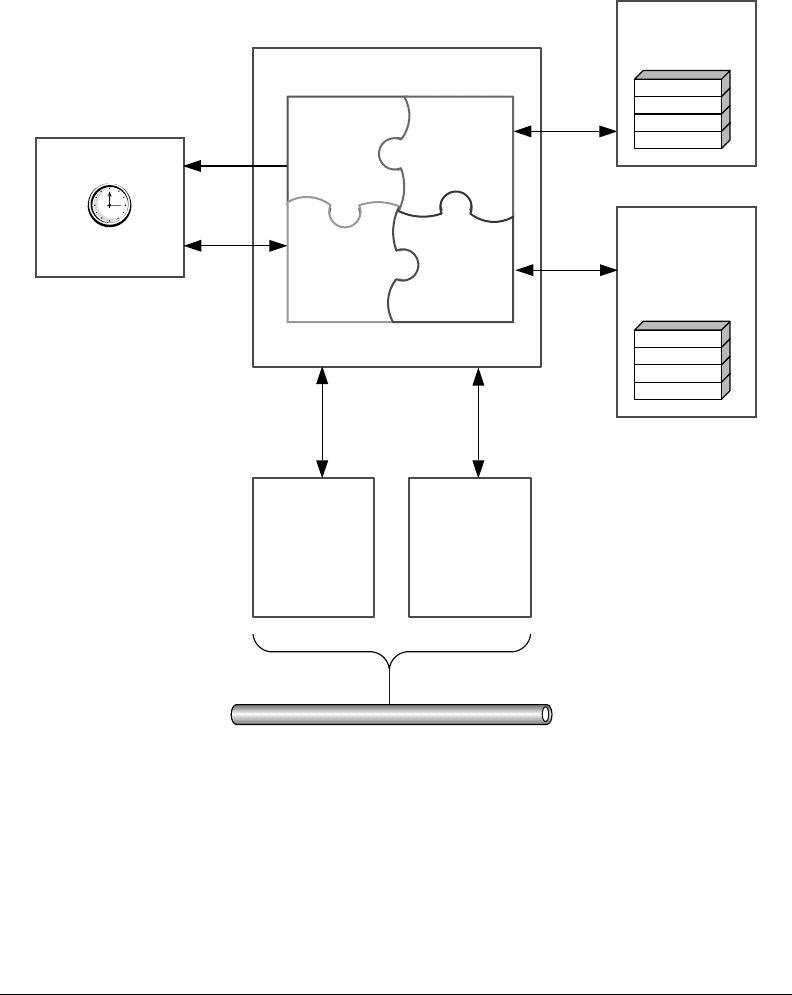

split.into.a.port-specic.part.and.general.information.about.the.clock..Finally,.the.protocol.engine.has.

access.to.the.timekeeping.part—the.clock.itself..A.clock.in.IEEE.1588.can.be.adjusted.and.read.out.by.

the.protocol.engine.

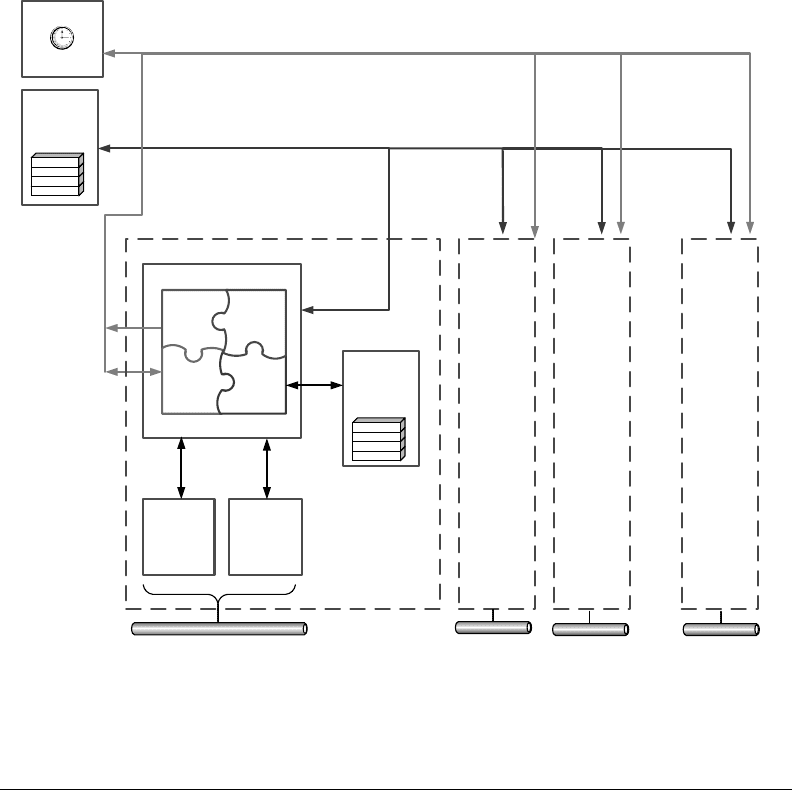

18.6 Boundary Clocks

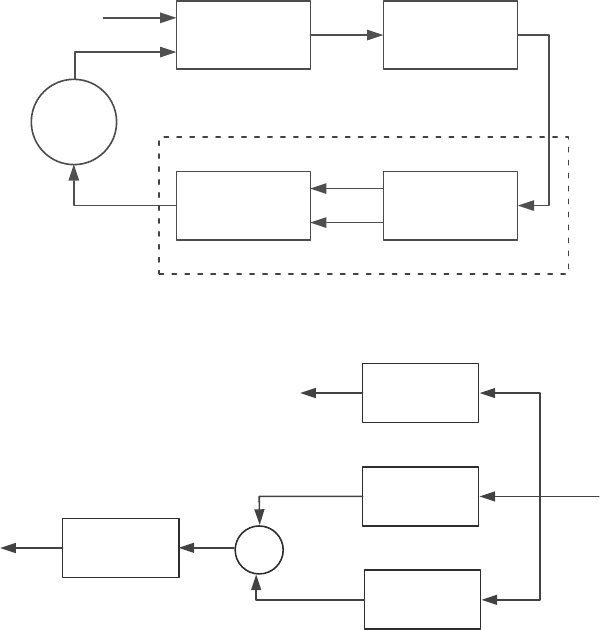

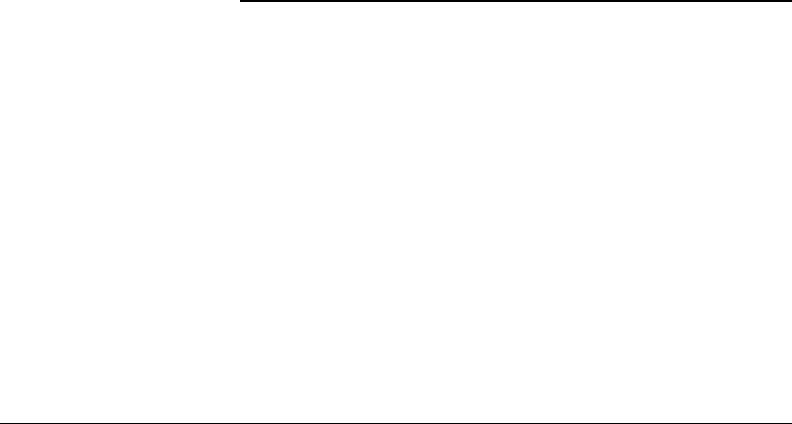

It.is.easy.to.broaden.the.concept.shown.for.the.ordinary.clocks.by.simply.duplicating.the.PTP.ports,.

each.having.access.to.a.common.clock.data.set.and.sharing.the.clock..In.order.to.implement.this.

communication.in.terms.of.intra-node.time.exchange.between.the.PTP.ports,.ordinary.clock.data.

sets.are.needed..e.IEEE.1588.standard.calls.these.generalized.clocks.boundary clocks..A.model.

for.a.boundary.clock.with.a.general.number.of.n.ports.is.shown.in.Figure.18.4..It.has.to.be.noted.

that.only.one.port.may.act.as.master.node,.which.implies.that.the.local.clock.will.only.be.set.by.one.

instance.

Node clock

Protocol engine

Event port

Port

configuration

data and foreign

master data

PTP communication path

Clock

correction

Message

assembling

Configuration

storage

Protocol state

engine

General

port

Timestamped

message receipt

and

transmission

Message receipt

and

transmission w/o

timestamping

Ordinary clock

data sets

FIGURE 18.3 Model.of.an.ordinary.PTP.clock.(ModelOrdinaryPTPClock.pdf).

© 2011 by Taylor and Francis Group, LLC

Clock Synchronization in Distributed Systems 18-5

18.7 Precision time Protocol, IEEE 1588–2008 (PtPv2)

Version.1.of.IEEE.1588.was.kept.as.simple.as.possible,.but.growing.industrial.interest.in.precision.clock.

synchronization.soon.made.clear.that.an.improved.version.of.the.standard.was.needed..By.the.time.

of.writing,.the.second.ballot.on.IEEE.1588v2.has.started.and.the.nal.publication.of.the.standard.is.

expected.to.be.in.the.second.half.of.2008..e.new.version.of.the.standard.will.have.several.improve-

ments

.[IEEE.1588v2]:

•

. Mappings..As.the.main.clauses.of.the.standard.specify.a.communication.protocol,.rather.then.

actual.payload.positions.in.packets,.mappings.to.communication.protocols.such.as.IP.have.to.be.

made..As.an.improvement.to.version.1,.additional.mappings.such.as.to.UDP.in.IPv4.and.IPv6,.

DeviceNet,.raw.Ethernet,.PROFINET,.and.ControlNet.will.be.made.

•

. Type length value elds..Version.1.suered.from.the.problem.that.formally,.messages.could.

not.be.extended.with.arbitrary.information..Such.extensions.have.been.added.via.partly.user-

denable

.type.length.value.(TLV).elds..Nevertheless,.not.only.proprietary.elds.are.dened.

via.TLVs..Also,.standardized.functionality,.like.security.updates,.is.transported.via.these.elds.

•

. Transparent clocks..Under.the.name.“on-the-y.timestamping”.[Gaderer2004],.version.2.supports.

transparent.clocks,.which.are.basic.network.elements.that.timestamp.messages.when.entering.

Node clock

Protocol engine

Event port

Port

configuration

data and

foreign

master data

PTP communication path

(Technology 1)

Clock

correction

Message

assembling

Configuration

storage

Protocol state

engine

General

port

Timestamped

message receipt and

transmission

Message receipt and

transmission w/o

timestamping

Ordinary

clock

data sets

Port 1

…

Port 3Port 2

Port n

(Technology 2)

(Technology n)

(Technology 3)

FIGURE 18.4 Model.of.a.PTP.boundary.clock.(PTPBoundaryClock.pdf).

© 2011 by Taylor and Francis Group, LLC

18-6 Industrial Communication Systems

and.exiting,.thus,.enabling.a.system.to.calculate.the.processing.time.of.a.packet.in.devices..is.is.

requ

ired

.for.swit

ches,

.whic

h

.do.not.have.a.pred

ictable

.forw

arding

.for.pack

ets

.or.in.ring.and.line.

stru

ctures

.as.impl

emented

.in.PROF

INET.

.is.addi

tion

.was.intr

oduced

.when.it.turn

ed

.out.that.

the.conc

ept

.of.boun

dary

.cloc

ks

.of.versi

on

.1.sue

rs

.from.dic

ulties

.caus

ed

.by.casc

aded

.cont

rol

.

loop

s,

.whi

ch

.may.exh

ibit

.sta

bility

.pro

blems

.ae

r

.sev

eral

.hop

s.

•

. In.prin

ciple,

.the.sync

hronization

.accur

acy

.with.IEEE.1588

v2

.can.get.bett

er

.than.1.ns..Comp

ared

.to.

vers

ion

.1,.this.was.made.poss

ible

.by.the.incr

eased

.leng

th

.of.sever

al

.eld

s

.in.the.prot

ocol

.allo

wing

.for.

a.high

er

.resol

ution

.of.para

meters

.and.time

stamps.

.is.exte

nsion

.reect

s

.the.incr

eased

.dema

nd

.for.

accur

acy

.in.cloc

k

.sync

hronization.

.Rela

ted

.to.it.and,.amon

g

.othe

rs,

.moti

vated

.by.telec

om

.appl

ica-

tions

.is.the.incr

eased

.sync

hronization

.rate.of.the.new.vers

ion.

.Fina

lly,

.eld

s

.to.comp

ensate

.asym

-

metry

.have.been.incl

uded,

.whic

h

.can.be.used.to.comp

ensate

.inhe

rently,

.die

rent

.dela

ys

.for.send.

and.recei

ve

.chan

nels.

.Howe

ver,

.also.meas

ures

.outs

ide

.of.the.scope.of.the.prot

ocol

.can.be.made.(e.g.

,

.

usag

e

.of.cali

brated

.cabl

es

.or.know

ledge

.of.the.chan

nel

.as.it.is.the.case.in.powe

rline).

•

. Opti

onal support of unicast messages.

.Gene

rally

.spea

king,

.IEEE.1588.assu

mes

.that.one.mast

er

.is.

elec

ted

.and.via.that.mast

er

.seve

ral

.slav

es

.are.sync

hronized.

.Of.cour

se,

.one.woul

d

.take

,

.if.avai

l-

able,

.mult

icast

.mess

ages

.for.sync

hronization,

.as.the.time.to.be.dist

ributed

.is.the.same.for.all.

node

s

.atta

ched

.to.this.mast

er.

.Howe

ver,

.in.some.case

s,

.for.exam

ple,

.if.the.comm

unication

.tech

-

nology

.does.not.supp

ort

.mult

icast

.or.die

rent

.time

scales

.need.to.be.used

,

.unic

ast

.is.need

ed.

.is.

will.be.pos

sible

.in.ver

sion

.2.

•

. Proles..Within.the.scope.of.standardization,.proles.are.in.general.needed.to.apply.a.special,.

reduc

ed

.set.of.value

s

.and.rang

es

.to.a.more.gene

ral

.stan

dard

.in.orde

r

.to.appl

y

.it.for.a.speci

al

.use.case..

In.the.case.of.IEEE.1588

,

.pro

les

.are.needed.in.orde

r

.to.reect.the.grow

ing

.numb

er

.of.appl

ication

.

area

s.

.For.exam

ple,

.in.the.new.vers

ion,

.a.speci

al

.pro

le

.for.telec

om

.appl

ications,

.PROF

INET,

.etc.

,

.

can.be.den

ed.

.For.all.value

s

.not.den

ed

.in.a.speci

c

.pro

le,

.the.defa

ult

.value

s

.of.the.stan

dard

.appl

y.

•

. Alte

rnative best master clock algorithms.

.Espe

cially,

.the.tele

com

.indu

stry

.dema

nds

.long.hold

over

.

time

s

.aer.a.mast

er

.fail

ure.

.is.is.ree

cted

.by.the.possi

bility

.for.alte

rnate

.best.mast

er

.cloc

k

.

(BMC

)

.alg

orithms.

•

. Expe

rimental specications.

.As.it.can.alre

ady

.be.pred

icted

.that.new.feat

ures

.such.as.secu

rity

.

(whi

ch

.is.curr

ently

.not.supp

orted

.at.all).or.cumu

lative

.freq

uency

.ose

ts

.to.the.mast

er

.are.need

ed,

.

some.expe

rimental,

.non-

normative

.clau

ses

.have.been.adde

d.

.For.some.of.thos

e

.clau

ses,

.furt

her

.

rese

arch

.and.case.stud

ies

.are.need

ed;

.howe

ver,

.the.expe

rimental

.anne

x

.ease

s

.the.star

t

.for.such.

inve

stigations

.[Tr

eytl2007,Gaderer2006a].

18.8 Network time Protocol

With.the.introduction.of.distributed.applications.in.the.Internet,.a.new.requirement.arose:.the.synchro-

nization

.betw

een

.the.part

icipating

.comp

uters.

.For.exam

ple,

.simpl

e

.appl

ications

.like.the.sync

hroniza-

tion

.of.les.on.two.serv

ers,

.like.the.well

-known

.rsyn

c

.appl

ication,

.use.time

stamps

.of.les.to.dist

inguish

.

betw

een

.olde

r

.and.newe

r.

.is.prob

lem

.was.solv

ed

.with.the.prob

ably

.olde

st

.appl

ication

.laye

r

.proto

col

.

of.the.Inte

rnet

.stil

l

.in.use:.e.netw

ork

.time.proto

col

.(NTP

).

.e.open.proto

col

.stan

dard

.NTP.is.a.

spec

ication

.for.a.TCP/

IP-based

.cloc

k

.sync

hronization

.sche

me

.for.netw

ork

.devi

ces.

.e.main.work.on.

NTP.was.cont

ributed

.by.Davi

d

.L..Mill

s.

.e.stan

dardization

.was.done.via.requ

est

.for.comm

ent

.(RFC

)

.

docu

ments—the

.key.cont

ribution

.can.be.foun

d

.in.[Mil

ls1991a].

.NTP.is.a.very.care

fully

.desig

ned

.proto

-

col

.almo

st

.to.ever

y

.exte

nt

.inve

stigated.

.It.cove

rs,

.in.oppo

site

.to.IEEE.1588

,

.all.aspe

cts

.like.the.cont

rol

.of.

the.cloc

k

.and.resp

ective

.filt

er

.algo

rithms

.[Gur

ewitz2003,Mills1998b,Mills1998a]

.with.a.wide.rang

e

.

of.app

lication

.stu

dies

.[Ri

chards2006].

e

.late

st

.versi

on

.of.NTP.is.4;.neve

rtheless,

.in.the.mean

while,

.a.simpl

ied

.versi

on

.call

ed

.SNTP.has.

been.spe

cied

.and.is.in.use

.

© 2011 by Taylor and Francis Group, LLC

Clock Synchronization in Distributed Systems 18-7

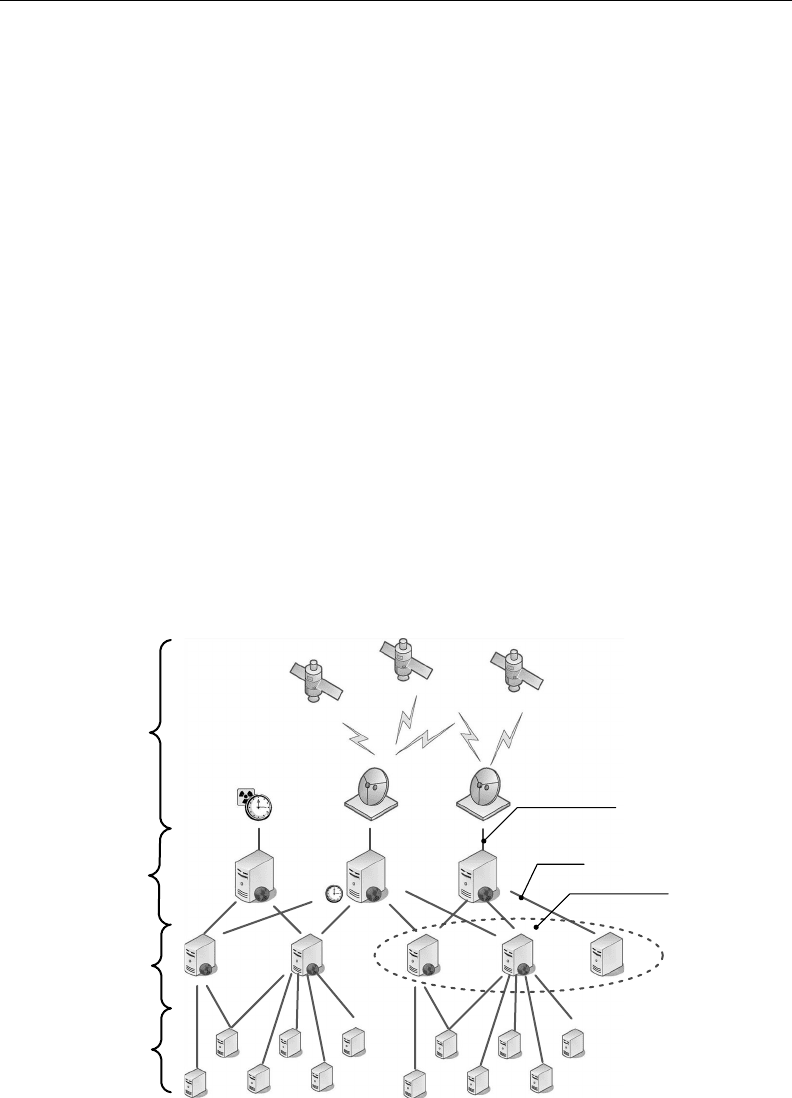

18.9 Network time Protocol Strata

A.basic.principle.in.NTP.is.to.assign.to.every.clock.a.so-called.stratum..is.hierarchically.organized.

system.of.clock.strata.denes.the.accuracy.of.a.computer’s.clock.or.more.precisely.the.distance.to.a.ref-

erence

.clock..Within.NTP,.device.strata.are.identied.with.an.integer.value.starting.at.stratum-0..Like.

illustrated.in.Figure.18.5,.these.strata.are.dened.as.follows:

•

. Stratum-0.devices.have.highly.accurate.clocks.such.as.cesium.or.rubidium.time.normals..It.

has.to.be.noted.that.devices.with.this.stratum.are.never.connected.directly.to.a.network—

time

.and.frequency.transfer.happens.via.serial.interfaces.or.transmission.of.defined.electrical.

pulses.

•

. Stratum-1.nodes.are.always.directly.connected.to.devices.with.stratum-0..e.usual.way.is.to.have.

these.nodes.act.as.time.servers.for.stratum-2.clients.

•

. Stratum-2.nodes.communicate.via.NTP.with.stratum-1.servers..It.is.possible.for.these.devices.to.

peer.with.other.stratum-2.nodes.in.order.to.obtain.a.more.robust.time.source.for.all.other.devices.

in.the.so-called.peer group..Again,.in.the.usual.case,.these.devices.will.act.as.servers.for.stratum-3.

clocks.

•

. Stratum-3.is.the.class.for.the.next.hierarchical.layer.in.NTP..ese.nodes.perform.basically.the.

same.tasks.as.NTP.devices.in.the.layer.below,.with.the.dierence.that.time.is.obtained.from.

stratum-2.devices..In.general,.NTP,.depending.on.the.version,.allows.strata.higher.than.stratum-3.

(up.to.256.depending.on.the.version)..Nevertheless,.future.developments.will.most.likely.restrict.

the.NTP.strata.to.8–16.

A

.study.by.Minar.in.1999.[Minar1999].revealed.that.at.the.time.of.the.study,.at.least.175,000.hosts.use.

NTP.in.the.Internet..Among.those.are.more.then.300.stratum-1.servers.and.20,000.and.80,000.stratum-2.

and.stratum-3.servers,.respectively.

Stratum-0

Stratum-2

Stratum-1

Stratum-2 peer group

for increased accuracy

Direct link

e.g., RS232

NTP link

Stratum-3

FIGURE 18.5 Example.for.an.NTP.network.with.node.strata.(NTPStratums.pdf).

© 2011 by Taylor and Francis Group, LLC

18-8 Industrial Communication Systems

18.10 architecture, Protocol, and algorithms

e.idea.behind.the.NTP.is.to.distribute.a.common.notion.of.time.among.all.nodes.of.a.network.in.

terms.of.a.reference.clock..is.goal.can.be.achieved.in.quite.dierent.strategies:

•

. Minimization.of.clock oset,.which.tries.to.minimize.the.sampled.dierence.between.the.local.

and.the.reference.time.

•

. Alignment.of.the.frequency..is.is.equal.to.the.rst.strategy,.with.the.exception.that.the.absolute.o-

set

.of.periodically.generated.clock.signals.is.not.considered,.but.the.stability.of.the.oset.optimized.

•

. e.alignment.of.the.absolute.clock.value.in.terms.of.minimizing.clock.oset.and.optimizing.the.

dierence.between.all.nodes..is.criterion.is.equal.to.internal.clock.synchronization.(alignment.

of.all.nodes.of.a.network.with.no.respect.to.the.absolute.time.scale),.with.the.exception.that.NTP.

inherently.assumes.an.alignment.to.an.absolute.correct.time.source.of.the.overall.master.

18.11 NtP Clock Synchronization Hardware requirements

Like.any.other.clock.synchronization.system,.NTP.has.to.make.certain.assumptions.regarding.the.clocks..

As.NTP.aims.to.synchronize.hosts.within.the.Internet,.one.assumption.is.that.the.architecture.of.every.

node.is.similar.to.a.clock.in.a.PC..One.further.assumption.of.NTP.is.that.a.network.node.does.not.neces-

sarily

.need.to.be.powered.up.all.time..However,.this.requires.keeping.up.with.the.unstoppable.progress.of.

time.even.during.power.down..In.practice,.this.is.usually.done.with.a.so-called.real-time.clock.(RTC)..is.

clock.is.battery-powered.and.thus,.running.also.during.power-down.times..For.cost.and.energy.eciency.

reasons,.these.clocks.are.usually.equipped.with.32,768.kHz.crystals..is.frequency.is.very.convenient,.

since.32,768.transitions.can.be.represented.as.2

15

,.which.means.that.a.15.bit.counter.can.be.used.without.

further.fractional.parts.to.represent.1.s..In.common.PC.architectures,.the.content.of.this.clock.is.loaded.

during.boot-up.into.a.tick.register..Usual.clock.registers.for.NTP.are.48.bit.wide,.and.updated.by.adding.

the.32.bit.wide.clock-adjust.register,.with.an.interrupt.typically.scheduled.every.1–20.ms..e.content.is.

also.called.processor.cycle.counter.(PCC)..As.these.registers.are.updated.by.means.of.soware.routines.

and.without.the.possibility.to.schedule.future.updates.(such.as.provided.in.high.precision.clocks.like.in.

SynUTC),.writing.to.these.registers.has.to.be.done.with.high.priority.[Mills1998a]..Additionally,.the.16.bit.

wide.dri-compensation.register.is.used.to.compensate.the.frequency.oset.of.the.processor.clock.

18.12 Synchronization algorithms of NtP

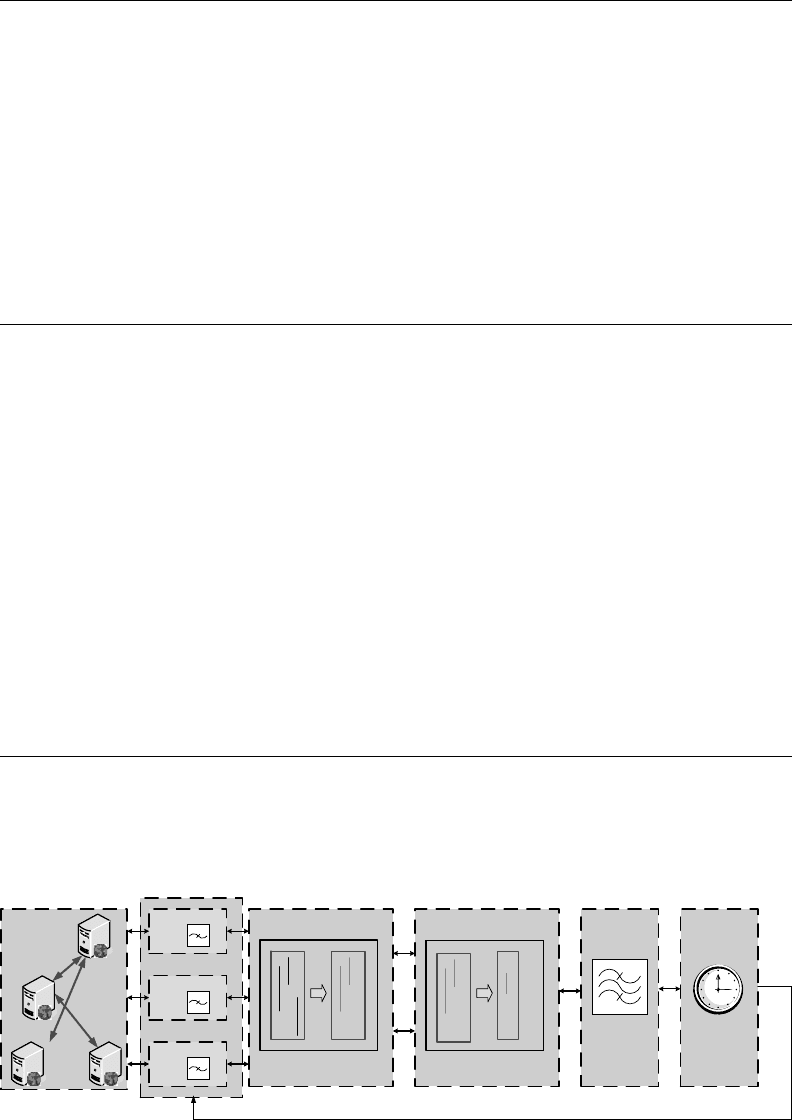

Figure.18.6.shows.the.ve.components.of.the.NTP:

•

. e.data lter.is.instantiated.on.the.client.side.for.every.server..e.main.task.of.this.unit.is.to.

calculate.the.delay.through.round-trip.measurements.and.adjust.the.contents.of.each.message.

accordingly.

Network

Data filter

Peer selection

Clock combining Loop filter

Adjustable

clock

Data filter

Data filter

FIGURE 18.6 System.concept.of.a.typical.NTP.node.(NTPSystemConcept.pdf).

© 2011 by Taylor and Francis Group, LLC

Clock Synchronization in Distributed Systems 18-9

•. e.second.component.in.the.data.ow.is.the.so-called.peer selection..is.unit.is.included.due.to.

the.fac

t

.tha

t

.not.onl

y

.del

ayed

.mes

sages

.can.arr

ive

.fro

m

.a.nod

e,

.but.als

o

.mut

ually

.wro

ng

.clo

cks

.

can.pre

sent

.the

mselves

.as.mas

ters.

.Rea

sons

.for.wro

ng

.hos

ts

.in.NTP.net

works

.can.be.bro

ken

.

ser

ver

.clo

cks

.or.att

acks

.wit

h

.the.goa

l

.to.cha

nge

.the.tim

e

.on.a.net

work

.hos

t.

.e.lat

ter

.can.be.

tac

kled

.by.aut

hentication

.of.clo

ck

.ser

vers,

.whi

ch

.is.nev

ertheless

.not.su

cient

.for.the.rs

t

.iss

ue

.

of.acc

identally

.wro

ng

.clo

cks.

.In.ord

er

.to.avo

id

.pro

blems

.res

ulting

.fro

m

.suc

h

.bro

ken

.clo

cks,

.a.

par

ameter-driven

.de

cision

.of.so

rting

.ou

t

.th

ose

.cl

ocks

.is.do

ne

.in.pe

er

.se

lection.

•

. Ae

r

.the.pee

r

.sel

ection

.is.don

e—from

.a.mes

sage

.poi

nt

.of.vie

w—oen

.con

tradicting

.inf

ormation

.

reg

arding

.the.os

et

.and.dri

.of.the.loc

al

.clo

ck

.exi

st.

.es

e

.dat

a

.hav

e

.to.be.mer

ged

.in.the.clo

ck

combining

.co

mponent.

•

. e.las

t

.two.com

ponents,

.nam

ely

.the.loo

p lter

.and.vol

tage-controlled oscillator

.(VC

O),

.hav

e

.the.

tas

k

.of.con

ditioning

.the.con

trol

.sign

al

.wit

h

.res

pect

.to.con

trol

.cir

cuit

.sta

bility

.and.adj

usting

.the.

loc

al

.cl

ock,

.re

spectively.

e

.rs

t

.ele

ment

.of.the.NTP.sign

al

.ow.is.the.dat

a

.lt

er.

.is.ele

ment

.is.pro

vided

.to.eli

minate

.sta

-

tistical

.err

ors

.as.wel

l

.as.byz

antine

.nod

es.

.e.lt

er

.col

lects

.dat

a

.on.a.per

-peer

.basi

s

.and.cal

culates

.two.

mea

sures:

.the.lt

er dispersion

.ε

σ

,.and.the.select dispersion.ε

ζ

..e.dispersion.is.calculated.with.ϑ

i

(0.≤.i.≤.n).

as.the.os

et

.of.the.ith.sam

ple

.and.the.sam

ple

.di

erence

.ε

ij

.=.|ϑ

i

.−.ϑ

j

|..e.dispersion,.ε

j

.is.then.dened.

rel

ative

.to.th

e

.jth.en

try

.as.we

ighted

.su

m

.

ε ε

j ij

i

i

n

w=

+

=

−

∑

1

1

1

Both.ε

σ

.and.ε

ζ

.are.dened.by.protocol.parameters,.namely.NTP.FILTER.and.NTP.SELECT,.which.

are.usu

ally

.set.to.val

ues

.les

s

.tha

n

.0.5.and.eva

luated

.rel

ative

.to.the.rs

t

.ent

ry

.ε

0

..In.that.context,.w.

is.the.wei

ghting

.fac

tor,

.whi

ch

.is.use

d

.to.bui

ld

.an.exp

onential

.ave

rage,

.wit

h

.a.val

ue

.of.w.<.0.5

.

.e.

sec

ond,

.fun

ctional

.par

t,

.the.pee

r

.sel

ection

.is.mos

t

.imp

ortant

.for.the.sta

bility

.of.NTP

.

.As.soo

n

.as.new.

os

ets

.to.a.ref

erence

.clo

ck

.are.est

imated,

.thi

s

.alg

orithm

.dec

ides

.whi

ch

.pee

r

.is.use

d

.as.syn

chroniza-

tion

.sou

rce.

.Of.cou

rse,

.als

o

.the.una

vailability

.of.os

et

.mea

surements

.(e.

g.,

.due.to.tim

eouts)

.are.als

o

.

use

d

.to.(de

-)select

.pee

rs.

.e.act

ual

.pee

r

.sel

ection

.is.don

e

.by.ass

embling

.of.the.can

didates

.in.a.sor

ted

.

lis

t.

.is.lis

t

.rep

resents

.the.ava

ilable

.pee

rs

.sor

ted

.by.str

atum

.and.syn

chronization

.dis

persion.

.Als

o,

.

sev

eral

.san

ity

.che

cks

.to.det

ect

.def

ective

.nod

es

.are.a.kno

ck-out

.cri

terion

.to.rem

ove

.def

ective

.nod

es.

.In.

cas

e

.tha

t

.the.res

ult

.of.thi

s

.san

ity

.che

ck

.is.an.emp

ty

.lis

t,

.the.loc

al

.nod

es

.con

tinue

.run

ning

.wit

h

.the

ir

.

loc

al

.una

djusted

.clo

ck

.fre

quencies.

.In.the.oth

er

.cas

e,

.if.the.lis

t

.hol

ds

.mor

e

.tha

n

.one.nod

e,

.the

se

.sta

tis-

tical

.equ

ivalent

.os

ets

.hav

e

.to.be.com

bined.

.e.clo

ck

.ass

embly

.is.don

e

.by.con

struction

.of.so-

called

.

na

l

.clo

ck

.cor

rection,

.η

n

,.for.all.nodes..Moreover,.the.synchronization.distance,.λ

n

,.is.also.internally.

req

uired

.by.the.pre

viously

.des

cribed

.alg

orithms.

.e.val

ue

.of.1/λ

n

.is.then.used.as.weight.of.each.clock.

os

et

.in.the.lis

t.

e

.vir

tual

.con

trol

.loo

p

.is.na

lly

.clo

sed

.by.the.loo

p

.lt

er

.and.the.VCO

,

.res

pectively.

.e.tas

k

.of.the

se

.

two.par

ts

.is.to.ada

pt

.the.cal

culated

.set

tings

.fro

m

.NTP.to.the.act

ual

.clo

ck

.of.the.dev

ice.

.is.is.don

e

.by.

adj

usting

.os

et

.and.fre

quency—both

.alg

orithms

.are.imp

lemented

.in.a.fee

dback

.loo

p.

.e.gen

eral

.str

uc-

ture

.of.the.dis

ciplining

.is.sho

wn

.in.Fig

ure

.18.

7.

.In.gen

eral,

.thi

s

.dis

ciplining

.str

ucture

.is.a.sub

ordinate

.

con

trol

.loo

p.

.e.set.val

ue

.ϑ

r

.is.taken.from.the.above-described.clock.selection.part.of.NTP..e.value.is.

com

pared

.to.the.con

trol

.pha

se

.of.the.var

iable

.fre

quency

.osc

illator,

.whi

ch

.is.the.act

ual

.dri

ver

.of.the.nod

e

.

clo

ck.

.e.di

erence

.bet

ween

.ϑ

r

.and.ϑ

c

.is.aerward.used.in.the.clock.lter,.which.is.actually.a.tapped.

del

ay

.li

ne,

.wh

ereas

.th

e

.ta

p

.is.se

lected

.by.an.al

gorithm

.de

scribed

.in.[M

ills2000].

Aerward,

.the.lt

ered

.sign

al

.is.use

d

.in.the.loo

p

.lt

er

.(Fi

gure

.18.

7).

.is.lt

er

.adj

usts

.the.clo

ck

.via.the.

cal

culation

.of.thr

ee

.vari

ables.

.Fir

st,

.the.pha

se

.ose

t

.is.cal

culated

.and.dir

ectly

.fed.bac

k

.to.the.clo

ck

.adj

ust-

ment

.uni

t.

.Seco

nd,

.the.fre

quency

.ose

t

.is.cal

culated

.via.two.way

s:

.a.pha

se

.pred

iction

.and.a.fre

quency

.

© 2011 by Taylor and Francis Group, LLC

18-10 Industrial Communication Systems

prediction.(Figure.18.8)..e.phase-locked.loop.(PLL).predicts.a.frequency.oset.as.integral.of.V

S

τ,.whereas.

the.frequency-locked.loop.(FLL).use.an.exponential.average.of.V

S

/τ..ese.two.values.are.combined.via.a.

simple.summarization..It.has.to.be.specically.noted.that.the.averaging.interval.of.these.two.components.is.

chosen.with.respect.to.the.Allan-intercept,.in.order.to.gain.an.optimal.behavior.of.the.structure.

references

[Anceaume1997].Anceaume,.E..and.Puaut,.I.A.,.Taxonomy.of.clock.synchronization.algorithms,.Campus

Universitaire de Beaulieu,

.Rennes.Cedex,.France,.1997,.25.pp.

[Brennan2005]

. Brennan,. R.W.,. Christensen,. J.H.,. Gruver,. W.A.,. Kotak,. D.B.,. Norrie,. D.H.,. and. van.

Leeuwen,.E.H.,.Holonic.manufacturing.systems:.A.technical.overview,.in.e Industrial Information

Technology Handbook,

. Part. II. (Industrial. Information. Technology),. Section. 7. (Integration.

Technologies),.Chapter.106,.CRC.Press,.Boca.Raton,.FL,.2005,.106-1–106-15.

[Eidson2005]

.Eidson,.J..C.,.e.application.of.IEEE.1588.to.test.&.measurement.systems,.White.Paper.

Agilent,.Agilent.Laboratories,.Palo.Alto,.CA,.December.2005,.pp..9–13.

[Eidson2006]

. Eidson,. J.C.,. Measurement, Control, and Communication Using IEEE 1588,. Springer,.

London,.U.K.,.2006.

[Gaderer2004]

.Gaderer,.G..and.Sauter,.T.,.Strategies.for.clock.synchronization.in.powerline.networks,.in.

Proceedings of the 3rd International Workshop on Real-Time Networks in Conjunction with the 16th

Euromicro International Conference on Real-Time Systems,

.Catania,.Italy,.2004.

Phase

detector

Clock adjust

Predictor

Clock filter

VFO

NTP

Loop filter

y

x

V

d

V

S

V

c

θ

C

θ

R

FIGURE 18.7 NTP. clock. discipline. (NTPClockDiscipline.pdf).. (Redrawn. from. Mills,. D.,. IEEE/ACM Trans.

Netw.,

.6(5),.505,.1998.)

FLL predict

Frequency

PLL predict

Phase

correct

y

x

V

S

y

adj

y

PLL

y

FLL

Σ

FIGURE 18.8 NTP.phase.and.frequency.prediction.functions.(NTPPredictionFunctions.pdf)..(Redrawn.from.

Mills,.D.,.IEEE/ACM Trans. Netw.,.6(5),.505,.1998.)

© 2011 by Taylor and Francis Group, LLC

Clock Synchronization in Distributed Systems 18-11

[Gaderer2006a].Gaderer,.G.,.Treytl,.A.,.and.Sauter,.T.,.Security.aspects.for.IEEE.1588.based.clock.synchro-

nization

.pro

tocols,

.in.Pro

ceedings of the IEEE International Workshop on Factory Communication

Systems,

.Tur

in,

.It

aly,

.Jun

e

.27,.2006,.pp

.

.247–250.

[Gur

ewitz2003]

.Gure

witz,

.O.,.Cidom,.I.,.and.Sidi,.M.,.Netw

ork

.time.sync

hronization

.using.cloc

k

.oset.

opt

imization,

.in.Pro

ceedings of the 2003 International Conference on Network Protocols,

.Atl

anta,

.GA,.

Nov

ember

.4–7,.2003,.pp

.

.212–221.

[Ha

nsson2005]

.Han

sson,

.H.,.Nolin,.M.,.and.Nol

te,

.T.,.Rea

l-time

.system

s,

.Sec

tion

.6.(Rea

l-time

.embe

d-

ded

.system

s),

.in.e I

ndustrial Information Technology Handbook,

.Par

t

.II.(Ind

ustrial

.Info

rmation

.

Tec

hnology),

.Sec

tion

.6.(Rea

l-Time

.Embe

dded

.Syst

ems),

.Cha

pter

.81,.CRC.Pres

s,

.Boc

a

.Rat

on,

.FL,.

2005,.81-1–81-28.

[IEEE1588v1]

.Arl

t,

.V.,.John

son,

.R.,.Lee

,

.K.,.Munz,.H.,.Pow

ers,

.E.,.Read

,

.J.,.and.Schmid

t,

.R.,.IEEE.Sta

ndard

.

for.a.Pre

cision

.Cloc

k

.Syn

chronization

.Pro

tocol

.for.Netw

orked

.Mea

surement

.and.Con

trol

.Syst

ems

.

TC9,.Tec

hnical

.Commi

ttee

.on.Sens

or

.Tec

hnology

.of.the.IEEE.Ins

trumentation

.and.Mea

surement

.

Societ

y.

[IEEE1588v2]

.McK

ay,

.J..(ed

.),

.IEEE 1588 (tm) 2.1 S

tandard for a Precision Clock Synchronization Protocol

for Networked Measurement and Control Systems,

.Ins

titute

.of.Elec

trical

.and.Elec

tronics

.Engin

eers,

.

Inc.,.Ne

w

.Yo

rk,

.2006.

[Ko

petz1987]

.Kop

etz,

.H..and.Och

senreiter,

.W.,.Cloc

k

.sync

hronization

.in.dist

ributed

.rea

l-time

.system

s,

.

IEEE Tra

nsactions on Computers,

.C-36(8),.Augu

st

.1987,.933–940.

[La

mport1978]. Lamport,. L.,. Time,. clocks,. and. the. ordering. of. events. in. a. distributed. system,.

Com

munications of the ACM,

.1978,.21,.558–565.

[Li

skov]

.Lis

kov,

.B.,.Pract

ical

.uses.of.sync

hronized

.cloc

ks

.in.dist

ributed

.system

s,

.Dis

tributed Computing,

.

1993,.6,.211–219.

[Mi

lls1991a]

.Mil

ls,

.D.L.,.Int

ernet

.time.sync

hronization:

.e.netw

ork

.time.pro

tocol,

.IEEE Tr

ansactions on

Communications,

.1991,.39,.1482–1493.

[Mi

lls1998a]

.Mil

ls,

.D.,.RFC.1059:.Netw

ork

.Time.Pro

tocol

.(Versio

n

.1),.Univ

ersity

.of.Del

aware,

.Newa

rk,

.

DE,.1998.

[Mi

lls1998b]

.Mil

ls,

.D.,.Ada

ptive

.hyb

rid

.cloc

k

.disci

pline

.algo

rithm

.for.the.netw

ork

.time.pro

tocol,

.IEEE/

ACM Tr

ansactions on Networking,

.1998,.6(5),.505–514.

[Mi

lls2000]

.Mil

ls,

.D.,.RFC.1119:.Netw

ork

.Time.Pro

tocol

.(Versio

n

.2),.Univ

ersity

.of.Del

aware,

.Newa

rk,

.

DE,.2000.

[Min

ar1999]

.Mina

r,

.N.,.A.Surv

ey

.of.the.NTP.Netw

ork,

.Tec

hnical

.Repo

rt,

.Mas

sachusetts

.Ins

titute

.of.

Tec

hnology,

.Ca

mbridge,

.MA,.1999.

[Ow

en2005]

.Owen,.D.,.Wire

d

.trig

ger

.bus.physic

al

.asp

ects

.2005,.Whit

e

.Pap

er

.Agi

lent,

.Agi

lent

.Lab

oratories,

.

Palo.Al

to,

.CA,.2005.

[Pa

lumbo1992]

.Pal

umbo,

.D.L.,.e.deriva

tion

.and.experim

ental

.veric

ation

.of.cloc

k

.sync

hronization

.

the

ory,

.IEEE Tr

ansactions on Computers,

.1992,.43,.676–686.

[Pa

tt1994]

.Pat

t,

.B.,.A.the

ory

.of.cloc

k

.sync

hronization,

.PhD.thesi

s,

.Mas

sachusetts

.Ins

titute

.of.Tec

hnology,

.

Cam

bridge,

.MA,.1994.

[Ple

asant2005]

.Plea

sant,

.D.,.LXI.trig

gering,

.Whit

e

.Pap

er

.Agi

lent,

.Agi

lent

.Lab

oratories,

.Palo.Alt

o,

.CA,.

2005.

[Rich

ards2006]

.Rich

ards,

.J.M.,.Man

dell,

.D.E.,.Maka

rand

.Kara

njkar,

.P.,.and.Pierr

e-Anthony,

.S.,.Fra

me

Synchronization in a Ethernet NTP Time-Keeping Digital Cinema Playback System,

.Dol

by

.Lab

oratories

.

Licensin

g

.Co

rporation,

.San.Fra

ncisco,

.CA,.2006.

[Sau

ter2005]

.Saut

er,

.T.,.Link

ing

.facto

ry

.oor.and.the.inter

net,

.in.e I

ndustrial Information Technology

Handbook,

. Par

t

. II. (Ind

ustrial

. Info

rmation

. Tec

hnology),

. Sec

tion

. 3. (Ind

ustrial

. Comm

unication

.

Syst

ems),

.Ch

apter

.52,.CRC.Pr

ess,

.Bo

ca

.Ra

ton,

.FL,.2005,.52-1–52-15.

[T

reytl2007]

.Tre

ytl,

.A.,.Gad

erer,

.G.,.Hir

schler,

.B.,.and.Coh

en,

.R.,.Tra

ps

.and.pit

falls

.in.sec

ure

.clo

ck

.syn

chro-

nization,

.in.Pro

ceedings of the IEEE International Symposium on Precision Clock Synchronization for

Measurement, Control and Communication ISPCS 2007,

.Vie

nna,

.Aus

tria,

.Oct

ober

.1–3

,

.200

7,

.pp..18–

24.

© 2011 by Taylor and Francis Group, LLC

19-1

19.1 Introduction

Nowadays,.almost.any.industrial.network.uses.applications.based.on.IP.networks.[1]..is.means.that.

peop

le

.cont

rolling

.thes

e

.netw

orks

.need.to.know.at.leas

t

.the.basic

s

.of.qual

ity

.of.serv

ice

.(QoS

)

.for.IP.net-

w

orks.

.Ever

y

.devi

ce

.used.in.an.indu

strial

.netw

ork

.is.goin

g

.to.send.and.rece

ive

.IP.pack

ets

.but,.depe

nding

.

on.the.natu

re

.of.the.indu

strial

.appl

ication

.we.use.in.the.devi

ce,

.the.way.to.proc

ess

.the.IP.pack

ets

.can.be.

deci

sive

.to.the.objec

tives

.we.want.to.get.thro

ugh

.the.devi

ce.

.e.IP.netw

ork

.is.the.fund

amental

.infr

a-

structure

.for.ever

y

.indu

strial

.netw

ork

.so,.alth

ough

.we.cann

ot

.chan

ge

.the.deta

ils

.of.the.IP.impl

ementa-

tion

.in.the.oper

ating

.syst

ems

.of.the.devi

ces,

.we.need.to.know.how.to.get.the.maxi

mum

.perf

ormance

.

and.reli

ability

.of.our.netw

ork

.for.ever

y

.indu

strial

.appl

ication

.we.deci

de

.to.use..It.is.also.impo

rtant

.to.

note.that.the.devi

ces

.we.can.use.to.mana

ge

.and.impl

ement

.thes

e

.QoS.char

acteristics

.are.not.the.same.

devi

ces

.we.use.to.impl

ement

.our.indu

strial

.appl

ications

.but.the.usua

l

.comm

unication

.devi

ces

.in.ever

y

.

IP.netw

ork—switches

.and.rout

ers.

.It.is.so.possi

ble

.to.say.that.the.QoS.requ

irements

.in.indu

strial

.net-

w

orks

.depe

nd

.on.the.indu

strial

.appl

ications

.we.want.to.use.and,.as.a.cons

equence,

.of.the.comp

lexity

.

of.the.netw

ork.

.If.the.netw

ork

.uses.rout

ers,

.we.can.appl

y

.spec

ial

.feat

ures

.in.the.rout

ers

.to.impr

ove

.our.

QoS;.but.if.the.net

work

.onl

y

.nee

ds

.swi

tches,

.we.can.onl

y

.use.a.res

tricted

.set.of.QoS.fea

tures.

Any

.qual

ied

.netw

ork

.prof

essional

.must.know.the.limi

ts

.for.the.netw

orks

.in.his.or.her.orga

niza-

tion.

.It.is.nece

ssary

.to.know.how.to.get.the.maxi

mum

.of.the.feat

ures

.of.the.netw

ork

.devi

ces

.used

,

.bein

g

.

swit

ches,

.rout

ers,

.or.any.netw

ork

.secu

rity

.elem

ent

.that.can.modi

fy

.the.netw

ork

.perf

ormance,

.as.re-

w

alls

.or.int

rusion

.det

ection

.sys

tems.

Until

.

rece

ntly,

.

ther

e

.

was

.

not

.

much

.

to

.

say

.

abou

t

.

how

.

to

.

impr

ove

.

the

.

serv

ices

.

oer

ed

.

by

.

IP

.

netw

orks.

.

It

.

was.enou

gh

.that.the.netw

ork

.does.its.job.prop

erly

.24.h/da

y.

.But.today

,

.and.in.almo

st

.ever

y

.orga

nization,

.

it.is.nece

ssary

.a.netw

ork

.be.able.to.adapt.the.chan

ging

.need

s

.for.the.die

rent

.kind.of.appl

ications

.using.

it.as.a.mean

s

.of.tran

smission

.and.comm

unication.

.ere.will.be.appl

ications

.that.need.more.band

width

.

19

Quality of Service

19.1. Introduction.....................................................................................19-1

19.2

. Rela

tionship

.wit

h

.Inf

ormation

.Sec

urity

.Top

ics..........................19-3

19.3

. Qual

ity

.of.Ser

vice

.for.IP.Net

works...............................................19-4

Integrated.Services.(IntServ).Model. •. Dierentiated.Services.

(DiServ).Model. •. Classication.and.Marking. •. Queuing.

andCongestion.Management

19.4. Special.Considerations.for.Managing.the.Quality.

ofS

ervice.......................................................................................19-11

Congestion.Avoidance. •. High.Availability.Solutions.for.the.Routers

References................................................................................................... 19-14

Gabriel Diaz Orueta

Spanish University of

Dist

ance

Edu

cation,

UNE

D

Elio San

Cristobal Ruiz

Spanish University of

Dist

ance

Edu

cation,

UNE

D

Nuria Oliva Alonso

Spanish University of

Dist

ance

Edu

cation,

UNE

D

Manuel Castro Gil

Spanish University of

Dist

ance

Edu

cation,

UNE

D

© 2011 by Taylor and Francis Group, LLC

19-2 Industrial Communication Systems

at.specic.moments.and.other.applications.that.impose.no.more.than.a.certain.delay.for.its.signal..

Ift

hese

.con

ditions

.are.not.rea

ched

.simp

ly,

.the.cli

ent

.side.of.the

se

.app

lications

.wil

l

.not.wor

k

.pro

perly

.

and.we.wi

ll

.be.lo

sing

.qu

ality.

Technically

.spe

aking,

.net

work

.QoS.can.be.de

ned

.as.the.app

lication

.of.fun

ctionality

.and.fea

tures

.

to.act

ively

.man

age

.and.sat

isfy

.net

working

.req

uirements

.of.app

lications

.sen

sitive

.to.del

ay,

.los

s,

.or.del

ay

.

var

iation

.(j

itter),

.gu

arantying

.al

so

.th

e

.av

ailability

.of.ba

ndwidth

.fo

r

.cr

itical

.ap

plication

.o

ws.

Using

.Qo

S

.me

thods

.an

d

.te

chnologies

.[2

,3]

.se

veral

.be

nets

.ar

e

.re

ached:

•

. Con

trol over resources:

.It.can.be.det

ermined

.whi

ch

.net

work

.res

ources

.(ba

ndwidth,

.equ

ipment,

.

etc

.)

.are.bei

ng

.use

d.

.For.exa

mple,

.cri

tical

.tra

c

.as.voi

ce

.or.vid

eo

.ove

r

.IP.may.con

sume

.a.lin

k

.and.

QoS.helps.control.the.use.of.the.link.by.dropping.low-priority.packets.

•

. Mor

e ecient use of network resources:

. Usin

g

. net

work

. ana

lysis

.man

agement

. and. acc

ounting

.

tool

s,

.it.can.be.det

ermined

.how.tra

c

.is.han

dled,

.and.whi

ch

.tra

c

.sho

ws

.lat

ency,

.jit

ter,

.or.pac

ket

.

los

s.

.Qo

S

.too

ls

.[1

]

.ca

n

.be.us

ed

.to.tu

ne

.th

e

.ha

ndling

.of.th

e

.tr

ac.

•

. Coe

xistence of critical applications:

.By.usi

ng

.QoS.tec

hnologies,

.it.is.pos

sible

.tha

t

.mos

t

.cri

tical

.

app

lications

.rec

eive

.the.mos

t

.eci

ent

.use.of.the.net

work.

.It.is.pos

sible,

.for.exa

mple,

.tha

t

.tim

e-

.

sen

sitive

.mul

timedia,

.whi

ch

.req

uires

.ban

dwidth

.and.min

imized

.del

ay,

.get.the

m

.whi

le

.oth

er

.app

li-

cations

.in.the.sam

e

.lin

k

.rec

eive

.fai

r

.ser

vice

.wit

hout

.int

erfering

.wit

h

.cri

tical

.app

lications

.tra

c.

ese

.nee

ds

.are.dir

ectly

.lin

ked

.wit

h

.the.ide

a

.of.QoS

,

.see

n

.as.a.sum.of.val

ue

.and.war

ranty,

.bei

ng

.onl

y

.

a.part.of.the.framework.of.services.management.for.best.practices.IT.recommendations,.as.ITIL.or.

Cob

IT[4].

.e.val

ue

.of.the.net

work

.is.wha

t

.we.sea

rch

.usin

g

.a.par

ticular

.net

work,

.the.par

ticular

.com

-

munication

.bet

ween

.di

erent

.kin

d

.of.dev

ices.

.For.the.cas

e

.of.an.ind

ustrial

.net

work,

.the.val

ue

.is.goi

ng

.to.

be.wha

t

.we.wan

t

.to.get.wit

h

.com

munication

.bet

ween

.ser

vers

.and.cli

ents

.in.our.ind

ustrial

.net

work.

.e.

war

ranty

.is.muc

h

.mor

e

.lin

ked

.wit

h

.the.qua

lity,

.mea

ning

.a.de

ned

.set.of.fea

tures

.for.a.con

crete

.net

work

.

and.ca

n

.be.ex

pressed

.as.th

e

.le

vel

.of.se

rvice

.of.th

e

.ne

twork

.fo

r

.a.nu

mber

.of.fe

atures:

•

. Ava

ilability

.or.ho

w

.mu

ch

.ti

me

.is.gu

aranteed

.th

at

.th

e

.ne

twork

.is.up.co

ntinuously

•

. Cap

acity

.or.how.man

y

.res

ources

.(de

dicated

.ban

dwidth,

.del

ay,

.etc

.)

.are.ava

ilable

.for.eac

h

.of.the.

app

lications

.an

d

.ho

w

.is.th

e

.ca

pacity

.to.re

act

.to.a.ch

ange

.in.th

e

.ne

ed

.of.re

sources

•

. Network.security.or.the.ability.to.protect.any.piece.of.information,.following.a.security.policy.

tha

t

.inc

lude

.fac

ts

.lik

e

.the.con

dentiality,

.int

egrity,

.or.aut

hentication

.for.any.kin

d

.of.acc

ess

.eve

nts

.

in.th

e

.ne

twork

•

. Con

tinuity

.as.a.sum.of.the.oth

er

.fea

tures,

.but.spe

cially

.tho

ught

.for.dis

aster

.inc

idents

.suc

h

.as.a.

re.or.a.o

od

Once

.the.net

work

.man

agement

.sta

.has.bui

lt

.a.Net

work

.Pol

icy

.for.all.the

se

.fea

tures,

.it.is.nec

essary

.to.

kno

w

.the.tool

s

.for.imp

lementing

.eac

h

.of.the.dir

ectives

.in.the.pol

icy

.and

,

.for

tunately,

.we.hav

e

.now.rea

l

.

tec

hnical

.so

lutions

.in.pl

ace

.fo

r

.th

ese

.ki

nds

.of.sit

uations,

.an

d

.we.ha

ve

.en

ough

.re

liable

.st

andards.

e

.res

t

.of.thi

s

.cha

pter

.pre

sents

.an.int

roduction

.on.how.to.man

age

.all.the

se

.fea

tures

.to.get.the.bes

t

.

QoS.for.IP.industrial.networks,.although.practically.every.single.piece.of.information.in.the.chapter.

can.be.app

lied

.to.any.IP.net

work.

.e.rea

l

.di

erence

.bet

ween

.ind

ustrial

.IP.net

works

.and.non

industrial

.

IP.net

works

.are.the.app

lications

.we.run.on.the

m

.and

,

.for.IP.QoS

,

.we.onl

y

.nee

d

.to.kno

w

.som

e

.gen

eral

.

cha

racteristic

.of.the

se

.app

lications.

.e.nex

t

.sec

tion

.sho

ws

.the.imp

ortant

.con

nections

.for.QoS

,

.pre

vi-

ously

.de

ned,

.wit

h

.the.basi

cs

.of.inf

ormation

.sec

urity

.topi

cs

.and.the.eo

rts

.dev

eloped

.in.the.las

t

.yea

rs

.

to.bui

ld

.som

e

.sta

ndards

.for.man

aging

.inf

ormation

.sec

urity

.topi

cs

.rel

ated

.wit

h

.ind

ustrial

.net

works.

.

en

,

.we.go.in.dept

h

.of.the.cla

ssical

.ter

minology,

.tec

hniques,

.and.arc

hitectures

.use

d

.toda

y

.for.get

ting

.

a.goo

d

.QoS.in.any.IP.net

work,

.sho

wing

.the.two.mos

t

.imp

ortant

.mod

els:

.Int

Serv

.and.Di

Serv.

.Als

o,

.we.

ana

lyze

.how.the.com

munication

.dev

ices

.in.the.net

work

.can.cla

ssify

.and.mar

k

.any.IP.pac

ket

.and.how.to.

man

age

.the.pos

sible

.tra

c

.con

gestion

.we.can.see.in.the.sam

e

.dev

ices.

.To.end

,

.we.ana

lyze

.two.pos

sible

.

situ

ations

.we.mus

t

.man

age

.onl

y

.if.our.IP.ind

ustrial

.net

work

.use

s

.rou

ters:

.the.con

gestion

.avo

idance

.and.

hig

h

.av

ailability

.so

lutions

.fo

r

.ro

uters.

© 2011 by Taylor and Francis Group, LLC