Комаров А.В. Цифровые сигнальные процессоры

Подождите немного. Документ загружается.

А.В. КОМАРОВ

ЦИФРОВЫЕ СИГНАЛЬНЫЕ ПРОЦЕССОРЫ

ОБНИНСК 2003

Комаров А.В. Цифровые сигнальные процессоры. – Обнинск, 2003, -

141 с.

Настоящее издание является учебным курсом для изучения

архитектуры цифровых сигнальных процессоров (и систем на их основе)

на примере процессора ADSP-2181. Пособие поддерживает курс

Процессоры цифровой обработки сигналов, который обычно читается

студентам специальности 22.01 - Вычислительные машины, комплексы,

системы и сети.

Пособие содержит две главы. В первой главе рассматриваются

особенности структурной схемы ADSP-2181, его система команд, а также

примеры программирования. Во второй главе рассматриваются методы

создания микропроцессорной системы на основе ADSP-2181.

Настоящий конспект лекций может быть полезен не только для

студентов специальности 22.01, но и для всех желающим познакомиться с

основами разработки аппаратных средств и программного обеспечения

цифровых сигнальных процессоров.

А. Комаров, 2003 г.

СОДЕРЖАНИЕ

1. АРХИТЕКТУРА ADSP-2181………………………………………. 5

1.1. Описание выводов процессора…………………………………. 5

1.2. Структурная схема ADSP-2181………………………………… 7

1.3. Память программ………………………………………………... 11

1.4. Память данных…………………………………………………... 12

1.5. Функциональная схема ALU ……………………………………13

1.6. Функциональная схема MAC……………………………………15

1.7. Функциональная схема SHIFTER……………………………….17

1.8. Функциональная схема программного конвейера…………….. 22

1.9. Система прерываний……………………………………………..28

1.9.1. Общие сведения…………………………………………….. 28

1.9.2. Последовательность обслуживания прерываний………… 29

1.9.3. Конфигурирование прерываний……………………………29

1.10. Регистры состояния и стек…………………………………….. 31

1.11. Передача данных……………………………………………….. 34

1.11.1. Генераторы адресов……………………………………….. 35

1.11.2. Узел обмена данными…………………………………….. 36

1.12. Последовательные порты……………………………………… 37

1.12.1. Общие сведения…………………………………………… 37

1.12.2. Программирование SPORT………………………………..40

1.12.3. Пример конфигурирования последовательных портов… 43

1.12.4. Сжатие данных……………………………………………..44

1.12.5. Автобуферизация…………………………………………..45

1.12.6. Пример программирования автобуферизации…………...46

1.12.7. Многоканальность…………………………….…………... 47

1.13. Таймер…………………………………………………………... 48

1.14. Системный интерфейс…………………………………………. 50

1.14.1. Сигналы синхронизации………………………………….. 51

1.14.2. Внешние прерывания……………………………………... 53

1.14.3. Флажковые биты…………………………………………...54

1.14.4. Режим энергосбережения………………………………….54

1.15. Контроллер прямого доступа к байтовой памяти (BDMA)…. 56

1.15.1. Общие сведения…………………………………………… 56

1.15.2. Регистры управления BDMA……………………………...57

1.15.3. Функционирование BDMA……………………………….. 57

1.15.4. Загрузка программ с помощью BDMA…………………...58

1.16. Порт IDMA……………………………………………………... 59

1.16.1. Сигналы IDMA……………………………………………..59

1.16.2. Функционирование IDMA………………………………... 60

1.16.3. Загрузка программ с помощью IDMA…………………… 60

1.17. Система команд………………………………………………… 61

1.17.1. Общие сведения…………………………………………… 61

1.17.2. Методы адресации……………………………………….... 62

1.17.3. Условные обозначения……………………………………. 63

1.17.4. Команды пересылки данных………………………………64

1.17.5. Команды ALU……………………………………………... 70

1.17.6. Команды MAC…………………………………………….. 79

1.17.7. Команды SHIFTER………………………………………... 82

1.17.8. Команды управления потоком программы……………… 88

1.17.9. Многофункциональные команды…………………………92

1.17.10. Прочие команды…………………………………………. 98

1.18. Инструментальные средства разработки программного

обеспечения……………………………………………………. 101

1.18.1. Инструментальные средства для DOS……………………101

1.18.2. Инструментальные средства для WINDOWS…………… 102

1.18.3. Создание проекта в VisualDSP…………………………… 102

1.18.4. Загрузка программы в EZ-KIT Lite………………………. 103

1.19. Примеры программирования в среде VisualDSP…………….. 104

1.19.1. Формирование эхо-сигнала………………………………. 104

1.19.2. Эмуляция интерфейса RS-232……………………………. 112

1.19.3. Эмуляция интерфейса RS-232 (смешанный вариант)…... 124

2. АРХИТЕКТУРА СИСТЕМЫ НА ОСНОВЕ ADSP-2181………….. 131

2.1. Структурная схема вычислительной (управляющей) системы на

основе ADSP-2181………………………………………………….131

2.2. Цепи синхронизации и запуска процессора…………………….133

ПРИЛОЖЕНИЕ 1. ФОРМАТ РЕГИСТРОВ УПРАВЛЕНИЯ………... 134

П1.1. System control register…………………………………………..134

П1.2. Data memory waitstate register………………………………….134

П1.3. SPORT0 autobuffer control register……………………………. 135

П1.4. SPORT0 control register………………………………………... 135

П1.5. SPORT1 autobuffer control register……………………………. 136

П1.6. SPORT1 control register……………………………………….. 137

П1.7. Programmable flags & Composite select control………………. 137

П1.8. Programmable flag data………………………………………… 138

П1.9. BDMA word count………………………………………………138

П1.10. BDMA control………………………………………………… 138

П1.11. BDMA external address……………………………………….. 139

П1.12. BDMA internal address……………………………………….. 139

П1.13. IDMA control…………………………………………………..139

П1.14. ICNTL register………………………………………………… 140

П1.15. IMASK register………………………………………………... 140

П1.16. IFC register……………………………………………………. 140

ЛИТЕРАТУРА…………………………………………………………... 141

1. АРХИТЕКТУРА ADSP-2181

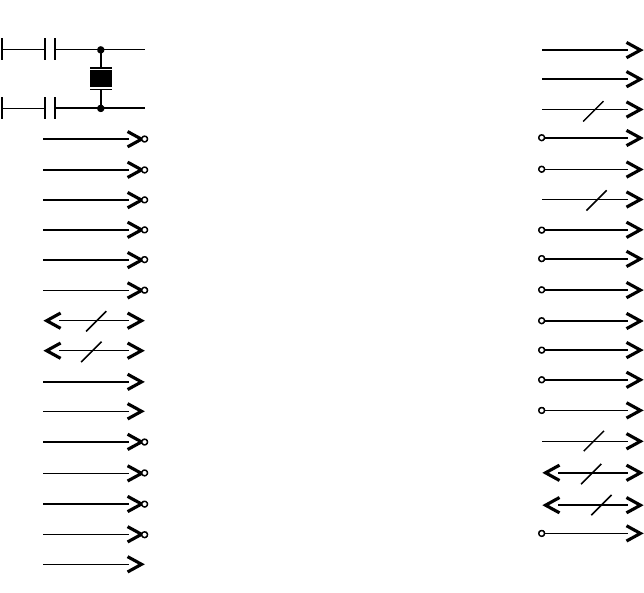

1.1. Описание выводов процессора

Условное графическое обозначение процессора ADSP2181

приведено на рис. 1.1. На этом рисунке условно не показаны 6 выводов

питания (Vdd = +5V), 11 общих выводов (GND), а также 9 сигналов,

которые используются только для связи с эмулятором. Стрелки

показывают направления передачи сигналов по отношению к процессору,

по сути, тип вывода: вход, выход, вход/выход. Перечеркнутая линия

является шиной, а рядом стоящая цифра показывает число ее

проводников.

Рис. 1.1. Условное графическое изображение ADSP-2181

Сигналы процессора имеют следующее назначение.

ADDR[13:0] – 14-битная шина адреса (ША) адресных пространств

памяти программ (ПП), памяти данных (ПД), ввода/вывода и байтовой

памяти (БП), см. п. 1.2. ША работает только на выход.

DATA[23:0] – 24-битная шина данных (ШД) адресных пространств

ПП, ПД, ввода/вывода и БП, см. п. 1.2. ШД работает на выход, когда

процессор выводит данные в одно из адресных пространств и на вход,

когда процессор вводит данные из одного из адресных пространств.

RESET# – входной сигнал начальной установки процессора, см. п.

1.14.1.

16

3

8

24

14

5

5

C2

BQC1

CLKINCLKOUTPWDACKXTALA

DSPADDR[13:0]RESET#2181RD#

PWD#WR#IRQ2#DATA[23:0]IRQE

#DMS#IRQL0#PMS#IRQL1#IOMS

#SPORT0BMS#SPORT1CMS#MM

APBG#BMODEBGH#BR#FL2:0IR

D#PF7:0IWR#IAD[15:0]IS#IACK#I

AL

IRQ2# (Interrupt Request) – входной сигнал запроса прерывания по

уровню или по фронту, см. п. 1.9.

IRQL0#, IRQL1# (Interrupt Request Level) – входные сигналы

запроса прерывания по уровню, см. п. 1.9.

IRQE# (Interrupt Request Edge) – входной сигнал запроса

прерывания по фронту, см. п. 1.9.

BR# (Bus Request) – входной сигнал запроса шины.

BG# (Bus Grant) – выходной сигнал подтверждения запроса шины.

BGH# (Bus Grant Hung) – выходной сигнал оповещения о том, что

процессор, находясь в режиме захвата, завершил все свои внутренние

операции и нуждается в шине.

PMS# (Program Memory Select), DMS# (Data Memory Select), IOMS#

(Input/Output Select), BMS# (Byte Memory Select), CMS# (Combine

Memory Select) – выходные селектирующие сигналы ПП, ПД,

ввода/вывода, БП и комбинированный соответственно, см. п. 2.1.

RD# (Read) – выходной сигнал чтения всех видов адресных

пространств.

WR# (Write) – выходной сигнал записи во все виды адресных

пространств.

MMAP (Memory Map) – входной сигнал выбора карты памяти. Если

MMAP = 0, то адреса 0х0000…0x1FFF принадлежат внутренней ПП

процессора, а адреса 0x2000…0x3FFF – внешней. В противном случае –

наоборот, см. пп. 1.3, 1.14.1, 1.15.4, 1.16.3.

BMODE (Boot Mode) – входной сигнал источника загрузки

программы. Действителен только при MMAP = 0, когда адреса 0х0000…

0x1FFF принадлежат внутренней ПП (см. выше) и необходима загрузка

программы. Если это условие выполнено, то при BMODE = 0 источником

программы является БП доступная через порт BDMA (см. п. 1.15.4). В

противном случае, загрузка программы осуществляется через порт IDMA

(см. п. 1.16.3).

CLKIN (Clock Input), XTAL (Quartz Crystal Input) – входы

хронирующей цепи встроенного генератора тактовых импульсов

процессора, см. п. 1.14.1.

CLKOUT (Clock Output) – выходной синхросигнал процессора,

частота которого в два раза выше частоты входного синхросигнала на

входе CLKIN, см. п. 1.14.4.

SPORT0, SPORT1 (Serial Port0, 1) – входы/выходы

последовательных портов 0 и 1, см. п. 1.12.

IRD# (IDMA Read), IWR# (IDMA Write), IS# (IDMA Select), IAL

(IDMA Address Latch) – управляющие сигналы доступа к портам

контроллера прямого доступа к памяти (КПДП) IDMA, см. п. 1.16.

IAD – 16-битная шина адреса/данных КПДП IDMA, см. п. 1.16.

IACK# (IDMA Acknowledge) – подтверждение доступа к портам

КПДП IDMA, см. п. 1.16.

PWD# (Power Down) – перевод процессора в режим

энергосбережения (при PWD# = 0) , см. п. 1.14.4.

PWDACK (Power Down Acknowledge) – выходной сигнал

подтверждения режима энергосбережения, см. п. 1.14.4.

FL2:0 – выходные сигналы внутреннего 3-битного параллельного

порта процессора (выходные флаги) , см. п. 1.14.3.

PF7:0 – программируемые входы/выходы процессора, см. п. 1.14.3.

1.2. Структурная схема ADSP-2181

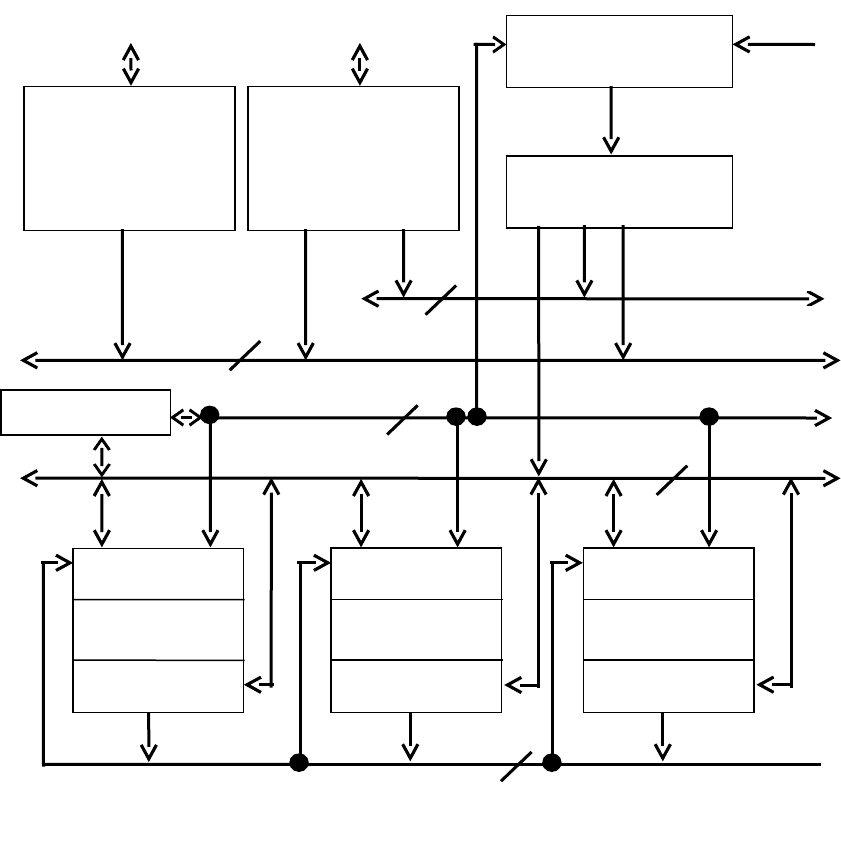

Структурную схему процессора можно условно разделить на две

части: базовую (общую для всех процессоров ADSP-21хх, рис 1.2.) и

периферийную (характерную, в основном, для процессора ADSP-2181,

рис. 1.3).

Рис. 1.2 показывает, что к базовой части процессора отнесены:

внутренние шины PMA BUS, DMA BUS, PMD BUS DMD BUS, I

BUS, R BUS;

узел обмена данными BUS EXCH(ANGE);

Рис. 1.2. Структурная схема базовой части процессора ADSP-2181

14

16

16

24

14

I BUS

R BUS

DMD BUS

PMD BUS

DATA

ADDRESS

GENERATOR

#1

DMD BUS

DATA

ADDRESS

GENERATOR

#2

DMD BUS

INSTRUCTION

REGISTER

PROGRAM

SEQUENCER

PMA BUS

DMA BUS

INP REGS

ALU

OUT REGS

INP REGS

MAC

OUT REGS

INP REGS

SHIFTER

OUT REGS

BUS EXCH

вычислительные устройства ALU (арифметико-логическое

устройство), MAC (Multiplier/ACcumulator - умножитель/акку-

мулятор) и SHIFTER (устройство сдвига);

генераторы адресов данных DAG1 и DAG2, регистр команд

INSTRUCTION REGISTER и программный конвейер PROGRAM

SEQUENCER.

Внутренние шины обеспечивают пересылку команд из ПП, а также

данных из памяти данных в вычислительные устройства и обратно. К ним

относятся: шина адреса ПП PMA BUS (Program Memory Address Bus),

шина адреса ПД DMA BUS (Data Memory Address Bus), шина данных ПП

PMD BUS (Program Memory Data Bus), шина данных ПД DMD BUS (Data

Memory Data Bus), шина команд I BUS (Instruction Bus) и шина

результатов вычислений R BUS (Result Bus).

Можно говорить о наличии у процессора четырех магистралей: ПП

PMA, PMD BUS, ПД DMA, DMD BUS, команд I BUS и результатов

вычислений R BUS. Наличие множества внутренних магистралей

позволяет распараллеливать процесс пересылок команд и данных, в

частности, можно совместить во времени вычисление и считывание

данных из памяти программ и памяти данных (см. п. 1.17.9). Это

позволяет существенно повысить производительность процессора.

Магистрали ПП и ПД соединены между собой с помощью узла обмена

данными BUS EXCH (см. п. 1.5).

Ширина адресных шин (PMA, DMA) – 14 бит, что обеспечивает

доступ к 16К ячейкам памяти. Ширина шины данных ПП (PMD, I) – 24

бита по числу бит команды процессора. Все оставшиеся шины (DMD, R)

имеют ширину 16 бит, что позволяет обмениваться 16-битными данными

за один цикл доступа к ПД.

Все вычислительные устройства имеют входные регистры (INP

REGS), над содержимым которых они выполняют арифметические

операции или операции сдвига. В ALU и MAC к таким регистрам

относятся Х- и Y- регистры (см. пп. 1.5, 1.6), а в SHIFTER – S-регистр. Х-

и S-регистры подключаются к DMD, а Y-регистры – к PMD, что

позволяет одновременно считывать данные из памяти данных в Х-

регистры, а из памяти программ – в Y-регистры вычислительных

устройств.

Результаты арифметических операций и операций сдвига

сохраняются в выходных регистрах (OUT REGS) вычислительных

устройств, которые связаны с DMD и шиной результатов R. Шина DMD

используется для обмена данными с ПД. Шина результатов позволяет

использовать результат операции одного вычислительного устройства в

качестве операнда в другом вычислительном устройстве без потери

времени на сохранение результата операции в ПД.

DAG1 и DAG2 используются для реализации косвенной и

косвенной автоинкрементной/автодекрементной адресации данных (см. п.

1.11), поскольку среди прочих содержат по четыре регистра указателей.

Программный конвейер формирует адреса инструкций для ПП. Он

управляет регистром инструкций, который содержит исполняемую в

данный момент команду. Команды загружаются в регистр инструкций в

течение одного цикла, а исполняются в течение следующего,

одновременно с загрузкой следующей инструкции.

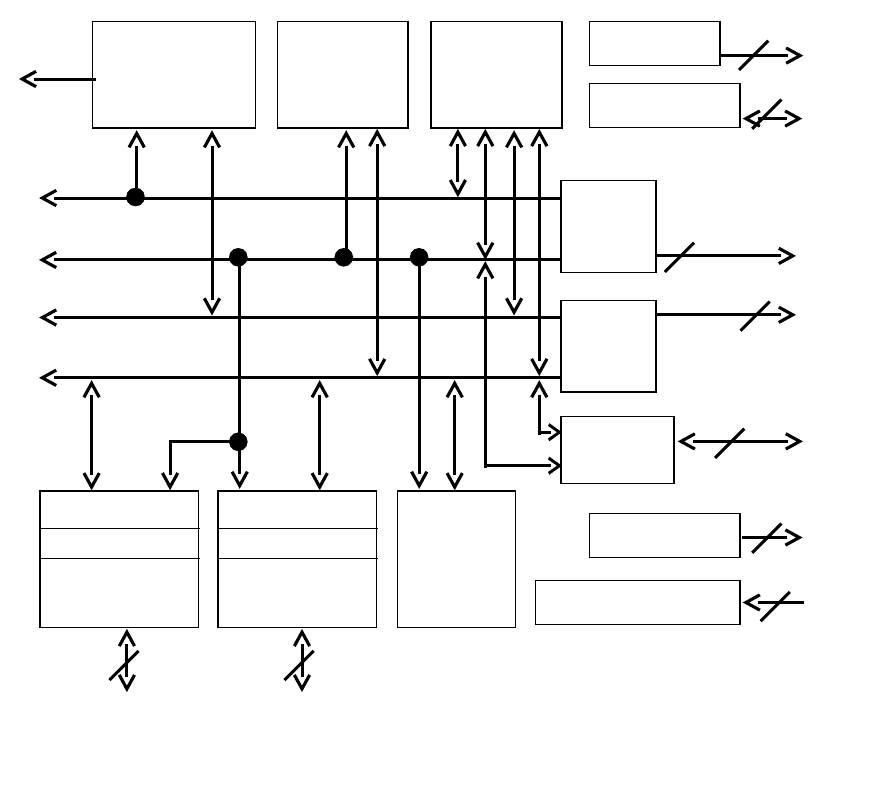

Рис. 1.3 показывает, что к периферийной части процессора отнесены:

мультиплексор шины адреса MUX1;

мультиплексор шины данных MUX2;

память программ – PROGRAM SRAM;

память данных – DATA SRAM;

байтовый КПДП – BDMA (Byte DMA Controller);

внутренний КПДП – IDMA PORT (Internal DMA PORT);

последовательные синхронные порты SERIAL PORT0, 1;

таймер – TIMER;

узел управления энергосбережением процессора – PDCL (Power

Down Control Logic);

программируемые входы/выходы – PROG(rammable). I/O;

выходы флагов – FLAGS;

входы запросов прерываний – INTERRUPTS.

I BUS

4

3

21

EXTERNAL

DATA

BUS

2414

EXTERNAL

ADDRESS

BUS

PMA BUS

8

2

PROGRAM

SRAM

16K x 24

DMD BUS

PMD BUS

DMA BUS

Рис. 1.3. Структурная схема периферийной части процессора

ADSP-2181

DATA

SRAM

16K x 16

BDMA PDCL

PROG. I/O

MUX

1

MUX

2

IDMA

PORT

TRN REG

RCV REG

SERIAL

PORT 0

TRN REG

RCV REG

SERIAL

PORT 1

TIMER

FLAGS

INTERRUPTS

5 5

Периферийная и базовая части процессора соединяется внутренними

шинами I, PMA, DMA, PMD, DMD. На рис. 1.3 их выходы изображены

слева. Справа и снизу изображены внешние входы/выходы, которыми

процессор соединяется с внешним миром. Для выдачи адреса на

внешнюю шину адреса EXTERNAL ADDRESS BUS используется

мультиплексор шины адреса MUX1. Если идет обращение к внешнему

адресному пространству ПП, то на внешнюю шину адреса попадает код

адреса с PMA. Если идет обращение к внешнему адресному пространству

ПД, то на внешнюю шину адреса попадает код адреса с DMA. Выводы

внешней шины адреса имеют обозначения ADDR[13:0] (см. п. 1.1).

Для взаимодействия с внешней шиной данных (ввод команд или

ввод/вывод данных) EXTERNAL DATA BUS используется

мультиплексор шины данных MUX2. Если идет обращение к внешнему

адресному пространству ПП, то код команды с внешней шины данных

попадает на PMD. Если идет обращение к внешнему адресному

пространству ПД, то внешняя шина данных соединяется с DMD. Выводы

внешней шины данных имеют обозначения DATA[23:0] (см. п. 1.1).

ПП (см. п. 1.3) используется для хранения программы и данных. Это

ОЗУ статического типа (SRAM – Static RAM), поэтому во время сброса

процессора обычно осуществляется загрузка программы (см. пп. 1.15.4,

1.16.3).

ПД (см. п. 1.4) используется для хранения данных. В ее адресном

пространстве располагаются также некоторые регистры специального

назначения (РСН, см. пп. П1.1-П1.16).

Байтовый КПДП (см. п. 1.15) используется для взаимодействия с БП

процессора (ввод программ, ввод/вывод данных). БП подключается к

внешней магистрали процессора (внешние шины адреса и данных) с

использованием селектирующего сигнала BMS# (см. п. 1.1). В частности,

байтовая память может использоваться для хранения программы, которая

во время сброса процессора загружается во внутреннюю ПП. Записать

данные в БП или считать их оттуда прямо из программы (без

использования байтового КПДП) невозможно, поскольку только

байтовый КПДП формирует сигнал BMS#.

Внутренний КПДП (см. п. 1.16) используется для связи с внешним

миром, например, для ввода программы во внутреннюю ПП при сбросе

процессора, а также для ввода и вывода данных. Имеет собственную

магистраль (см. п. 1.1), в которую входят: шина адреса/данных IAD[15:0]

и шина управления IRD#, IWR#, IS#, IAL, IACK#. Поскольку шина адреса

данных 16-битная, возможен обмен двухбайтными словами.

Последовательные синхронные порты (см. п. 1.12) используются для

связи с внешним миром, например, для связи с другим процессором или

любым другим последовательным синхронным портом. Связь

осуществляется с использованием пяти выводов. По одному из них

данные принимаются в регистр REC REG, по другому данные выдаются

из регистра TRN REG, оставшиеся выводы используются для

формирования управляющих сигналов. На рис. 1.3 условно не показан