Комаров А.В. Цифровые сигнальные процессоры

Подождите немного. Документ загружается.

данных

0x3FF5 Делитель частоты битовой синхронизации SPORT0

0x3FF4 Делитель частоты приемного фрейма SPORT0

0x3FF3 Регистр управления автобуферизацией SPORT0

0x3FF2 Регистр управления SPORT1: значение выходного флага,

выбор источника битовой синхронизации, управление

фреймовой синхронизацией, режим сжатия данных, выбор

длины слова данных

0x3FF1 Делитель частоты битовой синхронизации SPORT1

0x3FF0 Делитель частоты приемного фрейма SPORT1

0x3FЕF Регистр управления автобуферизацией SPORT1

Работа с регистрами данных проста. Например, для выдачи

содержимого регистра АХ0 через SPORT1 достаточно написать ТХ1 =

АХ0;. А для считывания принятых данных из SPORT0 – AY0 = RX0;.

Обычно эта пересылка осуществляется в обработчике прерывания по

приему последовательного порта.

Перед первым использованием последовательных портов кроме

регистров, упомянутых в табл. 1.13, необходимо проинициализировать

биты 12-10 регистра управления системой System Control Register (см. п.

П1.1), расположенного по адресу 0x3FFF. Бит 12 разрешает работу

SPORT0, а бит 11 – SPORT1, если они установлены. После сброса

процессора эти биты обнулены, поэтому для работы с соответствующими

последовательными портами они должны быть программно установлены.

Бит 10 регистра управления системой определяет конфигурацию

SPORT1. Если бит 10 установлен, то SPORT1 работает в режиме

последовательного порта, в противном случае – в альтернативном режиме

в соответствии с табл. 1.14.

Таблица 1.14.

Альтернативная конфигурация SPORT1

Имя контакта Альтернативное имя Альтернативная функция

RFS1 IRQ0# Внешнее прерывание 0

TFS1 IRQ1# Внешнее прерывание 1

DR1 FI Входной флаг

DT1 FO Выходной флаг

SCLK1 SCLK1 Та же самая

Источник битовой синхронизации (внутренний или внешний)

SPORT0 и SPORT1 может быть выбран с помощью бита 14 (ISCLK)

регистров управления соответственно SPORT0 и SPORT1 (см. пп. П1.4,

П1.6).

Если бит ISCLK установлен, то процессор генерирует собственный

сигнал SCLK, в противном случае – использует внешний сигнал SCLK.

Очевидно, что выход SCLK двунаправленный. После сброса процессора

ISCLK = 0, поэтому после сброса процессора оба порта работают в

режиме внешнего сигнала SCLK.

Частота внешнего сигнала битовой синхронизации может иметь

значение до Fclkout, где Fclkout – частота синхронизации процессора

(частота сигнала на выходе CLKOUT (см. рис. 1.1) процессора). Частота

внутреннего сигнала битовой синхронизации не может иметь значение

более Fclkout/2 и устанавливается с помощью регистров SCLKDIV

(0x3FF5 для SPORT0 и 0x3FF1 для SPORT1, см. табл. 1.13):

Fsclk = Fclkout / (2 * (SCLKDIV + 1)) (1.1)

где: Fsclk - частота битовой синхронизации (частота сигнала на выходе

SCLK процессора), SCLKDIV - содержимое соответствующих регистров.

Формула (1.1) позволяет определить делитель частоты SCLKDIV для

достижения необходимой скорости обмена данными (частоты битовой

синхронизации). Например, максимальная частота обмена имеет место

при SCLKDIV = 0 и равна Fclkout/2. Формула (1.1) справедлива и для

случая, когда SPORT1 используется в альтернативном режиме, поскольку

функция выхода SCLK1 при этом не изменяется (см. табл. 1.14).

Длину посылки можно устанавливать независимо для каждого

последовательного порта с помощь битовых полей SLEN (Serial Length –

длина последовательных данных) регистров управления SPORT0 и

SPORT1 (см. пп. П1.4, П1.6). Битовые поля SLEN занимают биты 3-0

соответствующих регистров управления.

Поля занимают четыре бита, поэтому можно задать длину посылки в

пределах 16-3 битов. Если длина посылки меньше 16 бит, то посылка

располагается в младших битах регистров данных последовательных

портов.

Фреймовая синхронизация используется для обозначения начала

каждого передаваемого слова. Последовательные порты множеством

способов и независимо (при приеме и передаче) могут управлять

сигналами фреймовой синхронизации. Все фреймовые сигналы изменяют

состояния по срезу импульсов битовой синхронизации (SCLK).

Тип фреймовой синхронизации определяется битами 13 (RFSR) и 11

(TFSR) регистров управления портами (см. пп. П1.4, П1.6). Если RFSR =

0, то RFS требуется только для первого слова фрейма данных (фреймовая

при приеме синхронизация отсутствует), в противном случае RFS

требуется для каждого слова фрейма данных. Если TFSR = 0, то TFS

требуется только для первого слова фрейма данных (фреймовая

синхронизация пр передаче отсутствует), в противном случае TFS

требуется для каждого слова фрейма данных.

После сброса процессора RFSR = 0 и TFSR = 0, поэтому связь в

обоих направлениях осуществляется без фреймовой синхронизации. Для

ее инициализации необходимо программно установить биты RFSR и/или

TFSR.

Источник фреймовой синхронизации определяется битами 9 (ITFS)

и 8 (IRFS) регистров управления портами (см. пп. П1.4, П1.6). Если ITFS

= 0, то используется внешний сигнал TFS, в противном случае сигнал TFS

является внутренним. Если IRFS = 0, то используется внешний сигнал

RFS, в противном случае сигнал RFS является внутренним.

Если используются внешние фреймовые сигналы, то RFS и TFS

являются входами и внешнее устройство управляет передачей и приемом

данных. Для порта это означает, что перед выдачей в канал данных он

должен дождаться сигнала TFS, а перед приемом – сигнала RFS.

Если фреймовые сигналы формируются портом, то RFS и TFS

являются выходами и временные параметры обмена определяются

процессором. В этом случае сигнал TFS формируется при загрузке

любого регистра передаваемых данных ТХ0 или ТХ1. Сигнал RFS

формируется периодически в соответствии с содержимым регистра

делителя частоты приемного фрейма RFSDIV (0x3FF4 для SPORT0 и

0x3FF0 для SPORT1, см. табл. 1.13).

Содержимое RFSDIV трактуется портом как число импульсов SCLK

(уменьшенное на единицу), между двумя импульсами RFS. Например, для

того чтобы импульс RFS выдавался на каждый 256-ой импульс SCLK

необходимо в RFSDIV записать число 255. Значение RFSDIV + 1 не

должно быть меньше SLEN. После получения импульса RFS внешнее

устройство должно выдать слово данных.

Следует отметить, что фреймовые сигналы формируются даже тогда,

когда сигнал SCLK является внешним. Это дает возможность для

различных применений делить частоту входной

синхропоследовательности. Кроме этого, для обеспечения одновременной

передачи и приема данных можно использовать один фреймовый сигнал.

Для этого необходимо подать выходной сигнал RFS на вход TFS,

запрограммированный на прием внешнего сигнала синхронизации.

Последовательные порты могут работать в нормальном или

альтернативном фреймовых режимах. В нормальном режиме

фреймовый сигнал проверяется на срезе SCLK. Если фреймовый сигнал

распознан, то принимаемые данные защелкиваются на срезе SCLK,

начиная со следующего импульса, а выдаваемые данные появляются

после фронта SCLK, также начиная со следующего импульса. Далее

фреймовые сигналы не проверяются до полного приема или полной

передачи слова данных. Если передача/прием слов непрерывны, т.е. за

последним битом предыдущего слова следует первый бит следующего

слова, то фреймовый сигнал формируется во время передачи последнего

бита предыдущего слова.

В альтернативном режиме фреймовый сигнал активизируется при

передаче первого бита текущего слова. Принимаемые биты

защелкиваются на срезе SCLK, а выдаваемые - появляются после фронта

SCLK. Внутренний сигнал фрейма остается активным до конца передачи

текущего слова. Внешний сигнал фрейма проверяется только во время

первого бита.

Выбор фреймового режима определяется значениями битов ширины

фреймовых сигналов – RFSW (RFS Width - ширина RFS) и TFSW (TFS

Width – ширина TFS). RFSW располагается в бите 12, а TFSW – в бите 10

регистров управления портами (см. пп. П1.4, П1.6). Причем нулевое

значение этих битов определяет нормальный режим, а единичное –

альтернативный. После сброса процессора все эти биты обнулены, что

создает нормальный фреймовый режим для приема и передачи.

Программно можно также выбрать уровни активности фреймовых

сигналов. Для этого необходимо определить биты инверсии фреймовых

сигналов – INVTFS (INVerse TFS) и INVRFS (INVerse RFS). INVTFS

располагается в бите 7, а INVRFS – в бите 6 регистров управления

портами (см. пп. П1.4, П1.6). Причем нулевое значение этих битов

определяет высокий уровень активных фреймовых сигналов, а единичное

– низкий. После сброса процессора все эти биты обнулены, что

устанавливает высокий уровень активных фреймовых сигналов.

1.12.3. Пример конфигурирования последовательных портов

Ниже приводится пример конфигурирования портов SPORT0 и

SPORT1. SPORT0 генерирует сигналы битовой синхронизации (SCLK),

сигналы фреймовой синхронизации, а также сжимает данные по –

закону. Это типичный пример установок для связи с комбинированным

кодеком.

SPORT1 использует внешнюю битовую синхронизацию, внешнюю

фреймовую синхронизацию, отсутствие сжатия 16-битных данных и

автобуферизацию. Это типичный пример установок для связи с другими

процессорами многопроцессорной системы.

В примере инициализируются только самые необходимые

конфигурационные регистры. Инициализация производится перед

разрешением последовательных портов. Кроме этого, перед разрешением

прерываний необходимо сбросить все внешние запросы на прерывания от

последовательных портов.

{ПРОГРАММА ИНИЦИАЛИЗАЦИИ SPORT0, SPORT1}

{Сначала инициализируем SPORT1}

AX0 = 0x0017;

DM(0x3FEF) = AX0; {разрешение автобуферизации}

{авто буфер ТХ использует I0 и M0}

{авто буфер RХ использует I1 и M1}

AX0 = 0x280F;

DM(0x3FF2) = AX0; {внешние SCLK, RFS и TFS}

{ RFS и TFS требуются, нормальный фреймовый}

{режим, отсутствие сжатия, 16 бит}

{Далее инициализируем SPORT0}

{Предполагаем, что Fclkin = 12.288 МГц}

AX0 = 255;

DM(0x3FF4) = AX0; {RFSDIV + 1 = 256, частота фреймовой}

{cинхронизации = 8 КГц}

AX0 = 2;

DM(0x3FF5) = AX0; {SCLKDIV + 1 = 3, частота битовой}

{cинхронизации = 2.048 МГц}

AX0 = 0x6B27;

DM(0x3FF2) = AX0; {внутренние SCLK, RFS и TFS}

{ RFS и TFS требуются, нормальный фреймовый}

{режим, сжатие по -закону, 8 бит}

{И, наконец, разрешаем работу портов и прерывания}

IFC = 0x1E; {очищаем все SPORT запросы на прерывания}

ICNTL = 0; {запрещаем вложенные прерывания}

AX0 = 0x1C1F; {разрешаем оба SPORT, BWAIT и PWAIT}

DM(0x3FFF) = AX0; {оставляем по умолчанию}

IMASK = 0x1E; {разрешаем все прерывания SPORT}

1.12.4. Сжатие данных

Сжатие данных или в более широком смысле компандинг (от

COMpressing и exPANDing – сжатие и расширение данных) – это процесс

логарифмического кодирования и декодирования данных с целью

уменьшения числа передаваемых битов. Процессор содержит один узел

сжатия данных (см. рис. 1.10) на два порта, который за один машинный

цикл может произвести одно сжатие или одно расширение данных. При

наличии коллизий приоритет имеет SPORT0.

Процессор поддерживает два наиболее широко распространенных

алгоритма сжатия: А и . Компандинг производится в соответствии с

протоколом G.711, рекомендованного CCITT. Тип компандинга может

выбран независимо для каждого порта с помощью битов 5 и 4 (битовое

поле DTYPE) в регистрах управления портами (см. пп. П1.4, П1.6). Так

код 11 в этих битах устанавливает алгоритм сжатия А, а код 10 –

алгоритм сжатия .

Оставшиеся комбинации кода в этих битах определяют формат

полученных данных длиною меньше 16 бит при отключенном

компандинге. Так комбинация 01 определяет правое выравнивание и

заполнение старших битов знаковым битом переданного слова, а

комбинация 00 – правое выравнивание и заполнение старших битов

нулем.

Если компандинг включен, то в регистрах RX0, RX1 находится

значение с правым выравниваем и распространенным знаковым битом –

расширенное из восьми принятых битов. Подобно этому запись в

регистры ТХ0, ТХ1 вызывает сжатие 16-битного числа в восьми битное с

правым выравниванием и распространением знака. Сжатие происходит

перед перезаписью числа из регистра передаваемых данных в сдвиговый

регистр передачи (см. рис. 1.10). Если абсолютное значение

передаваемого числа выходит за пределы 13 бит для алгоритма А или 14

бит для алгоритма , то такое число автоматически сжимается до

максимального положительного или отрицательного значения.

1.12.5. Автобуферизация

В обычных условиях SPORT формирует запрос на прерывание, когда

он получил или начал выдавать слово данных. Автобуферизация

обеспечивает механизм приема/передачи целого блока последовательных

данных прежде чем сформируется запрос на прерывание. Это уменьшает

частоту прерываний, что ведет к увеличению производительности

системы.

Автобуферизация использует способность DAG1, DAG2

поддерживать адресацию кольцевых буферов. При передаче слово данных

из кольцевого буфера (по указателю, содержащегося в одном из

индексных регистров Ix) пересылается в регистр ТХ0 или ТХ1, из

которых передается в канал связи. После выполнения пересылки

индексный регистр Ix модифицируется с помощью соответствующего

регистра модификации Мх, как и при обычных пересылках. Каждая

передача слова данных в канал связи не формирует запроса на

прерывание. Такой запрос формируется только после записи в ТХ0 или

ТХ1 последнего слова данных кольцевого буфера, когда в индексном

регистре формируется адрес первого слова кольцевого буфера.

При приеме данных из канала связи принятое слово записывается в

кольцевой буфер по указателю, содержащегося в одном из индексных

регистров Ix. После выполнения пересылки индексный регистр Ix

модифицируется с помощью соответствующего регистра модификации

Мх, как и при обычных пересылках. Запрос на прерывание формируется

после приема в кольцевой буфер последнего слова данных, когда в

индексном регистре формируется адрес первого слова кольцевого буфера.

Режим автобуферизации может быть независимо разрешен для

приема и передачи с помощью регистров управления автобуферизацией

(см. пп. П1.3, П1.5).

Номера xIREG в регистрах управления автобуферизацией могут

быть в диапазоне 0-3 для DAG1 и в диапазоне 4-7 для DAG2. Номера

xMREG (там же) могут быть любыми в диапазоне 0-3. Предполагается,

что они принадлежат тому DAGx, в котором определен соответствующий

xIREG.

После сброса процессора (а также после очередной загрузки

программы) биты TBUF, RBUF обнуляются, что соответствует

запрещению автобуферизации.

1.12.6. Пример программирования автобуферизации

Программа конфигурирует SPORT1 на выполнение операций с

автобуферизацией. Предполагается, что Fclkin = 12.288 МГц. SPORT1

будет автоматически передавать данные из кольцевого буфера с именем

tx_buffer. Он также будет принимать данные из канала связи и

автоматически записывать их в кольцевой буфер с именем rx_buffer.

Запрос на прерывание по передаче будет сформирован после

передачи всех данных буфера tx_buffer в регистр ТХ1, но перед

перезаписью последнего данного в сдвиговый регистр передачи. Запрос

на прерывание по приему будет сформирован после заполнения буфера

rx_buffer.

.MODULE/RAM code_to_init_Auto_Buff_SPORT1;

{Объявление переменных и точки входа в программу}

.VAR /DM/CIRC tx_buffer[10];

.VAR /DM/CIRC rx_buffer[10];

.ENTRY sport1_inits;

{Инициализация I, M и L регистров}

sport1_inits: I0 = ^tx_buffer; {I0 содержит начальный адрес tx_buffer}

M0 = 1; {используем каждый адрес буферов}

L0 = %tx_buffer; {L0 содержит длину буфера tx_buffer}

I1 = ^rx_buffer; {I1 содержит начальный адрес rx_buffer}

L1 = %rx_buffer; {L1 содержит длину буфера rx_buffer}

{Инициализация SPORT1 на автобуферизацию}

AX0 = 0x0013; {ТХ использ. I0, M0; RX использ. I1, M0}

DM(0x3FEF) = AX0; {автобуферизация разрешена}

{Инициализация SPORT1 на Frfs = 8 КГц, Fsclk = 2.048 МГц}

AX0 = 255; {RFSDIV = 255 для Frfs = 8 КГц}

DM(0x3FF0) = AX0;

AX0 = 2; {SCLKDIV = 2 для Fsclk = 2.048 МГц}

DM(0x3FF5) = AX0;

{Разрешение в SPORT1 нормального фрейминга и внутреннего SCLK}

AX0 = 0x6B27; {нормальный фрейминг, 8-бит -закон}

DM(0x3FF2) = AX0; {внутренняя байтовая синхронизация }

{Инициализация прерываний}

IFC = 6; {очистка всех внешних SPORT запросов}

ICNTL = 0; {запрет вложенных прерываний}

IMASK = 6; {разрешение прерываний от SPORT1}

{Передача первого слова данных в ТХ1}

AX0 = DM(0xI0, M0);

TX1 = AX0;

RTS;

.ENDMOD;

1.12.7. Многоканальность

SPORT0 поддерживает многоканальность. Это означает, что к

SPORT0 ведущего процессора можно подключить до 32-х SPORT0

ведомых процессоров. Очевидно, что передача данных в этом случае

может осуществляться только в режиме временного

мультиплексирования, т.е. в текущий промежуток времени канал связи

может занимать только один из ведомых процессоров. Возможность

подключения выходов DT0 всех ведомых процессоров к входу DR0

ведущего процессора (исключение конфликта) обеспечивается тем, что

выходы DT имеют третье состояние, которое снимается только на время

выдачи данных.

В одноканальном режиме сигналы RFS0 и TFS0 обеспечивают

начало передачи/приема единственного слова или потока слов от одного

источника (см. п. 1.12.2). При этом передача и прием происходят

независимо друг от друга. В многоканальном режиме сигнал RFS0

(выводы RFS0 ведущего процессора и всех ведомых процессоров

объединены) определяет начало передачи блока из 24 или 32 слов от

каждого из ведомых процессоров, при этом операции приема/передачи

протекают параллельно. Функции сигнала TFS0 описываются ниже.

Многоканальные операции разрешаются установкой бита 15 (МСЕ)

в регистре управления SPORT0 (0x3FF6, см. п. П1.4). Это также

переопределит назначение некоторых битов этого регистра. В частности

бит 9 становится битом, который определяет длину блока данных в

многоканальном режиме (MCL). Если MCL = 0, то блок данных содержит

24 слова (канала), в противном случае (MCL = 1) блок данных содержит

32 слова. Длина слов, как и прежде, определяется полем SLEN регистра

управления SPORT0 и может изменяться от 3 до 16 бит.

Биты 13…10 регистра управления SPORT0 в многоканальном

режиме определяют значение многоканальной задержки фрейма (MFD =

0…15). Значение MFD определяет задержку (в импульсах сигнала

SCLK0) появления первого бита первого передаваемого слова блока

данных из 24 или 32 слов после выдачи сигнала RFS0 ведущим

процессором.

Для конфигурирования SPORT0 в многоканальном режиме

используются также регистры разрешения приема блока данных Receive

Word Enables (RWE, 0x3FF9 - младший регистр и 0x3FFA - старший

регистр) и разрешения передачи блока данных Transmit Word Enables

(TWE, 0x3FF7 - младший регистр и 0x3FF8 - старший регистр). Единица в

любом бите этих регистров разрешает прием/передачу соответствующего

канала, ноль – запрещает.

Принимаемые слова от запрещенных каналов игнорируются

приемником – они не записываются в регистр RX0, не формируются

запросы на прерывания по приему и автобуферизации. При передаче

запрещенного канала (выход DT находится в третьем состоянии) также не

формируются запросы на прерывания по передаче и автобуферизации.

Для приема данных от двух ведомых процессоров во все биты

регистра RWE ведущего процессора необходимо записать единицы, в

регистры TWE первого ведомого процессора необходимо записать

единицы во все четные биты, а во втором ведомом процессоре – во все

нечетные биты.

Функционирование SPORT0 в многоканальном режиме во многих

отношениях совпадает с функционированием в одноканальном режиме

(см. пп. 1.12.1…1.12.6). В частности, это относится к длине

передаваемых/принимаемых слов (SLEN), внутреннему и внешнему

фреймингу (IRFS), инверсии фреймовых сигналов (INVRFS),

компандингу (DTYPE) и автобуферизации. Следует только помнить, что

сигнал RFS формируется один раз для всего блока данных.

Сигнал TFS0 имеет функции подтверждения действительности

передаваемых данных (TDV) и активизируется только на промежуток

времени передачи данных разрешенного канала. Уровень активности

определяется битом 7 регистра управления SPORT0 (в многоканальном

режиме он называется INVTDV), если INVTDV = 0, то уровень TDV

высокий, в противном случае – низкий. Сигналы TDV обычно

используются внешними узлами процессоров (или совсем не

используются).

1.13. Таймер

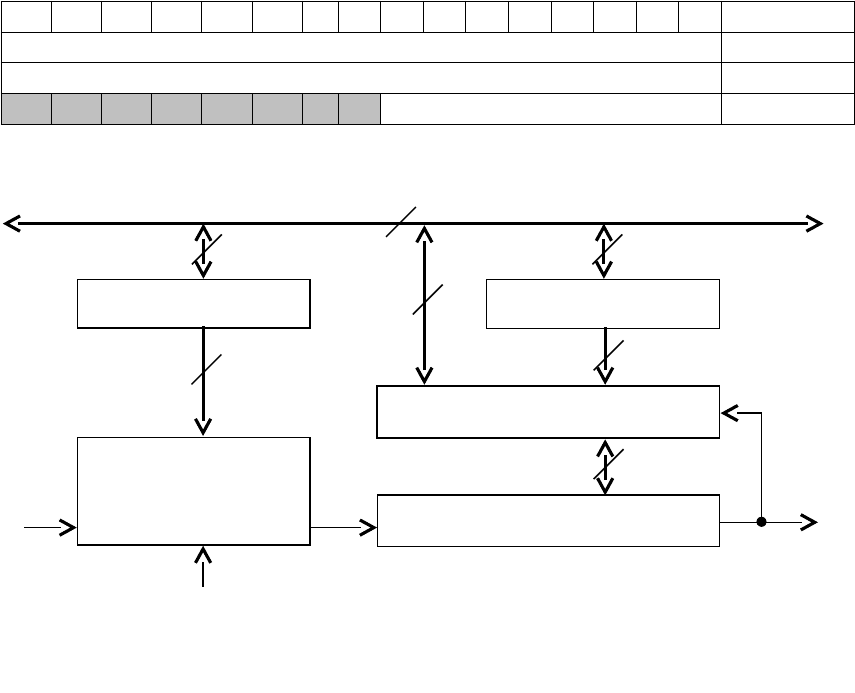

Программируемый интервальный таймер (рис. 1.11) позволяет

генерировать запросы на прерывания с периодом кратным длительности

машинного цикла. Период запросов может программно задаваться в

широком диапазоне значений.

Таймер содержит два 16-битных регистра TCOUNT, TPERIOD и

один 8-битный регистр TSCALE. Команда управления расширенным

режимом (см. п. 1.17.10.б) может разрешить или запретить работу

таймера установкой или сбросом бита 5 регистра MSTAT. Регистр

TCOUNT является счетчиком. Если таймер разрешен, то счетчик

декрементируется с частотой вплоть до CLKOUT. Когда содержимое

счетчика достигает нуля, то формируется запрос на прерывание, а счетчик

перегружается из регистра TPERIOD и счет начинается снова.

Регистр TPERIOD (как и TCOUNT) может быть программно

загружен любым 16-битным числом (через DMD шину, см. рис. 1.11),

которое рассматривается как число без знака. Регистр TSCALE хранит

коэффициент деления (уменьшенный на единицу) частоты импульсов

декрементирования счетчика. Можно утверждать, что период следования

запросов на прерывания Tint определяется формулой:

Tint = (TPERIOD + 1) * (TSCALE + 1) / Fclkout. (1.2)

Форматы регистров TCOUNT, TPERIOD, TSCALE и их адреса

приведены в табл. 1.15.

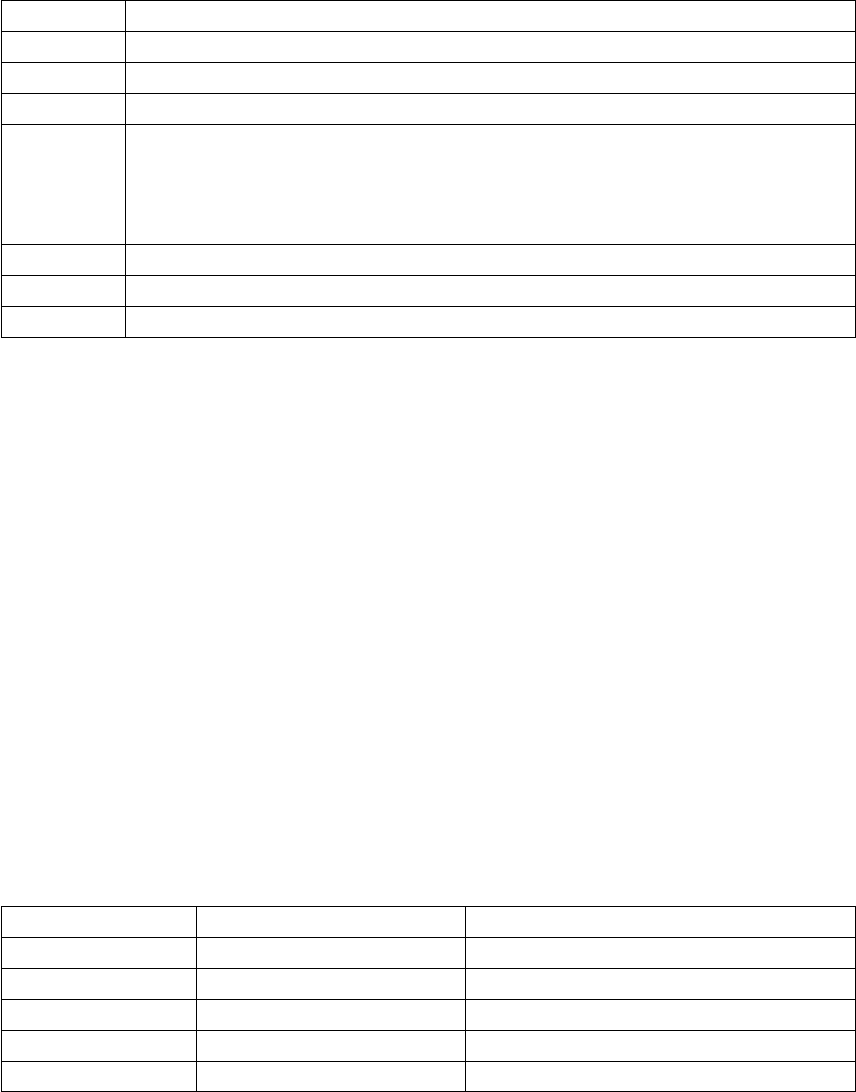

Таблица 1.15

Формат регистров TCOUNT, TPERIOD, TSCALE и их адреса

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 Адрес

TPERIOD 0x3FFD

TCOUNT 0x3FFC

0 0 0 0 0 0 0 0 TSCALE 0x3FFB

1.14. Системный интерфейс

К системному интерфейсу относится аппаратная часть и

программное обеспечение, которые используются для управления

процессором. Сигналы управления процессором включают: RESET#,

сигналы синхронизации, флаги входов и выходов, запросы на

прерывания, запрос на режим энергосбережения.

1.14.1. Сигналы синхронизации

Для синхронизации процессора на его вход CLKIN необходимо

подать сигнал от внешнего генератора с ТТЛ уровнями или подключить

кварцевый резонатор между CLKIN и XTAL, как это показано на рис. 1.1.

Если используется внешний сигнал синхронизации, вход XTAL должен

оставаться неподключенным. Нельзя также прерывать внешний сигнал

синхронизации или изменять его частоту во время работы процессора.

DMD 16

8

TSCALE

Рис. 1.11. Структурная схема таймера

CLKOUT

8

Разрешение

таймера и узла

прескалера

Timer Enable

16

TPERIOD

Узел загрузки счетчика

16

16

16

-1 TCOUNT Нуль

Запрос на прерывание

от таймера