Кагиров Р.Р. Лекции по Организации ЭВМ

Подождите немного. Документ загружается.

данные - в главном или во вторичном. Для перемещения данных между

пространствами были добавлены специальные команды. Поскольку система

допускает многопроцессорные конфигурации, для исключения конфликтов

обращений разных процессоров в начальную область ОП была введена

префиксация (prefixing) адреса, заключающаяся в преобразовании реального

адреса в абсолютный (физический) адрес.

В Системе 370 с расширенной архитектурой (370-XA) разрядность адреса ОП

была увеличена до 31 с сохранением совместимости с 24(26)-разрядными

системами. Добавлены команды для установки способа адресации и переходов

от одного способа адресации к другому. Введен второй уровень процессорной

памяти - расширенная ОП, являющаяся программно доступной процессорной

памятью. Обращение к расширенной ОП осуществляется постранично (4К), для

чего введены дополнительные команды с адресацией страниц. Основное

назначение расширенной ОП - буферизация страниц, перемещаемых между

внутренней и внешней памятью в процессах, связанных с виртуализацией

памяти.

Система 370 с архитектурой ESA (ESA/370) дополнена шестнадцатью 32-

разрядными регистрами доступа (Access Register - AR). В дополнение к двум

ранее введенным способам формирования адресных пространств Система 370

поддерживала два новых: базовое (home) адресное пространство и режим

регистров доступа (Access Register Mode). Базовое адресное пространство

использовалось управляющими программами операционной системы и

прикладными программами для хранения команд и данных. В режиме

регистров доступа программы размещались в главном адресном пространстве, а

данные - в адресных пространствах, определяемых регистрами доступа.

Каждый регистр доступа содержал ссылку на отдельное адресное пространство,

а выбор регистра определялся базовым регистром команды. Помимо этого

модели IBM 9370, продолжившие линейку ESA/370, были рассчитаны на

работу в сетях IBM.

Система 390 с архитектурой ESA (ESA/390) поддерживала программную

совместимость с предыдущими моделями и включала новые архитектурные

решения, такие, как последовательные оптические интерфейсы ввода-вывода

(Enterprise System CONection - ESCON и FIber CONnection - FICON),

криптографические средства, сетевые средства OSA для подключения серверов

к сетям различных типов. Были разработаны многомашинные комплексы с

использованием технологии параллельного сисплекса (Parallel Sysplex) на

основе специализированных серверов, для их объединения (coupling facility).

Расширенная архитектура ESAME, или z/Architecture, основана на 64-разрядной

адресации с сохранением совместимости с архитектурами на базе 24- и 31-

разрядной адресации. Разрядность регистров GR, CR увеличена до 64, слово

состояния PSW расширено до 128 разрядов, введены учетверенные слова-

241

операнды. Состав системы команд расширен командами с 64-разрядным и

смешанными способами адресации.

При разработке IBM eServer использовался широкий спектр новых решений,

сформулированных в проекте eLiza, который трансформировался впоследствии

в стратегическую инициативу компании IBM - программу построения

самонастраивающихся (самоорганизующихся) систем (Autonomic Computing).

Название проекта - eLiza, сокращение от electronic Lizard ("электронная

ящерица"), подчеркивает, с одной стороны, уровень компьютерного

интеллекта, сопоставимого с интеллектом живых существ, а с другой стороны -

самоорганизацию системы в критических ситуациях, возникающих как при

внутренних сбоях, так и вследствие неблагоприятных воздействий: атак

хакеров, резкого увеличения потока заявок, стихийных бедствий и т.д. В основу

систем положен принцип саморегуляции, позаимствованный из живой

природы. Проблемы самоорганизации вычислений, решаемые проектом eLiza,

сочетаются с задачами Grid-вычислений (Grid computing), и эти инициативы

развиваются согласованно. Технология Grid-вычислений позволяет

виртуализировать ресурсы и данные для распределенных вычислений, такие,

как процессорные мощности, полоса пропускания сети, емкость запоминающих

устройств. Это позволяет оптимально распределять ресурсы системы,

предоставляя их по мере необходимости.

Основными целями создания самонастраивающихся систем являются:

создание интеллектуальных механизмов внутренней самоорганизации

вычислительных систем;

обеспечение динамической адаптации вычислительных систем к условиям

деловой активности предприятия.

Для реализации указанных целей предлагается использовать четыре основных

принципа.

1. Автоматическая конфигурация (Self-configuring)

Данный механизм включает автоматическое определение новых аппаратных

ресурсов и их динамическое распределение средствами операционной системы.

В процессе функционирования системы вследствие сбоев в работе

оборудования, ошибок в программном обеспечении, уточнения внешних

требований изменяются параметры и состояния аппаратных средств, что может

стать причиной для автоматического перераспределения ресурсов системы.

При этом сохраняется возможность конфигурации аппаратных ресурсов по

требованию администраторов, обслуживающего персонала или программы,

осуществляющей управление аппаратными ресурсами.

2. Автоматическое восстановление (Self-healing)

242

Механизм самовосстановления предназначен для обнаружения и локализации

сбоев, возникающих в работе аппаратных и программных средств, а также для

минимизации возможных последствий сбоев и отказов и сохранения

работоспособности системы на необходимом уровне.

3. Автоматическая оптимизация (Self-optimizing)

Механизм оптимизации определяет текущую нагрузку на различные ресурсы

системы и при необходимости включает механизм автоматической

конфигурации ресурсов для достижения максимальной производительности и

эффективности.

4. Самозащита (Self-protecting)

Данный механизм обеспечивает защиту системы от внутренних и внешних

атак, угрожающих целостности и конфиденциальности приложений и данных.

Большинство современных серверов IBM eServer уже обладают признаками,

соответствующими принципам построения самонастраивающихся систем:

многопроцессорная, многоузловая реализация с включением процессоров

разных типов;

практически неограниченные возможности масштабирования серверов и их

консолидация;

наращивание ресурсов по требованию;

обеспечение логического разделения - партиций, при котором один сервер

представляется в виде нескольких отдельных виртуальных компьютеров с

разными операционными средами и единым центром управления и средствами

взаимодействия;

широкий спектр средств контроля и восстановления работоспособности;

гарантии высочайшего уровня готовности;

минимизация эксплуатационных затрат.

Мэйнфреймы zSeries образуют одну из линеек серверов eServer.

Название zSeries, как и z/Architecture, включает сокращение от "zero down time",

означающее нулевое время простоя, что отражает одно из главных качеств

сервера - высочайшую надежность, позволяющую непрерывно поддерживать

работу сервера на заданном уровне производительности по схеме 7 × 24 (т.е. 24

часа в сутки) × 365 (дней). Это достигается благодаря централизации

вычислительной мощности в рамках одного сервера с развитой системой

контроля и возможностью "горячей" замены отказавших элементов.

К другим важным характеристикам серверов zSeries можно отнести:

243

Масштабируемость архитектуры сервера по количеству процессоров, объему

памяти, средствам ввода-вывода и другим параметрам. Это позволяет

оперативно наращивать вычислительную мощность, пропускную способность

ввода-вывода и другие характеристики, как по запросу пользователей, так и

автоматически при возникновении критических нагрузок.

Высокая концентрация вычислительной мощности достигается за счет

использования КМОП - интегральной технологии и многочиповых модулей -

MultiСhip Module (MCM). Каждый такой модуль может содержать несколько

десятков интегральных чипов микропроцессоров, КЭШ-памяти, управления и

обмена, а также все соединения между ними в относительно небольшом

корпусе размером примерно 12×12 см. Один или несколько таких MCM-

модулей полностью обеспечивают вычислительную мощность центральной

части или ядра сервера.

Высокая пропускная способность системы ввода-вывода (около 200 GB/s)

обеспечивается большим числом разнообразных высокоскоростных каналов,

управляемых специализированными процессорами. Такие процессоры

выполняют канальные программы, находящиеся в основной памяти и

реализующие операции ввода-вывода. Это позволяет, с одной стороны,

освободить центральные процессоры от большинства рутинных и медленных

операций, связанных с вводом-выводом, а с другой стороны, распараллелить

выполнение таких операций.

Кластеризация серверов zSeries позволяет создавать системы IBM Parallel

Sysplex, в которых могут быть консолидированы серверы разных поколений.

Кластеры существенно расширяют масштабируемость систем, обладают

повышенной готовностью, динамически перераспределяют пиковые нагрузки,

позволяют сохранить преемственность при замене серверов и т.д.

Серверы zSeries в наибольшей степени отвечают концепции

самонастраивающихся систем и реализуют многие из зафиксированных в ней

технологий.

В 90-х годах прошлого века сложилось впечатление, что все задачи можно

решить при помощи персональных компьютеров, объединенных в сеть. Однако,

как мы можем убедиться сегодня, мэйнфреймы не сдают позиций.

Персональные компьютеры расширили область применения вычислительной

техники в бизнесе и в быту, однако ряд задач по-прежнему невозможно решить

без мэйнфреймов. Мэйнфреймы используются в критически важных областях

деятельности компаний, там, где требуется высокая производительность и

надежность. Они нашли свое место в эпоху Internet. Сроки их службы

исчисляются десятилетиями. Интерес к мэйнфреймам вновь растет.

Развитие и совершенствование операционных систем (ОС) для мэйнфреймов

шло по нескольким направлениям. Первое направление ведет свою историю от

операционной системы OS/360 и c начала 70-х годов базируется на технологии

управления памятью MVS (Multiple Virtual Storage). Данное направление,

244

позиционируемое IBM как стратегическое, включает наиболее популярные и

широко используемые сегодня операционные системы OS/390, z/OS и z/OS.e.

Другие ветви эволюции операционных систем также не стали тупиковыми.

Среди них семейство операционных систем, построенных на основе концепции

"виртуальных машин". К этому семейству относится z/VM, которая дает

возможность запускать на мэйнфрейме сотни образов различных ОС, включая

z/OS. Для малых и средних по мощности конфигураций мэйнфреймов по-

прежнему используется операционная система VSE, начавшая свою историю с

первой версии, известной под названием DOS.

В 1999 году родилось новое направление, связанное с созданием

ориентированных на мэйнфрейм версий популярной операционной системы

Linux. Это неординарное решение дает возможность перенести на серверы IBM

существующие приложения и системы, работающие в среде Linux, что в

совокупности с z/VM и z/OS позволяет создавать гибкие, легко

масштабируемые и в то же время мощные и защищенные информационные

системы на базе мэйнфреймов.

245

Базовая архитектура zSeries

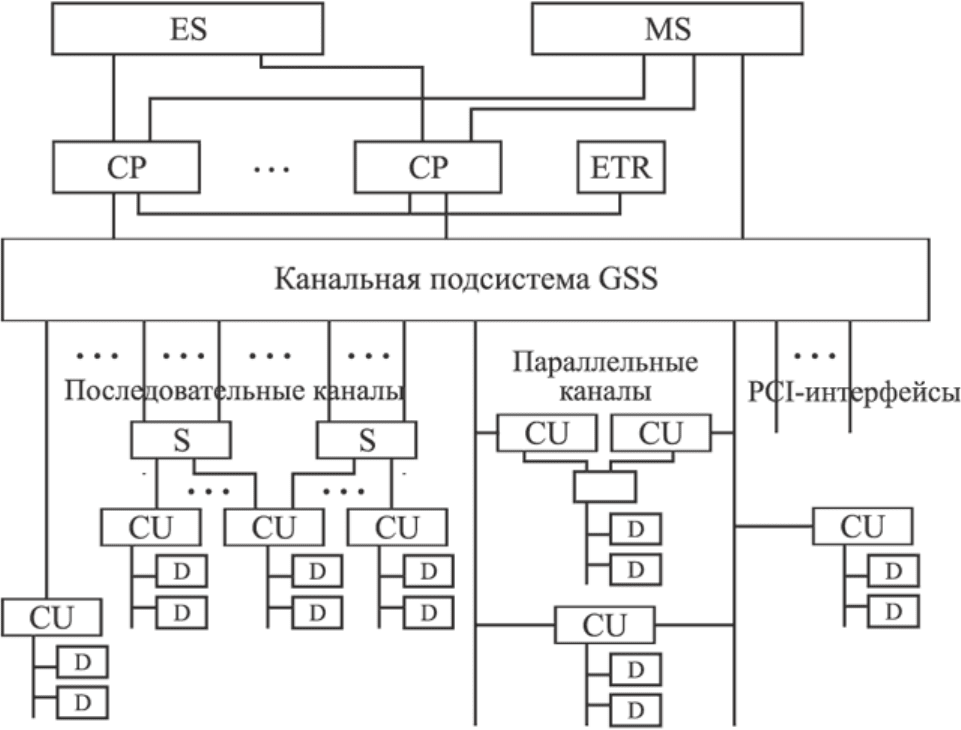

Основными компонентами z/Architecture серверов zSeries на уровне

программистской модели являются:

один или несколько центральных процессоров (Central Processor - CP);

основная память (Main Storage - MS);

расширенная память (Expanded Storage - ES);

внешний таймер (External Time Reference - ETR);

канальная подсистема (Channel Subsystem - CSS);

контроллеры (Control Unit - CU) периферийных устройств (I/O Device - D)

канальные пути или каналы, соединяющие канальную подсистему с CU

периферийных устройств, и средства их коммутации (S).

Различные генерации моделей z/Architecture отличаются качественными и

количественными характеристиками перечисленных компонентов. Основными

направлениями развития архитектуры являлись: увеличение

производительности, распараллеливание вычислительного процесса,

расширение адресного пространства памяти, увеличение пропускной

способности подсистемы ввода-вывода, повышение надежности и др. При этом

246

на всем протяжении развития z/Architecture сохранялась полная программная

совместимость "снизу-вверх".

Процессоры разных генераций отличаются физической реализацией,

быстродействием и другими параметрами, но имеют единую программисткую

модель, являющуюся базовой платформой программной совместимости всех

моделей. Основу такой модели составляет универсальная регистровая модель и

единая система команд процессоров. По мере развития регистровая модель

расширялась путем введения новых и расширения разрядности

использовавшихся ранее регистров. Пополнялся и список команд, реализуемых

процессором, с сохранением программной совместимости "снизу-вверх". В

зависимости от моделей процессор дополнялся криптографическими и другими

возможностями, встроенными как на уровне команд, так и в виде внешнего

сопроцессора.

Каждый из процессоров z/Architecture взаимодействует с основной памятью,

где хранятся команды и данные исполняемых программ. Подключение

процессоров к памяти выполняется по симметричной схеме, соответствующей

SMP-архитектуре. Расширенная память также программно доступна для

процессоров и используется для буферизации страниц при обмене с дисковой

памятью. Ко всем процессорам может быть подключен внешний таймер для

согласованного отсчета времени.

Взаимодействие процессоров и памяти с периферийными устройствами

осуществляется через канальную подсистему ввода-вывода, включающую

канальные пути разного типа. Основными типами канальных путей являются

различные последовательные каналы, параллельный канал, аналогичный

использовавшимся в системах S/360, S/370, а также универсальный интерфейс

PCI (Peripheral Component Interconnect). К канальным путям подключаются

контроллеры CU, через которые осуществляется связь с периферийными

устройствами. Последовательные каналы могут быть подключены к

устройствам через коммутаторы (S) каналов, что позволяет создавать

множественные канальные пути к устройствам. В зависимости от требований

пользователя в подсистеме ввода-вывода может быть использовано разное

количество канальных путей и CU с различными способами их подключения.

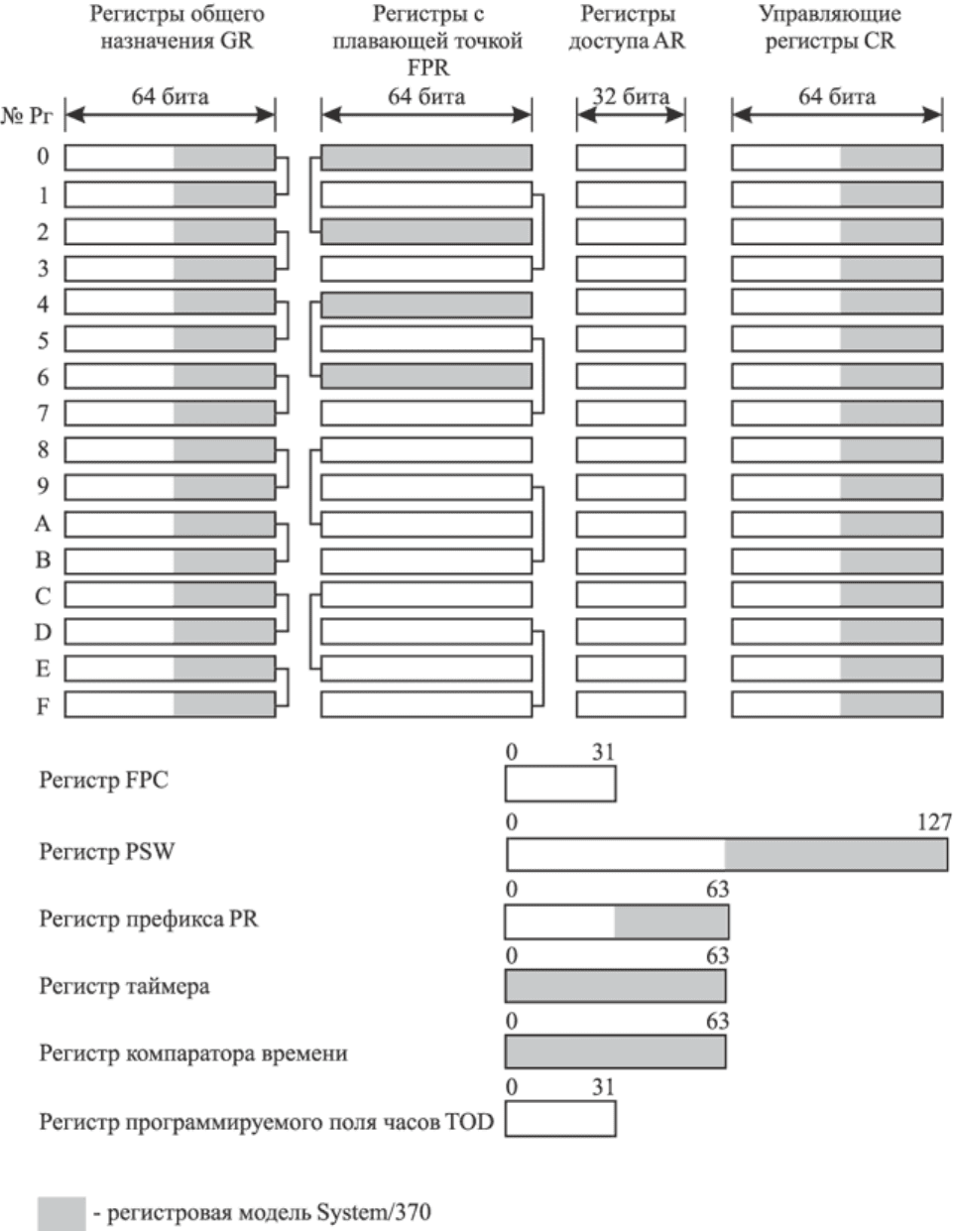

Регистровая модель

Регистровая модель процессора z/Architecture на современном этапе развития

[2.1] включает следующие группы регистров:

16 64-разрядных регистров общего назначения (General Registers GR);

16 64-разрядных регистров с плавающей точкой (Floating Point Register - FPR);

32-разрядный регистр управления операциями с плавающей точкой (Floating

Point Control Register - FPC);

16 32-разрядных регистров доступа (Access Registers - AR);

247

16 64-разрядных управляющих регистров (Control Register - CR);

128-разрядный регистр слова состояния программы (Program Status Word -

PSW);

64-разрядный регистр префикса (Prefix Register - PR);

32-разрядный программируемый регистр часов (Time-of-Day (TOD)

Programmable Register);

64-разрядный регистр таймера;

64-разрядный регистр компаратора времени (Clock Comparator).

248

Регистры GR предназначены для хранения операндов и адресов основных

арифметических, логических и других операций. Каждый из регистров имеет

разрядность 64 бита и адресуется в командах 4-разрядным полем R. В

зависимости от реализуемой модели используются 32 (биты 32-63) или 64

разряда регистров. На рис. 2.2 показан пример использования модели для

249

архитектуры System/370. Два регистра GR с соседними адресами могут служить

для хранения операндов удвоенной длины 64 или 128 бит (см. дуги на рис. 2.2).

В первом случае объединяются биты 32÷63, а во втором - биты 0÷63 соседних

регистров. Удвоенный операнд начинается с четного адреса, по которому

размещается старшая половина операнда. Часть команд со сложными

способами адресации используют регистры GR в качестве базовых и индексных

регистров. Четырехразрядные поля B и Х в командах определяют,

соответственно, один из 15 базовых или индексных регистров (при В=0

базирование, а при Х=0 индексация не используются). В некоторых командах

применение регистров GR подразумевается без явного указания их адресов в

полях команды.

Регистры FPR предназначены для хранения 32- или 64-разрядных чисел в

форматах с плавающей точкой: двоичном (Binary Floating Point - BFP) или

шестнадцатеричном (Hexadecimal Floating Point - HFP). Как и GR, регистры

FPR адресуются в командах 4-разрядными полями R и могут быть попарно

объединены для хранения расширенных до 128 бит операндов, адресуемых

младшим из адресов объединенных регистров. Для задания параметров

операций с плавающей точкой используется дополнительный управляющий

регистр FPC.

Шестнадцать регистров доступа AR применяются в механизме динамического

преобразования адресов для хранения косвенной ссылки на используемое

адресное пространство. В режиме адресации с использованием AR (Access

Register Mode) поле В (или R) команд задает номер AR, содержимое которого

используется как ссылка на адресное пространство. Указание в команде на

регистр доступа с номером 0 подтверждает использование текущего адресного

пространства, а AR1/AR 15 задают новое адресное пространство.

Управляющие регистры CR адресуются как полем R, так и по умолчанию в

различных командах, и используются при исполнении команд и функций

процессора. Управляющие поля и отдельные биты регистров закреплены за

конкретными средствами, такими как динамическое преобразование адресов,

регистрация программных событий и др. и содержат информацию,

необходимую для функционирования таких средств. С помощью команд

загрузки и чтения можно обратиться как к отдельному регистру, так и к группе

регистров.

Регистр слова состояния программы PSW, как и управляющий регистр,

содержит управляющие поля и биты, основными из которых являются адрес

команды (программный счетчик), признаки результата операции (код условия),

определяющие состояние процессора. При выполнении прерывающей

процедуры текущее (или старое) PSW сохраняется в фиксированной зоне

начальных адресов памяти, а новое PSW, соответствующее прерыванию,

перемещается из памяти в регистр PSW.

250