Хмелевский И.В., Битюцкий В.П. Организация ЭВМ и систем. Однопроцессорные ЭВМ. Часть 3

Подождите немного. Документ загружается.

80

ECP (Enhanced Capability Port – порт с расширенными возможностями) – интел-

лектуальный вариант EPP. Реализованы возможность разделения передаваемой

информации на команды и данные, а также поддержка DMA и сжатия передаваемых

данных методом RLE (Run-Length Encoding – кодирование повторяющихся серий).

COM порт – последовательный порт. Скорость обмена до 115 Кбит/с. Возможно

подключение лишь одного устройства к порту. В основном используется для под-

ключения манипулятора типа «мышь» или модема. Стандартно в материнскую плату

встроено два последовательных порта.

PS/2 порт – последовательный порт. Является функциональным аналогом

COM- порта, но имеет дополнительно линии для питания подключаемых устройств.

Служит для подключения клавиатуры или манипулятора типа «мышь».

РАЗЪЕМЫ ДЛЯ ПОДКЛЮЧЕНИЯ ДИСКОВЫХ УСТРОЙСТВ

FDD (Floppy Disk Drivers – накопитель на гибких магнитных дисках) конструктив-

но представляет собой 12х2-контактный игольчатый разъем с возможностью под-

ключения двух дисководов. Устройство, подключенное к перевитому шлейфу, явля-

ется диском A:, к прямому – B:. Реализовано одновременное обращение только к

одному устройству.

HDD (Hard Disk Drivers – накопитель на жестких магнитных дисках) – конструк-

тивно может быть выполнен в нескольких вариантах. Обычно это IDE или SCSI.

IDE (Integrated Drive Electronics) – более дешевый и в настоящее время самый

распространенный интерфейс. Конструктивно представляет собой 2х20-контактный

игольчатый разъем. Стандартно контроллер IDE имеет один такой разъем, к которо-

му можно подключить до двух дисковых устройств. Стандартно на материнской пла-

те собраны 2 IDE контроллера Primary и Secondary. Существуют также несколько

протоколов обмена данными: UDMA/33 – 33 Мбайт/с и UDMA/66 – 66 Мбайт/с.

Про-

токол UDMA/66 обладает вдвое большей скоростью передачи данных за счет того,

что данные передаются по обоим фронтам тактирующего сигнала в отличие от

UDMA/33. Для реализации интерфейса необходим шлейф, в котором бы отсутство-

вали помехи от двух параллельно идущих проводников. Для решения этой пробле-

мы применяется 80-жильный шлейф, каждый второй проводник которого

соединен с

общим проводом для уменьшения помех.

SCSI (Small Computer System Interface) – более дорогой и в настоящее время

менее распространенный интерфейс. Один контроллер может обслуживать от 1 до

32 устройств в зависимости от конструкции. Контроллер SCSI внешне представляет

собой либо плату расширения, либо устройство, встроенное в материнскую плату. В

последнем случае мы можем видеть лишь 25х2-контактный игольчатый разъем.

Скорость обмена по каналу SCSI до 20 Мбайт

/с.

UWSCSI (Ultra Wide SCSI) является модификацией интерфейса SCSI. Внешне

также представляет собой плату расширения или устройство, встроенное в мате-

ринскую плату, и тогда мы можем видеть 34х2-контактный трапецеидальный разъем

плюс для поддержки SCSI 25x2-контактный игольчатый разъем. Скорость обмена по

каналу UWSCSI до 80 Мбайт/с.

РАЗЪЕМЫ ПРОЦЕССОРОВ

Собственно говоря, процессор как раз то устройство, которое производит все

вычисления и управляет всеми контроллерами. Так как же определить, какой про-

цессор вы сможете поставить в ту материнскую плату, которую выбрали? На данный

момент существует достаточно много типов разъемов для установки процессора.

Это Socket 7, Socket 370, Socket FC-PGA, Slot I, Slot A. Среди такого количества не-

сложно и запутаться, но

не волнуйтесь, сейчас все подробно разберем.

81

Тип разъемов Socket-ZIF (Zero Input Force – вставляй, не прикладывая сил) кон-

структивно представляет пластиковый разъем с зажимающей защелкой, располо-

женной сбоку корпуса разъема, предназначенной для предотвращения самопроиз-

вольного выпадения процессора. При установке процессора защелка должна быть

максимально поднята вверх.

Разъем

Socket 7 – стандартный ZIF (Zero Input Force) – разъемом с 296 контак-

тами, использующийся всеми процессорами класса Р5 – Intel Pentium, AMD K5 и K6,

Cyrix 6x86 и 6x86MX и Centaur Technology IDT-C6.

Разъем

Socket 8 – нестандартный ZIF– имеет 387 контактов и несовместим с

Socket 7, предназначен для установки в него процессора класса Р6 – Pentium Pro.

Поскольку ядро процессора и кэш были объединены на одном кристалле, то и фор-

ма его получилась прямоугольной, а не квадратной, как у Socket 7.

Разъем

Socket 370 – нестандартный ZIF– несовместим ни с Socket 7, ни с

Socket 8, предназначен для установки в него более дешевого прототипа P6 Celeron,

за исключением последней модели Celeron II, построенной по технологии

Coppermine.

Разъем

Socket FC-PGA (Flip Chip Pin Grid Array) внешне напоминает Socket 370.

В отличие от 370 на FC-PGA заводится два питания 1,5В и 1,6В, и предназначен он

для установки в него процессоров, произведенных по технологии Coppermine.

Тип разъема Slot конструктивно представляет пластиковый разъем с двумя ря-

дами контактов, в него вставляются процессоры с ножевым разъемом. Фирма INTEL

пошла на это в связи с тем, что для удешевления стоимости процессора кэш был

вынесен с кристалла и стал располагаться на плате процессора, которая имеет но-

жевой двухсторонний разъем.

Тип разъема

Slot I предназначен для установки в него процессора

P6 Pentium II, Pentium III и процессора P6 Celeron Slot I.

Тип разъема

Slot 2 отличается от Slot I по коммерческим причинам, так как в

него ставятся более дорогие модели процессоров Xeon, стоимость которых во много

раз превышает стоимость процессоров Pentium II и Pentium III.

Тип разъема

Slot A практически тот же самый Slot I, только перевернутый на-

оборот. Предназначен для установки процессора Athlon от AMD.

ВОПРОСЫ ДЛЯ САМОПРОВЕРКИ

1. Почему в процессе эволюции ЭВМ оказалось недостаточным использование

одной системной магистрали?

2. Что понимается под термином "шина расширения"?

3. Опишите назначение локальной системной шины.

4. Для чего предназначена шина процессора?

5. Чем определяется скорость передачи данных по шине?

6. Из чего складывается пропускная способность шины?

7. Для чего предназначена шина памяти?

8. Опишите стандарт

шины расширения ISA.

9. Чему равна пропускная способность шины ISA?

10. Шина расширения МСА. Ее назначение и основные характеристики.

11. Почему ШР МСА не получила распространение?

12. В чем сходство и отличия ШР ISA и EISA?

13. Что такое "локальная шина"?

14. Локальная шина VLB. Ее особенности.

15. Перечислите возможности шины PCI.

16. Назовите функции главного моста.

82

КОНТРОЛЬНЫЕ ЗАДАНИЯ

1. На листах ответа должны быть указаны номер группы, фамилия студента и

номер его варианта.

2. Номера вопросов выбираются студентом в соответствии с двумя последни-

ми цифрами в его зачетной книжке. В табл. 10.1 а

n-1

– это предпоследняя циф-

ра номера, а

n

– последняя цифра. В клетках таблицы стоят номера вопросов,

на которые необходимо дать письменный ответ.

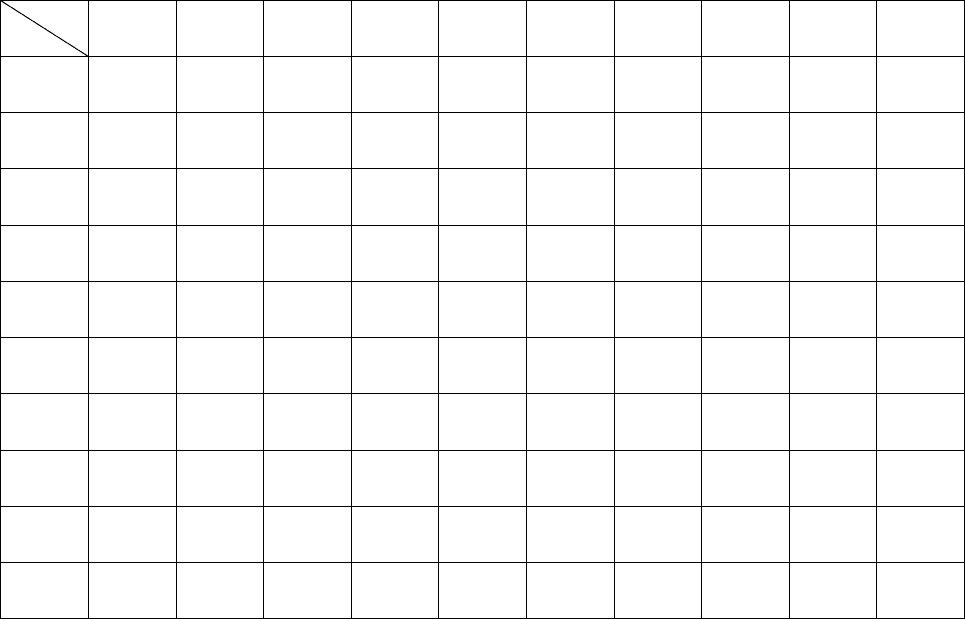

Номера вопросов Таблица 10.1

a

n

a

n-1

0 1 2 3 4 5 6 7 8 9

0

1,7,10,

13

2,8,11,

14

3,9,12,

15

4,7,10,

16

5,8,11,

13

6,9,12,

14

1,8,10,

15

2,9,11,

16

3,7,12,

13

4,8,10,

14

1

5,9,11,

15

6,7,12,

16

2,7,10,

15

1,9,10,

13

2,7,11,

14

3,8,12,

15

4,9,10,

16

5,7,11,

13

6,8,12,

14

5,9,12,

16

2

1,7,10,

13

2,8,11,

14

3,9,12,

15

4,7,10,

16

5,8,11,

13

6,9,12,

14

1,8,10,

15

2,9,11,

16

3,7,12,

13

4,8,10,

14

3

5,9,11,

15

6,7,12,

16

2,7,10,

15

1,9,10,

13

2,7,11,

14

3,8,12,

15

4,9,10,

16

5,7,11,

13

6,8,12,

14

5,9,12,

16

4

1,7,10,

13

2,8,11,

14

3,9,12,

15

4,7,10,

16

5,8,11,

13

6,9,12,

14

1,8,10,

15

2,9,11,

16

3,7,12,

13

4,8,10,

14

5

5,9,11,

15

6,7,12,

16

2,7,10,

15

1,9,10,

13

2,7,11,

14

3,8,12,

15

4,9,10,

16

5,7,11,

13

6,8,12,

14

5,9,12,

16

6

1,7,10,

13

2,8,11,

14

3,9,12,

15

4,7,10,

16

5,8,11,

13

6,9,12,

14

1,8,10,

15

2,9,11,

16

3,7,12,

13

4,8,10,

14

7

5,9,11,

15

6,7,12,

16

2,7,10,

15

1,9,10,

13

2,7,11,

14

3,8,12,

15

4,9,10,

16

5,7,11,

13

6,8,12,

14

5,9,12,

16

8

1,7,10,

13

2,8,11,

14

3,9,12,

15

4,7,10,

16

5,8,11,

13

6,9,12,

14

1,8,10,

15

2,9,11,

16

3,7,12,

13

4,8,10,

14

9

5,9,11,

15

6,7,12,

16

2,7,10,

15

1,9,10,

13

2,7,11,

14

3,8,12,

15

4,9,10,

16

5,7,11,

13

6,8,12,

14

5,9,12,

16

11. ПРИНЦИПЫ ОРГАНИЗАЦИИ СИСТЕМ

ПРЯМОГО ДОСТУПА К ПАМЯТИ

Материал, изложенный в предыдущих разделах, предполагал, что передача

данных между ОП и ПУ, как правило, осуществляется с помощью процессора. Это

так называемая

программно-управляемая передача данных (программно-управля-

емый ввод/вывод

), которая осуществляется при непосредственном участии и под

управлением процессора. В англоязычной литературе – Programmed Input/Output

(PIO). Процессор при этом выполняет соответствующую процедуру ввода/вывода

(ВВ), являющуюся либо частью основной программы, либо оформленную как под-

программа. Данные между ОП и ПУ пересылаются через процессор. Операции ВВ

инициируются текущей командой программы или запросом прерывания от

ПУ. Это

соответствует принципам функционирования классической неймановской машины,

описание которой приведено в гл.1. Более подробно процедура программно-

управляемой передачи данных (программно-управляемого ВВ) рассмотрена в гл. 9.

Между тем такой вариант обмена между ОП и ПУ во многих случаях является

далеко не самым оптимальным, а иногда вообще невозможным. Причин тому не-

сколько

. Рассмотрим очень коротко основные из них.

83

• При программно-управляемом ВВ процессор "отвлекается" от выполнения

основной программы решения задачи. Операции ВВ достаточно просты, чтобы

эффективно загружать логически сложную быстродействующую аппаратуру

процессора. В результате при использовании программно-управляемого ВВ

снижается производительность ЭВМ в целом.

• При пересылке любой единицы данных (байт, слово) процессор выполняет

достаточно много команд,

чтобы обеспечить буферизацию данных, преобразо-

вание форматов, подсчет количества переданных единиц данных, формирова-

ние адресов памяти и регистров ПУ. В результате скорость передачи данных

при программно-управляемом ВВ (т.е. через процессор) может оказаться не-

достаточной для работы с высокоскоростными ПУ, например с накопителями на

жестких дисках, видеосистемами, быстродействующими аналого-цифровыми

и

цифро-аналоговыми преобразователями различного назначения, и т.д.

• Большинство современных сложных ПУ, таких как видеосистемы, сетевые

карты, жесткие диски и т.д., осуществляют обмен с ОП целыми блоками ин-

формации. В этом случае перечисленные выше непроизводительные времен-

ные затраты процессора становятся особенно существенными.

• Обмен в режиме прерывания,

несмотря на все свои достоинства (см. гл. 6),

требует еще помимо перечисленных выше непроизводительных временных за-

трат время на сохранение вектора состояния текущей программы в стеке и его

последующего восстановления. Кроме того, прерывание в большинстве случа-

ев возможно только после завершения текущей команды.

Несмотря на широкое использование программно-управляемого ВВ, для уско

-

рения операций обмена данными между ОП и ПУ и разгрузки процессора от управ-

ления этими операциями в современных ЭВМ используется специальный режим об-

мена, получивший название

режим прямого доступа к памяти или просто прямой

доступ к памяти (ПДП). В англоязычной литературе – Direct Memory Access (DMA).

Ниже, в зависимости от контекста излагаемого материала, будут употребляться обе

аббревиатуры – ПДП и DMA.

Прямым доступом к памяти называется режим, при котором обмен данными

между ОП и регистрами ПУ осуществляется без участия центрального процессора

за счет специальных, внешних по отношению к нему, электронных схем. Простейший

вариант такого обмена рассмотрен в гл. 9.

Введение режима ПДП (реализация каналов ПДП) всегда усложняет аппарат-

ную часть ЭВМ, однако позволяет повысить скорость выполнения операций обмена

ОП-ПУ, разгружает центральный процессор от обслуживания операций ВВ, повыша-

ет общую производительность ЭВМ. При наличии кэш-памяти достаточного объема

режим ПДП в ряде случаев позволяет реализовать параллельное выполнение опе-

раций обмена и обработку команд текущей программы процессором, что также по-

вышает общую производительность ЭВМ. Более того, наличие механизма прямого

доступа к памяти позволяет поддерживать многопроцессорность вычислительной

системы. На последнем моменте необходимо остановиться более подробно.

Дело в том, что термин ПДП (как и DMA), используемый при изложении мате-

риала настоящего раздела, в общем

случае не совсем точно отражает суть процес-

сов, происходящих в ЭВМ. Точнее, прямой доступ к памяти (к ОП) является только

частным случаем организации процедур доступа к системной магистрали со стороны

множества устройств, в том числе и процессоров. Под доступом к системной магист-

рали понимается возможность какого-либо устройства, имеющего соответствующее

аппаратно

-программное обеспечение (ведущее устройство, интеллектуальное уст-

ройство магистрали), занимать на какое-то время системную магистраль и полно-

стью управлять ею, вырабатывая все необходимые управляющие сигналы. При этом

могут осуществляться связи не только ОП-ПУ, но и ПУ-ПУ. Между тем смысл поня-

84

тия "память" можно расширить и понимать под памятью не только ОП, но и адресуе-

мые регистры ПУ. В этом случае использование термина ПДП (как и DMA) будет

вполне корректно.

Следует иметь в виду, что термин "периферийное устройство (ПУ)" здесь ис-

пользуется достаточно условно. В англоязычной литературе ведущее устройство

магистрали, инициирующее обмен,

принято называть master. Устройство, к которому

обращается master, является подчиненным, и его принято называть

slave. Таким об-

разом, более правильно говорить о реализации связей master-slave (M-S), а не ПУ-

ПУ или ОП-ПУ. Мастером может быть только интеллектуальное устройство, имею-

щее средства управления магистралью (СУМ), которые, как минимум, должны

"уметь" формировать и модифицировать адреса обращения, вести контроль за раз-

мером переданного блока информации и генерировать управляющие сигналы

маги-

страли. Между тем в зависимости от текущего состояния вычислительного процесса

одно и то же интеллектуальное устройство магистрали может выступать и как

master, и как slave. Устройства магистрали, не имеющие СУМ, всегда являются под-

чиненными, т.е. slave.

Естественно, что предоставление магистрали в распоряжение того или иного

устройства (захват магистрали) может происходить только

на приоритетной основе.

Эта процедура получила название

арбитраж магистрали, а устройство, ее реали-

зующее, –

арбитр магистрали. В ряде случаев арбитр может строиться как отдель-

ное устройство, размещенное на системной магистрали. В других случаях арбитраж

магистрали выполняет сам процессор. Наличие процедуры арбитража позволяет

размещать на системной магистрали несколько интеллектуальных устройств, в том

числе и процессоров. В соответствии с принятой дисциплиной обслуживания (арбит-

ража) каждое из них будет

получать в свое распоряжение системную магистраль и

устанавливать связи как с ОП, так и с регистрами других устройств магистрали. Сле-

дует отметить при этом, что в процедуре арбитража всегда предусматриваются

средства, предотвращающие монопольный захват магистрали одним устройством.

Часть этих средств может быть сосредоточена в арбитре, другая часть может быть

распределена между

устройствами магистрали, использующими режим ПДП.

11.1. СПОСОБЫ ОРГАНИЗАЦИИ ДОСТУПА К СИСТЕМНОЙ МАГИСТРАЛИ

Конкретные варианты процедур доступа ведущих устройств к магистрали (орга-

низации каналов ПДП) в различных ЭВМ очень разнообразны. Между тем сущест-

вуют некоторые общие принципы их реализации. В общем случае для устройств, ис-

пользующих ПДП (DMA), выделяют два основных принципа организации доступа, в

соответствии с которыми выделяют два типа систем ПДП (DMA).

Пассивный доступ или slave DMA. При этом способе доступа все устройства,

использующие режим DMA, являются slave и обслуживаются одним специальным

контроллером DMA (ПДП), размещенным на системной магистрали, т.е. одним ве-

дущим устройством, – master. Такой способ доступа позволяет реализовать только

связи ПУ-ОП. Контроллер DMA включает в себя арбитр магистрали и соответствую-

щие СУМ. В этом случае ПУ играют пассивную роль и осуществляют обмен с ОП по

сигналам, формируемым контроллером DMA, т.е. аналогично тому, как

это происхо-

дит при обмене через процессор.

Как уже отмечалось выше, контроллер DMA обслуживает несколько ПУ, т.е.

поддерживает несколько каналов ПДП. Перед началом обмена контроллер должен

быть инициализирован. Для этого в его регистры необходимо загрузить начальный

адрес области ОП, с которой ведется обмен, размер передаваемого блока инфор-

мации для каждого канала

, направление и режим передачи, дисциплину арбитража.

В общем случае инициализация контроллера может осуществляться по мере необ-

ходимости (многократно) в процессе обработки текущей программы. Однако уста-

85

новка дисциплины арбитража в абсолютном большинстве случаев осуществляется

один раз, при запуске вычислительной системы на решение конкретной задачи.

Таким образом, slave DMA не требует существенного усложнения аппаратуры

устройств магистрали, а следовательно, и увеличения их стоимости. Каждое устрой-

ство, использующее такой режим обмена, должно иметь только аппаратуру форми-

рования сигнала запроса ПДП (запросчик).

При этом контроллер DMA является дос-

таточно сложным и дорогим устройством, которое можно считать сопроцессором

ввода/вывода, разгружающим центральный процессор от рутинных операций обме-

на (т.е. контроллер ПДП является очень упрощенным вариантом канальных процес-

соров мэйнфреймов, описанных в гл. 1).

Исторически системы slave DMA появились первыми. В частности, система

ПДП такого типа использовалась первоначально

на магистрали ISA в компьютерах

PC/XT фирмы IBM. Многочисленные варианты систем slave DMA используются и в

настоящее время в универсальных и управляющих ЭВМ самой разной архитектуры,

назначения и производительности.

Активный доступ, или bus master DMA. При этом способе доступа предполага-

ется, что устройства, использующие режим DMA, имеют программно-аппаратные

средства, способные управлять магистралью (осуществлять прямое управление ма-

гистралью, или

bus mastering), а следовательно, и реализовывать любые связи типа

master-slave (M-S). Такие устройства магистрали могут выступать как master, поэто-

му единый контроллер DMA отсутствует. Остается только арбитр магистрали, кото-

рый по определенной дисциплине предоставляет магистраль в распоряжение того

или иного устройства. Арбитр может быть выполнен как отдельное устройство, раз-

мещенное на магистрали, либо арбитражем магистрали может

заниматься процес-

сор. В современных IBM PC процедуры арбитража магистрали включены в функции

чипсета. При наличии нескольких процессоров арбитром может быть назначен один

из них.

Следует иметь в виду, что любое современное интеллектуальное устройство

управляется процессором (процессорами), находящимся на системной магистрали и

имеющим собственную шину расширения. Такое устройство фактически является

специализированной микроЭВМ,

функционирующей по программе, обычно храня-

щейся в собственном ПЗУ. Этим оно, в сущности, только и отличается от "централь-

ного процессора (ЦП)", также находящегося на системной магистрали и обрабаты-

вающего команды текущей программы, хранящейся в ОП или системном ПЗУ. Такой

подход позволяет рассматривать "ЦП" как одно из интеллектуальных устройств ма-

гистрали, причем

"ЦП" может быть несколько. Исходя из этого, в вычислительных

системах, использующих bus mastering, можно говорить о множестве интеллектуаль-

ных устройств, приоритеты которых на использование системной магистрали для

обмена (захват магистрали) определяются только дисциплиной обслуживания, за-

груженной в арбитр при инициализации, т.е. можно говорить о многопроцессорных

вычислительных системах.

Таким образом, bus master DMA требует существенного

усложнения устройств

магистрали (наличие СУМ, более сложный запросчик), а следовательно, и увеличе-

ния их стоимости. Однако он дает возможность ускорить процессы обмена, особенно

в многозадачном режиме, и реализовать многопроцессорные варианты вычисли-

тельных систем, имеющих магистрально-модульную архитектуру.

Примером устройств с активным DMA являются контроллеры АТА (AT Attach-

ment for Disk Drivers), расположенные в современных IBM PC на магистрали PCI, в

частном случае контроллеры IDE. Активный DMA использует хост-адаптер шины

SCSI (Small Computer System Interface), связывающий шину с какой-либо внутренней

магистралью компьютера, а также контроллеры графических систем и средства их

подключения, например порт AGP (Accelerated Graphic Port) и ряд других устройств.

Примером устройств, использующих только bus master DMA (bus mastering), являют-

ся устройства вычислительных систем, построенных на базе магистрали VME (Versa

Module Eurocard).

86

Следует отметить, что в реальных вычислительных системах иногда использу-

ют оба варианта систем DMA одновременно (для разных устройств магистрали). При

этом контроллер может поддерживать несколько каналов DMA и работать в комби-

нированном режиме. Для одних устройств магистрали (slave) он может выполнять

функции контроллера DMA, а для других устройств (master) он являются только ар-

битром магистрали.

Именно такой вариант функционирования системы DMA был

реализован в PC/AT фирмы IBM.

11.2. ВОЗМОЖНЫЕ СТРУКТУРЫ СИСТЕМ ПДП

Конкретные технические реализации систем ПДП имеют множество вариантов.

Они зависят от типа системной магистрали, архитектуры ЭВМ в целом, типа исполь-

зуемого процессора, целевого назначения ЭВМ, количества устройств на магистра-

ли и т.д. В то же время они являются сложными комбинациями небольшого количе-

ства базовых структур систем ПДП. Ниже рассматриваются две

основные базовые

структуры – радиальная и цепочечная.

Радиальная структура

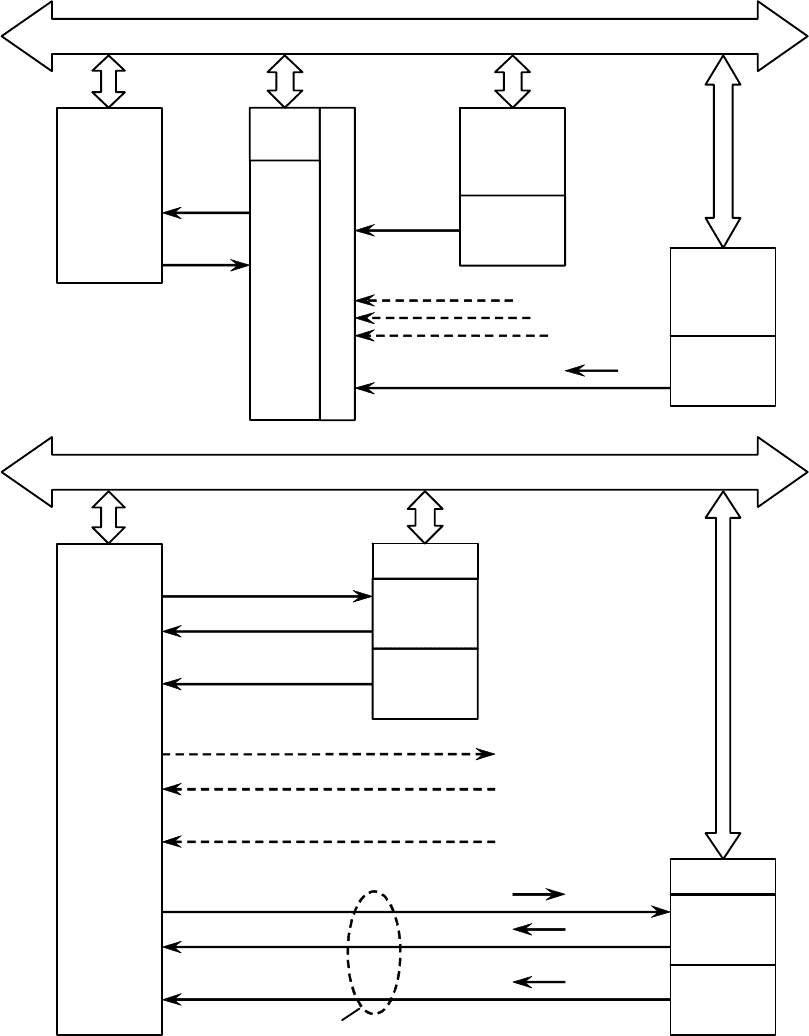

Упрощенные варианты обобщенных структур систем ПДП радиального типа

представлены на рис. 11.1.

Характерной особенностью радиальной структуры является то, что каждый

ИЗПД (в частном случае ПУ) подключен к отдельному входу контроллера ПДП

(рис. 11.1, а) или арбитра (рис. 11.1, б). Отличие двух структур состоит в том, что в

случае slave DMA для подключения ИЗПД достаточно одной

линии ЛЗПД, по которой

устройство выставляет запрос на обслуживание. В системе bus master DMA для под-

ключения устройства к арбитру необходимы, как минимум, три линии – ЛЗПД, ЛПЗ и

ЛРПД, которые можно назвать

шиной арбитража (ШАр), имеющей собственный

вход в арбитр. Каждый вход (в контроллер, в арбитр) обладает определенным уров-

нем приоритета. Число подключаемых ИЗПД определяется числом входов в кон-

троллер или арбитр. При обслуживании устройств, использующих slave DMA

(рис. 11.1, а), всем обменом управляет контроллер ПДП, обязательными компонен-

тами которого являются блок СУМ и арбитр магистрали. Устройства

магистрали пас-

сивны и должны содержать только запросчик.

При обслуживании устройств, использующих bus master DMA (рис. 11.1, б), кон-

троллер ПДП, как таковой, отсутствует и централизованно выполняется только ар-

битраж магистрали. Устройства магистрали активны, поэтому их обязательными

компонентами являются запросчик и блок СУМ (как уже отмечалось, "ЦП" в системах

bus mastering рассматривается как одно из ИЗПД

). После захвата магистраль управ-

ляется блоком СУМ конкретного устройства, ведущего обмен (master). В качестве

арбитра магистрали используется либо специализированное устройство, либо кон-

троллер ПДП, в котором функции блока СУМ отключены. Линии ЛРПД, присутст-

вующие в системе bus master DMA, предназначены для передачи сигнала РПД, по-

зволяющего активному устройству захватить магистраль. Кроме того, в системе bus

master DMA обязательно присутствуют линии ЛПЗ, сигналы которых информируют

арбитр о захвате магистрали тем или иным устройством. Сигнал ПЗ всегда выстав-

ляет master и удерживает его на линии все время, пока осуществляет обмен (управ-

ляет магистралью), поэтому сигнал всегда представлен потенциалом.

В системах радиальной структуры контроллер ПДП может работать, как было

отмечено выше,

и в комбинированном режиме, т.е. поддерживать как систему slave

DMA, так и систему bus master DMA (см. окончание п. 11.1). Запросы от ИЗПД в обе-

их системах DMA могут быть представлены как уровнем потенциала, так и его пере-

падом, поскольку поступают в контроллер или арбитр по отдельным линиям. Однако

представление запроса потенциалом более предпочтительно, поскольку система

DMA становится более устойчивой как к помехам, так и к сбоям аппаратуры. Это су-

щественно снижает вероятность пропуска запроса от ИЗПД.

87

Процес-

сор

СУМ

Арбитр

Контроллер ПДП

ИЗПД

1

Запро-

счик

ОЗПД

РПД

ИЗПД

k

Запро-

счик

ЛЗПД

1

ЛЗПД

k

ЛЗПД

i

ЗПД

k

А

Р

Б

И

Т

Р

ИЗПД

1

Запро-

счик

ЛЗПД

1

ИЗПД

k

Запро-

счик

ЛЗПД

k

ЛЗПД

i

ЛПЗ

i

СУМ

ЛПЗ

1

ЛРПД

1

СУМ

ЛПЗ

k

ЛРПД

k

ЛРПД

i

РПД

ПЗ

ЗПД

а

б

ИЗПД – источник запросов прямого доступа;

РПД – сигнал разрешения прямого доступа;

СУМ – средства управления магистралью;

ПЗ – сигнал подтверждения захвата магистрали;

ЛРПД – линия разрешения прямого доступа;

ЗПД – сигнал запроса прямого доступа;

ЛПЗ – линия подтверждения захвата магистрали;

ШАр – шина арбитража;

ОЗПД – общий сигнал запроса прямого доступа;

ЛЗПД – линия запросов прямого

доступа

Рис. 11.1. Радиальная структура системы: а – Slave DMA, б – Bus Master

ШАр

Системная магистраль

Системная магистраль

88

Основным преимуществом радиальной структуры является то, что упрощается

аппаратура арбитра магистрали, поскольку каждый ИЗПД имеет собственную ЛЗПД.

Кроме того, несколько упрощается аппаратура ИЗПД и конструкция слота даже в

случае bus master DMA, поскольку все активные устройства магистрали имеют от-

дельную шину арбитража (ШАр). Все это удешевляет радиальную систему по срав-

нению с цепочечной,

рассматриваемой ниже.

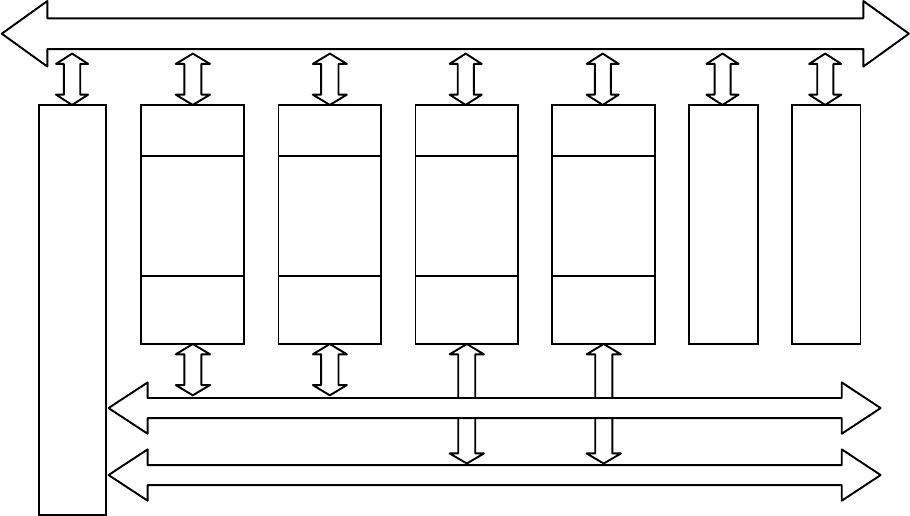

Цепочечная структура

Упрощенный вариант обобщенной структуры системы ПДП цепочечного типа

представлен на рис. 11.2.

А

Р

Б

И

Т

Р

СУМ

ИЗПД

1

Запро-

счик

СУМ

ИЗПД

2

Запро-

счик

СУМ

ИЗПД

3

Запро-

счик

СУМ

ИЗПД

4

Запро-

счик

Slave

Slave

ШАр

1

ШАр

2

Рис. 11.2. Обобщенная цепочечная структура системы Bus Master DMA

Системная магистраль

Характерной особенностью цепочечной структуры является то, что множество

активных устройств магистрали (ИЗПД), обязательными компонентами которых яв-

ляются блок СУМ и запросчик, подключены к одной или нескольким шинам арбитра-

жа (ШАр). На рис. 11.2 присутствуют две ШАр. После захвата магистраль управляет-

ся блоком СУМ конкретного устройства, ведущего обмен (master). Контроллер ПДП

отсутствует, и централизованно

выполняется только арбитраж магистрали. На

рис. 11.2 арбитр изображен как отдельное устройство магистрали, хотя, как отмече-

но выше, арбитраж может осуществлять и процессор (один из процессоров). Каждая

ШАр соответствует одному входу в арбитр и обладает собственным уровнем при-

оритета. Таким образом, ИЗПД, подключенные к разным ШАр, обладают различным

приоритетом. Пассивные устройства

магистрали (slave) к ШАр не подключены. Кро-

ме того, приоритет устройств, подключенных к одной ШАр, определяется также их

положением в цепи распространения сигнала разрешения прямого доступа (РПД).

Рассмотрим этот момент более подробно на примере одной ШАр

n

системы bus

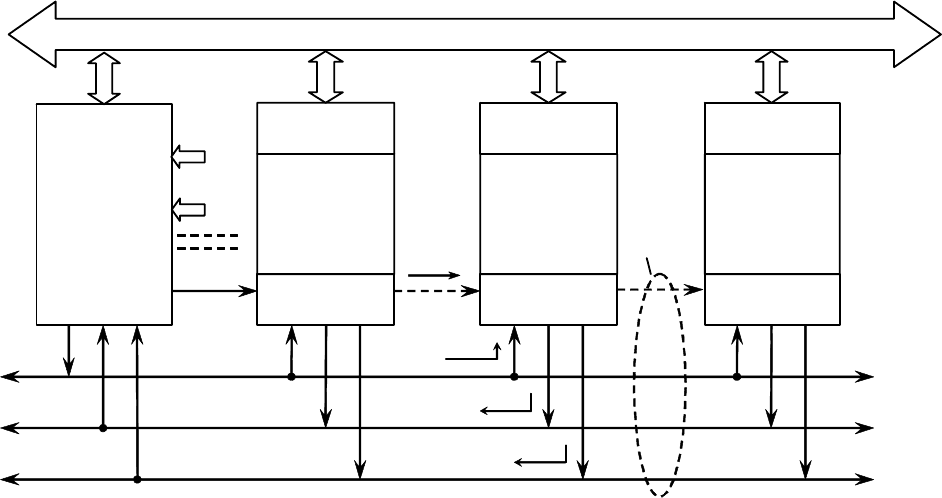

master DMA, упрощенная структура которой приведена на рис. 11.3.

Из рисунка следует, что ШАр (для упрощения обозначений здесь и ниже индекс

"n" опущен) в такой системе содержит, как минимум, четыре линии – ЛЗПД, ЛРПД,

ЛПЗ и ЛБПД. В отличие от радиальной структуры, ИЗПД магистрали подключены к

трем линиям ШАр (ЛЗПД, ЛПЗ и ЛБПД)

параллельно, поэтому запросы от ИЗПД

(сигналы ЗПД) всегда представлены уровнем потенциала. Выходные каскады аппа-

ратных средств формирования запросов в каждом ИЗПД представляют собой ключи

89

с открытым коллектором, объединенные по схеме монтажного "или". Это позволяет

исключить потерю запросов, одновременно выставленных запросчиками разных

ИЗПД на одну ЛЗПД.

Слот ”0”

Слот ”1” Слот ”i”

Слот ”k”

ШАр

2

ШАр

1

А

Р

Б

И

Т

Р

СУМ

ИЗПД

n,1

Запросчик

СУМ

ИЗПД

n,i

Запросчик

СУМ

ИЗПД

n,k

Запросчик

ЛРПД

n

РПД

n

ШАр

n

ЛБПД

n

ЛПЗ

n

ЛЗПД

n

БПД

n

ПЗ

n,i

ЗПД

n,i

ИЗПД – источник запросов прямого доступа;

СУМ – средства управления магистралью;

ЛЗПД – линия запросов прямого доступа;

ЛРПД – линия разрешения прямого доступа;

ЛПЗ – линия подтверждения захвата магистрали;

ЛБПД – линия блокировки прямого доступа;

ШАр

n

– одна из шин арбитража;

ЗПД – сигнал запроса прямого доступа;

РПД – сигнал разрешения прямого доступа;

ПЗ – сигнал подтверждения захвата магистрали;

БПД – сигнал блокировки прямого доступа

Рис. 11.3. Структура шины арбитража "n" системы bus master DMA цепочечного типа

Системная магистраль

Сигнал РПД распространяется последовательно через все устройства, пока его

распространение не будет заблокировано запросчиком ИЗПД

i

, выставившим запрос

прямого доступа (сигнал ЗПД

i

). Таким образом, приоритет ведущего устройства ма-

гистрали определяется его положением в цепи распространения сигнала РПД. Пусть

арбитр расположен в слоте с номером "0". Тогда приоритет устройств, расположен-

ных в последующих слотах, будет убывать с ростом номера слота. При отсутствии

устройства в слоте необходимо принять меры для того, чтобы цепь распространения

сигнала

РПД не разрывалась. Это обеспечивается либо специальной конструкцией

контактов слота, либо установкой перемычки на системной плате.

Сигнал линии ЛПЗ, как и в радиальной системе bus master DMA, информирует

арбитр о захвате магистрали тем или иным устройством. Этот сигнал всегда вы-

ставляет master и удерживает его на линии все время, пока осуществляет обмен

(управляет магистралью),

поэтому сигнал всегда представлен потенциалом.

Линия ЛБПД – общая для всех ШАр и предназначена для передачи от арбитра

сигнала блокировки прямого доступа (БПД), который запрещает bus mastering всем

интеллектуальным устройствам магистрали. Необходимость в этом может возник-

нуть, например, при появлении запроса на линии ЛЗПД ШАр более высокого приори-