Хмелевский И.В., Битюцкий В.П. Организация ЭВМ и систем. Однопроцессорные ЭВМ. Часть 3

Подождите немного. Документ загружается.

60

⎩

⎨

⎧

+−

=

+

,qvS

,S

S

ttt

t

1t

tt

tt

Sqесли

Sqесли

∉

∈

.

В первом случае обращение производится к странице, которая находится в па-

мяти верхнего уровня, и поэтому состояние этой памяти не меняется.

Во втором случае происходит обращение к странице, отсутствующей в памяти

верхнего уровня. Эта ситуация называется страничным сбоем, так как программа не

может дальше выполняться, пока нужная страница q

t

не будет переписана из памяти

нижнего уровня в память верхнего уровня, что сопряжено с потерями времени. По-

скольку в памяти верхнего уровня нет свободного места, из нее приходится удалять

некоторую страницу v

t

с тем, чтобы на ее место можно было поместить страницу q

t

.

Если во время пребывания страницы v

t

в памяти верхнего уровня в нее производи-

лась запись, эта страница при замещении должна переписываться в память нижнего

уровня. Такая процедура называется процессом замещения страниц, а правило, по

которому при возникновении страничного сбоя выбирается страница v

t

∈ S

t

для уда-

ления из памяти верхнего уровня, – алгоритмом замещения.

Для данной программы, порождающей некоторый поток обращений к памяти,

существует, по крайней мере, одна такая последовательность замещений страниц,

которая дает минимальное для этой программы число страничных сбоев – мини-

мально возможную последовательность замещений. При конструировании алгорит-

ма замещений стремятся приблизить реализуемую этим

алгоритмом последова-

тельность замещений к минимальной.

Оптимизация процесса замещений страниц упрощается, если известно, в каком

порядке в будущем будут происходить обращения к памяти или, по крайней мере,

вероятности обращений в будущем к отдельным страницам программы. Ясно, на-

пример, что в первую очередь из памяти верхнего уровня следует удалить страницу,

к которой

обращений больше не будет (вероятность обращений в будущем равна 0).

Трудность состоит в том, что, как правило, при выполнении программы отсутст-

вуют информация о потоке обращений или сколько-нибудь достоверные сведения о

вероятности обращений к отдельным страницам в будущие моменты времени.

Алгоритмы замещения можно разделить на две группы:

• физически нереализуемые,

использующие информацию (реально отсутст-

вующую) о потоке обращений в будущие моменты времени;

• физически реализуемые или эвристические, использующие только информа-

цию об обращениях к памяти в прошедшие моменты времени, т.е. только ис-

торию процесса.

Хотя алгоритмы первой группы на практике применить нельзя, они играют важ-

ную роль в теории алгоритмов

замещения, позволяя производить оценки (в том чис-

ле экспериментальные), в какой степени характеристики эвристических алгоритмов

приближаются к предельно возможным оптимальным.

Физически нереализуемые алгоритмы

Алгоритм Михновского-Шора. При каждом замещении страницы из памяти

верхнего уровня отсылается в память нижнего уровня страница, очередное обраще-

ние к которой произойдет позже, чем к любой другой странице в памяти верхнего

уровня.

Справедливо следующее предложение. Число замещений страниц в памяти

верхнего уровня (число страничных сбоев) при выполнении замещений по алгоритму

Михновского-Шора

является минимальным для заданных потока обращений и ис-

ходного распределения памяти, что имеет теоретическое доказательство.

Таким образом, алгоритм Михновского-Шора реализует минимально возможную

для данной программы последовательность замещений, поэтому этот алгоритм на-

зывают МИН-алгоритмом.

61

Если условиться, что известна вероятность обращений к отдельным страницам

программы, то оптимальным в смысле минимума среднего числа страничных сбоев

является

ОПТ-алгоритм: при каждом замещении страницы из памяти верхнего

уровня отсылается страница, вероятность обращения к которой не больше, чем к

любой другой странице в этой памяти.

Физически реализуемые (эвристические) алгоритмы замещения

Был предложен ряд алгоритмов этого класса.

Алгоритм случайного замещения (СЗ-алгоритм). При возникновении странич-

ного сбоя из памяти верхнего уровня с равной вероятностью отсылается любая из

находящихся там страниц.

НДИ-алгоритм. Из памяти верхнего уровня отсылается страница, наиболее

давно использовавшаяся.

Алгоритм "первый пришел – первый ушел" (ПППУ-алгоритм). Отсылается

страница, дольше других находившаяся в памяти верхнего уровня.

Алгоритм "последний пришел – первый ушел". Отсылается страница, позже

других поступившая в память верхнего уровня.

Следующие два алгоритма обладают определенными свойствами адаптации к

потоку обращений к памяти.

Алгоритм "карабкающаяся страница" (КС-алгоритм). Страницы в памяти

верхнего уровня образуют последовательность:

r1mm1m21t

j,...,j,j,j...,,j,jS

+−

= .

При очередном обращении q

t

к памяти эта последовательность изменяется по

правилу:

⎪

⎩

⎪

⎨

⎧

=

−

−+

,q,j,...,j,j

,j,...,j,j,...,j,j

,S

S

t1r21

r1mm21

t

1t

.Sqпри

1;m,jqпри

;jqпри

tt

mt

1t

∉

≠=

=

При обращении к странице j

m

, присутствующей в памяти верхнего уровня, по-

следняя меняется местами с соседней слева страницей, другими словами, "карабка-

ется" к началу последовательности, подальше от ее конца, куда происходит заме-

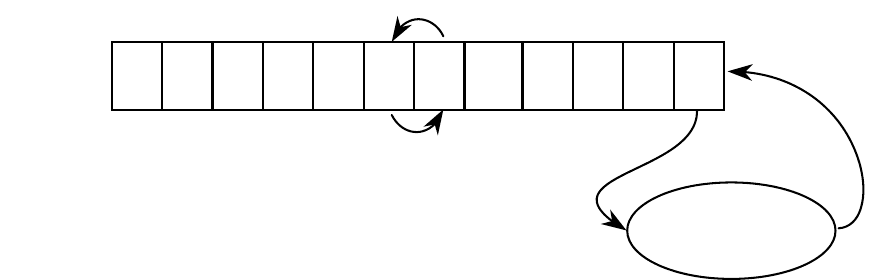

щение при страничном сбое. Этот процесс иллюстрирует схема на рис. 9.18.

j

1

j

2

…

j

m-1

j

m

j

m+1

j

r-1

j

r

…

…

…

…

Память

верхнего

уровня

Память нижнего

уровня

q

S

∉

t

t

Рис. 9.18. Алгоритм замещения "карабкающаяся страница"

Алгоритм "рабочий комплект" (РК-алгоритм). Страницы в памяти верхнего

уровня, использовавшиеся в течение заданного интервала времени, образуют "ра-

бочий комплект". Страницы из этой памяти, не вошедшие в "рабочий комплект",

формируют две очереди кандидатов на замещение:

- очередь страниц, в которые не вносились изменения, пока они присутствова-

ли в памяти верхнего уровня;

- очередь страниц, в которые

вносились изменения.

62

Замещение при страничном сбое производится по правилу:

первый пришел из

рабочего комплекта – первый ушел из памяти верхнего уровня. При этом сначала

подлежат замещению страницы из первой очереди. Описанный алгоритм использо-

вался еще в компьютерах IBM-360/370.

Предположим, что последовательность обращений q

1

, q

2

, …, q

t

соответствует

последовательности независимых случайных дискретных величин, таких что

{}

jt

pjqP ==

,

kj1

≤

≤

, 1p

k

1j

j

=

∑

=

.

Примем за состояние процесса замещения набор (а в некоторых случаях упо-

рядоченную последовательность) страниц, находящихся в памяти верхнего уровня.

Тогда для ряда алгоритмов замещения (СЗ, НДИ, ПППУ и некоторых других) процесс

изменения состояния верхнего уровня описывается однородной конечной эргодиче-

ской цепью Маркова, что указывает на существование стационарных вероятностей

пребывания процесса

в определенных состояниях и, как следствие этого, стацио-

нарных вероятностей страничных сбоев.

В качестве критерия эффективности W

r,k

алгоритма замещения А примем ста-

ционарную вероятность страничных сбоев:

(

)

{

}

tt

t

kr,

SqPlimAW ∉=

∞→

.

Можно для ряда алгоритмов замещения найти зависимость W

r,k

от p

1

, p

2

, …, p

k

и сравнить алгоритмы между собой, а также с физически нереализуемым ОПТ-алго-

ритмом. Определить W

r,k

для ряда алгоритмов можно, используя метод, основанный

на однородных эргодических цепях Маркова.

Описанные выше эвристические алгоритмы замещения страниц и их различные

комбинации лежат в основе алгоритмов замещения, используемых в современных

ЭВМ. При этом конкретные технические реализации алгоритмов замещения страниц

весьма сложные и сильно зависят от конкретной конфигурации аппаратных средств,

типа

операционной системы и даже ее модификации. Следует отметить только, что

в большинстве случаев алгоритмы замещения страниц в современных ЭВМ содер-

жат механизмы упреждающей выборки страниц. Идея использования упреждающей

загрузки страниц из ВП в ОП, как и в случае обновления блоков в кэш-памяти

(см. п. 9.3.3), основана на предположении о том,

что при очередном страничном

сбое обращение с большой вероятностью произойдет к следующей по порядку стра-

нице, уже находящейся в ОП. Кроме того, как уже отмечалось в п. 9.4.1, перемеще-

ние модифицированных страниц из ОП в ВП осуществляется в большинстве случаев

через кэшированную часть ОП (дисковый кэш), поскольку велика вероятность обра-

щения к

недавно удаленной странице. Такой механизм позволяет ускорить процесс

подкачки страниц при повторном обращении.

Более подробно вопросы организации виртуальной памяти в настоящем разде-

ле не рассматриваются, поскольку относятся к области системного программного

обеспечения компьютера (ядра операционной системы).

9.7. СОПРОЦЕССОРЫ

Расширение диапазона возможного применения процессоров с традиционной

фон-неймановской архитектурой привело к тому, что наборы команд МП стали весь-

ма громоздкими. Дальнейшее расширение наборов команд наталкивается на про-

блемы, связанные с поиском компромисса между добавлением команд, которые

способствовали бы повышению производительности для конкретных областей при-

менения, и усложнением кристалла ИС. Распространенный

метод введения относи-

тельно более специализированных команд, применение которого не приводит к по-

вышению сложности и стоимости базового МП, заключается в использовании сопро-

цессоров.

Сопроцессоры – это дополнительные процессорные устройства, обеспе-

63

чивающие выполнение дополнительных команд, в которых нуждается тот или иной

пользователь.

Наиболее распространенной разновидностью дополнительного процессорного

устройства (ДПУ) является сопроцессор для обработки чисел с плавающей запятой.

Это достаточно сложное устройство. Его сложность сопоставима со сложностью са-

мого процессорного устройства. Однако использование таких ДПУ позволяет при-

мерно в 100 раз увеличить скорость

выполнения команд обработки чисел с плаваю-

щей запятой и значительно повысить точность получаемых результатов. Особенно-

сти технической реализации ДПУ различны у различных изготовителей, но многие

основные принципы их построения не зависят от конкретной реализации.

Для использования команд, реализуемых сопроцессором в современных про-

цессорах (в частности, 32-разрядных), предусматривается командная маска. Она

представляет

собой группу резервных кодов операции, которая идентифицируется

процессором по заданному набору значений определенных битов кода. В остальных

битах кода операции определяется конкретная дополнительная операция.

Обычно ДПУ подключается к линиям адресов и данных процессора и в нужный

момент декодирует масочный код операции. Однако возможен и другой подход, при

котором для работы

с отдельным кодовым пространством ДПУ необходимы внеш-

ние логические схемы, так как ДПУ не способно само декодировать масочные коды

операции. Некоторые сопроцессоры имеют возможность брать на себя управление

процессорной шиной для прямого обращения к памяти. Другие же прибегают к услу-

гам основного процессора, который предоставляет им адреса для чтения или записи

данных в память. Последний вариант характерен для

однокристальных ДПУ (в ча-

стности, 32-разрядных). Возможность непосредственного обращения к памяти пре-

дусмотрена в некоторых

одноплатных сопроцессорах, предназначенных для обра-

ботки матриц и ВВ аналоговой информации.

В системе, где сопроцессор не установлен, его функции должен иметь возмож-

ность эмулировать центральный процессор. В его управляющем регистре может

быть предусмотрен бит, который устанавливается в состояние 1 при наличии сопро-

цессора. Если этот бит не установлен в состояние 1, то для

реализации масочной

операции, входящей в расширенный набор команд, центральный процессор перехо-

дит к определенной подпрограмме, при выполнении которой эмулируются соответ-

ствующие действия ДПУ.

Некоторые сопроцессоры работают в непараллельном (синхронном) режиме,

при котором центральный процессор вынужден дожидаться завершения ДПУ-

команды сопроцессором, для того чтобы начать выполнение очередной команды.

Другие сопроцессоры работают в

параллельном (асинхронном) режиме, позволяю-

щем центральному процессору выполнять другие команды одновременно с реали-

зацией ДПУ-команды сопроцессором. Очевидно, что параллельная работа сопро-

цессора и процессора позволяет повысить производительность системы в целом.

Однако при этом возникают проблемы, связанные с изменением содержимого памя-

ти центральным процессором до того, как соответствующие данные считаны

сопро-

цессором, а также изменением содержимого памяти сопроцессором без уведомле-

ния об этом центрального процессора. Одним из путей решения этих проблем явля-

ется запрещение прямого доступа к памяти со стороны сопроцессора при работе в

параллельном режиме.

Для микропроцессора I80386 ДПУ, выполняющего действия над ЧПЗ, является

сопроцессор I80387, имеющий быстродействие 1.8⋅10

6

операций в секунду и функ-

ционирующий параллельно с центральным процессором (I80386) в асинхронном

режиме.

64

ВОПРОСЫ ДЛЯ САМОПРОВЕРКИ

1. Какие преимущества дает теговая организация памяти?

2. Для чего используются дескрипторы?

3. Приведите формат дескрипторов сегмента программ или сегмента данных.

4. Как происходит обращение к памяти через дескрипторы?

5. ЭВМ RISC-архитектуры. Ее основные особенности.

6. Для чего предназначен механизм перекрывающихся регистровых окон?

7. Какие существуют направления оптимизации процессов обмена процессора

и ОП?

8. Основные

принципы конвейеризации процедур цикла выполнения команды.

9. Перечислите пути уменьшения влияния команд условных переходов на про-

изводительность конвейера команд.

10. В чем суть метода расслоения памяти?

11. Опишите метод "буферизации памяти".

12. Приведите алгоритм взаимодействия кэш-памяти и ОП при перемещении

блоков информации.

13. На чем основана концепция полностью ассоциативного кэш?

14. Опишите

принципы построения кэш с прямым отображением.

15. Опишите принципы построения двухвходового множественного ассоциатив-

ного кэш.

16. Процедура динамического распределения памяти. Как она осуществляется?

17. В чем заключается принцип построения виртуальной памяти?

18. Приведите схему страничной организации памяти.

19. Сегментно-страничная организация памяти.

20. Какие преимущества дает страничная организация памяти?

21. Перечислите варианты защиты памяти.

22. Какие бывают алгоритмы управления многоуровневой памятью?

23. Сопроцессоры. Их назначение и использование.

КОНТРОЛЬНЫЕ ЗАДАНИЯ

1. На листах ответа должны быть указаны номер группы, фамилия студента и

номер его варианта.

2. Номера вопросов выбираются студентом в соответствии с двумя послед-

ними цифрами в его зачетной книжке. В табл. 9.1 а

n-1

– это предпоследняя

цифра номера, а

n

– последняя цифра. В клетках таблицы стоят номера вопро-

сов, на которые необходимо дать письменный ответ.

Номера вопросов Таблица 9.1

a

n

a

n-1

0 1 2 3 4 5 6 7 8 9

1 2 3 4 5 6 7 8 9 10 11

0

1,5,9,

13,19

2,6,10,

14,20

3,7,11,

15,21

4,8,12,

16,22

1,7,12,

17,23

2,8,9,

15,19

3,5,10,

16,20

4,6,11,

13,21

1,8,11,

17,22

2,5,12,

18,23

1

3,8,10,

18,20

4,6,12,

13,22

2,7,9,

16,23

1,5,11,

14,21

3,6,9,

14,19

4,7,10,

13,20

1,6,12,

14,23

2,7,11,

15,20

3,5,11,

18,21

4,8,10,

15,22

2

1,6,9,

18,19

2,5,10,

17,20

1,8,11,

16,21

3,5,9,

18,22

2,7,9,

17,19

1,6,10,

14,22

3,7,12,

16,19

4,7,12,

15,23

2,5,10,

13,23

4,6,9,

17,21

3

1,5,9,

13,19

2,6,10,

14,20

3,7,11,

15,21

4,8,12,

16,22

1,7,12,

17,23

2,8,9,

15,19

3,5,10,

16,20

4,6,11,

13,21

1,8,11,

17,22

2,5,12,

18,23

65

Окончание табл. 9.1

1 2 3 4 5 6 7 8 9 10 11

4

3,8,10,

18,20

4,6,12,

13,22

2,7,9,

16,23

1,5,11,

14,21

3,6,9,

14,19

4,7,10,

13,20

1,6,12,

14,23

2,7,11,

15,20

3,5,11,

18,21

4,8,10,

15,22

5

1,6,9,

18,19

2,5,10,

17,20

1,8,11,

16,21

3,5,9,

18,22

2,7,9,

17,19

1,6,10,

14,22

3,7,12,

16,19

4,7,12,

15,23

2,5,10,

13,23

4,6,9,

17,21

6

1,5,9,

13,19

2,6,10,

14,20

3,7,11,

15,21

4,8,12,

16,22

1,7,12,

17,23

2,8,9,

15,19

3,5,10,

16,20

4,6,11,

13,21

1,8,11,

17,22

2,5,12,

18,23

7

3,8,10,

18,20

4,6,12,

13,22

2,7,9,

16,23

1,5,11,

14,21

3,6,9,

14,19

4,7,10,

13,20

1,6,12,

14,23

2,7,11,

15,20

3,5,11,

18,21

4,8,10,

15,22

8

1,6,9,

18,19

2,5,10,

17,20

1,8,11,

16,21

3,5,9,

18,22

2,7,9,

17,19

1,6,10,

14,22

3,7,12,

16,19

4,7,12,

15,23

2,5,10,

13,23

4,6,9,

17,21

9

1,5,9,

13,19

2,6,10,

14,20

3,7,11,

15,21

4,8,12,

16,22

1,7,12,

17,23

2,8,9,

15,19

3,5,10,

16,20

4,6,11,

13,21

1,8,11,

17,22

2,5,12,

18,23

10. ЭВОЛЮЦИЯ ШИННОЙ АРХИТЕКТУРЫ IBM PC

В начале настоящего курса (см. гл.1) было показано, что переход от мэйнфрей-

мов к малым ЭВМ (мини и микро) сопровождался существенным упрощением внут-

ренней структуры компьютера, а именно, переходом к магистрально-модульной

структуре, простейший вариант которой представлен на рис. 1.4. Магистрально-

модульная структура предполагает наличие в компьютере некоторой общей магист-

рали, к

которой в необходимой номенклатуре и количестве подключены все устрой-

ства ЭВМ, выполненные в виде функционально законченных блоков. Эта магистраль

получила название системной (см. п. 7.1). Первоначально это был единственный ка-

нал связи, по которому внутри ЭВМ передавалась информация между двумя и бо-

лее компонентами системы. В процессе эволюции мини- и микроЭВМ,

а также по-

вышения быстродействия процессоров одной системной магистрали оказалось не-

достаточно. Однако необходимость преемственности программно-аппаратных

средств серийно выпускаемых компьютеров разных поколений не позволила так

просто заменить разработанные ранее системные магистрали на более быстродей-

ствующие, хотя их производительность не соответствовала производительности но-

вых поколений процессоров. Компромиссным решением этой проблемы оказалось

введение помимо основной системной магистрали ряда других, более быстродейст-

вующих магистралей, которые получили название локальных шин. В процессе эво-

люции ЭВМ некоторые из них потеряли свое значение и исчезли (например, VLB),

другие продолжали развиваться, принимая на себя все больше функций основной

системной магистрали (например, PCI). Ввиду этого в современных компьютерах

помимо основной системной магистрали, имеется ряд быстродействующих локаль-

ных шин различного назначения.

Прежде чем перейти к рассмотрению основных

этапов эволюции шинной архи-

тектуры PC фирмы IBM, необходимо сделать ряд замечаний. Уже отмечалось, что в

литературе встречаются различные термины для обозначения системной или общей

магистрали. Это прежде всего термины: "общая шина", "системная шина", "шина ВВ"

и "шина расширения". Последний термин отражает тот факт, что системная магист-

раль позволяет подключать к компьютеру дополнительные

ПУ для расширения или

изменения его возможностей, т.е. позволяет изменять конфигурацию оборудования.

При этом часть устройств ВВ устанавливается непосредственно на системной (ма-

теринской) плате и не может быть заменена пользователем, а часть устройств ВВ

размещается в слотах, установленных на системной магистрали. При взаимодейст-

вии с МП те и другие

используют одну и ту же системную магистраль. Количество

66

слотов расширения может быть разным. В первом IBM PC их было пять, а в PC/XT –

восемь. В последующих моделях РС, имеющих быстродействующие локальные ши-

ны, их число изменялось в зависимости от конкретной конфигурации материнской

платы.

При дальнейшем изложении материала будет использоваться термин

шина

расширения (ШР), поскольку сама системная магистраль уже в первых РС претер-

пела существенные изменения по сравнению с классическим вариантом структуры

простейшей микроЭВМ, изображенным на рис. 1.4.

10.1. ЛОКАЛЬНАЯ СИСТЕМНАЯ ШИНА

Быстродействие ШР первых IBM PC (8 МГц) вполне соответствовало быстро-

действию процессора

I8088, на базе которого они были построены. Между тем для

оптимизации процесса обмена между ОП и МП разработчики пошли на усложнение

структуры РС и ввели две добавочные шины –

шину процессора и шину памяти. Та-

ким образом, обмен внутри ядра ЭВМ (т.е. между ОП и МП) осуществлялся не по

ШР, а по автономной магистрали, состоящей из двух шин, которую некоторые авто-

ры называют

локальной системной шиной. Этот термин будет использоваться при

дальнейшем изложении материала. Взаимодействие шины процессора и шины па-

мяти, а также их взаимодействие с ШР осуществлялось через набор специализиро-

ванных микросхем (чипсет), которые условно можно назвать

контроллером шины.

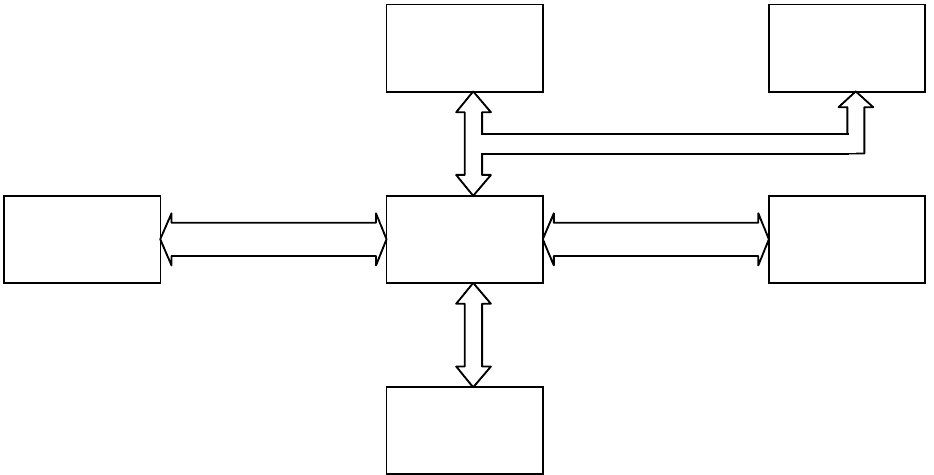

Очень упрощенная структура шин первых IBM PC приведена на рис. 10.1.

Шина

процессора

Шина

памяти

Микросхемы

контроллера

шины

Процессор

Основная

память

Внешний

кэш

Встроенные

устройства

ВВ

ВВ через

слоты

Шина расширения Шина расширения

Рис. 10.1. Упрощенная структура шин первых IBM PC

Шина процессора является самой быстродействующей и предназначается для

передачи данных, команд, адресов и сигналов управления между МП и контролле-

ром шины, который связывает ее с ОП и ШР. Шина процессора первых IBM PC рабо-

тала на той же тактовой частоте, что и процессор, поэтому слово данных или адрес

могли быть переданы по ней

в течение одного – двух периодов тактовой частоты

процессора (в современных РС тактовая частота шины процессора всегда ниже так-

товой частоты процессора). К этой же шине подключался внешний кэш, что позволя-

ло вести обмен процессор – кэш с максимальной скоростью. Число физических це-

пей в шине процессора существенно различно для различных поколений

процессо-

ров. Так, в компьютере с процессором

I80286 шина процессора имела 24 линии ад-

реса, 16 линий данных и 12 линий сигналов управления, а в компьютере с процессо-

67

ром Pentium было уже 32 линии адреса, 64 линии данных и почти в три раза больше

сигналов линий управления.

Скорость передачи данных по шине процессора (как и по любой другой шине)

определяется произведением разрядности шины на тактовую частоту шины, делен-

ному на число тактов, необходимое для передачи одного бита. Так, для первых мо-

делей процессора Pentium с тактовой частотой 66 МГц, совпадающей с тактовой

частотой шины процессора, максимальная скорость передачи данных составляет

66 МГц × 64 бита = 4224 Мбит/с → 4224 Мбит/с : 8 = 528 Мбайт/с.

При этом предполагается, что передача машинного слова происходит за один

период тактовой частоты шины. Эта скорость передачи данных называется

пропуск-

ной способностью шины и является максимальной. Она всегда выше средней рабо-

чей производительности шины примерно на 25%. Таким образом, для рассмотренно-

го примера средняя рабочая производительность шины будет составлять около

400 Мбайт/с.

Шина памяти предназначена для передачи информации между ОП и МП, а так-

же ОП и ПУ в режиме ПДП. Информация по шине

памяти передается с существенно

меньшей скоростью, чем по шине процессора. Это связано с тем, что шина памяти

содержит меньше линий данных. Их число определяется шириной выборки. Кроме

того, как уже отмечалось, быстродействие микросхем памяти всегда отстает от бы-

стродействия процессора, поэтому процесс передачи информации по шинам памяти

и процессора (т.е. по локальной системной шине) требует обязательной синхрони-

зации, которая осуществляется контроллером шины. Уже в первых моделях IBM PC

ОП выполнялась в виде отдельных модулей (SIMM), которые размещались в специ-

альных слотах, расположенных на шине памяти, аналогично слотам на ШР. Этот

принцип сохранен и в современных PC, хотя сами слоты и модули памяти (DIMM)

несколько видоизменились

.

10.2. ШИНА РАСШИРЕНИЯ

Как уже отмечалось, ШР позволяет МП и ОП взаимодействовать с различными

ПУ. За время, прошедшее после появления первых IBM PC, было разработано дос-

таточно много вариантов ШР, поскольку появление новых быстродействующих поко-

лений процессоров и ПУ (особенно видеосистем) требовало и более производи-

тельных ШР. Между тем одной из главных причин, сдерживающих интенсивное вне

-

дрение новых ШР, явилась их несовместимость со старыми стандартами, по кото-

рым множество фирм уже выпустили сотни тысяч единиц электронных компонентов

PC и которые становились совершенно ненужными в случае использования новых

ШР. В связи с этим эволюция ШР происходит достаточно медленно, без резких скач-

ков. Ниже рассматриваются основные моменты в процессе

эволюции архитектуры

ШР IBM PC.

10.2.1. ШИНА РАСШИРЕНИЯ ISA

Шина ISA (Industrial Standard Architecture) была использована в первых IBM PC,

построенных на процессоре I8088, в 1981 г. Она имела 8 линий данных, 20 линий

адреса, позволяла адресовать до 1 Мбайта памяти и тактовую частоту 8 МГц. Для

передачи данных требовалось от двух до восьми тактов. Эта же ШР была использо-

вана и в следующей модели – PC/XT, построенной на процессоре I8086.

Шина ISA считается достаточно простой

, но фирма IBM никогда не публиковала

ее полной спецификации, поэтому при создании плат адаптеров для первых IBM-

совместимых компьютеров разработчикам приходилось самим разбираться в ее ра-

боте.

Появление в 1984 году процессора второго поколения I80286, оперирующего

уже 16-разрядными данными, поставило проблему замены или модернизации ШР

68

ISA. Фирма IBM пошла по второму пути, и появился компьютер PC/AT со сдвоенны-

ми слотами расширения на модернизированной шине ISA. Вторая версия шины ISA

имела 16 линий данных, 24 линии адреса, позволяющих адресовать до 16 Мбайт

памяти, и тактовую частоту 8 МГц. Для передачи данных также (как и в первой вер-

сии) требовалось от двух до восьми тактов. Первая

и вторая версии шины ISA были

полностью совместимы, а сдвоенные слоты позволяли использовать старые

8-разрядные платы адаптеров, которые можно было вставлять в переднюю часть

слота. Новые же (16-разрядные) платы адаптеров вставлялись в обе части сдвоен-

ного слота. Пропускная способность новой версии шины ISA составляла

8 МГц × 16 бит : 2 такта = 64 Мбит/с → 64 Мбит/с : 8 = 8 Мбайт/с.

Соответственно, пропускная способность первой версии шины ISA вдвое

меньше, т.е. 4 Мбайт/с. Как уже отмечалось, это теоретическая, максимальная ско-

рость передачи данных. Однако достаточно сложный протокол обмена существенно

снижает реальную пропускную способность шины. Считается, что реальная пропуск-

ная способность ШР составляет примерно половину от максимальной.

Впоследствии с

появлением 32-разрядных процессоров некоторые фирмы на-

чали разрабатывать свои собственные версии расширения шины ISA, но сколько-

нибудь заметного распространения они не получили. Дополнительные линии этих

шин обычно использовались только при работе с платами расширения памяти и ви-

деоадаптерами. Их параметры и разводки разъемов существенно отличаются от

стандартных.

10.2.2. ШИНА РАСШИРЕНИЯ МСА

Появление 32-разрядного процессора I80386 привело к тому, что 16-разрядная

ISA перестала соответствовать возможностям нового поколения МП. Фирма IBM не

стала вновь модернизировать шину ISA, а разработала новую – МСА (Micro Channel

Architecture). Шина МСА полностью несовместима с шиной ISA и не позволяет ис-

пользовать старые платы адаптеров, однако по всем параметрам превосходит

16-разрядную шину ISA. Это достаточно дорогая шина, разработанная в пику

конку-

рентам для своих компьютеров PS/2, начиная с модели 50. Состав управляющих

сигналов, протокол и архитектура ориентированы на асинхронное функционирова-

ние шины и процессора, что снимает проблемы согласования скоростей процессора

и ПУ. В процессе работы шина МСА может передавать управление отдельным под-

ключенным к ней адаптерам (

bus mastering), для реализации режима ПДП или обме-

на между двумя адаптерами. Все запросы на захват шины поступают в специализи-

рованное устройство, называемое

арбитром шины (CACP – Central Arbitration Con-

trol Point). Арбитр обеспечивает доступ к шине всем устройствам в соответствии с

системой приоритетов, предотвращая конфликты и монополизацию шины одним из

них. Более подробно понятия “bus mastering”, “арбитр шины”, а также режим ПДП

(DMA) обсуждаются в гл. 11. Архитектура шины позволяет эффективно и автомати-

чески конфигурировать все устройства программным путем (в МСА PS/2 нет пере-

ключателей

ни на системной плате, ни на адаптерах). В шине МСА предусмотрено 6

типов слотов:

- 16-разрядные;

- 32-разрядные;

- 16- и 32-разрядные с дополнением для плат памяти;

- 16- и 32-разрядные с дополнениями для видеоадаптеров.

Фирма IBM хотела не просто заменить старый стандарт ISA на новый, но и сде-

лать на этом деньги. IBM потребовала от всех производителей, желающих получить

лицензию на использование новой шины МСА, заплатить за использование шины

ISA во всех ранее выпущенных компьютерах. Это непомерное требование привело к

69

разработке конкурентами фирмы IBM альтернативной шины EISA (см. п. 10.2.3), что

существенно замедлило распространение шины МСА.

Эта причина, а также полная несовместимость с массовыми ISA-устройствами

привели к тому, что новая шина МСА при всей прогрессивности архитектуры (отно-

сительно ISA) не пользуется популярностью из-за узости круга пользователей МСА-

устройств. Между тем МСА еще находит

применения в мощных файл-серверах, где

требуется обеспечить высоконадежный производительный ВВ.

10.2.3. ШИНА РАСШИРЕНИЯ EISA

Стандарт EISA (Extended Industry Standard Architecture) появился в 1988 году в

ответ на разработку фирмой IBM шины МСА и требование ее лицензировать (см.

п. 10.2.2). Конкуренты сочли излишним платить задним числом за давно используе-

мую шину ISA и, проигнорировав новую разработку IBM, создали свою. В этой рабо-

те приняли участие практически все ведущие изготовители компьютеров (за исклю-

чением, естественно, IBM) и крупнейшие

фирмы по производству программных про-

дуктов. Первые компьютеры с шиной EISA появились в 1989 г. Это единственное

жестко стандартизированное расширение ISA до 32 бит и количеством слотов рас-

ширения до восьми.

Шина EISA разрабатывалась как преемница ISA, а не как альтернатива ей, по-

этому различия между ними связаны лишь с появлением дополнительных возмож-

ностей. В шине EISA

предусмотрены 32-разрядные слоты для компьютеров с про-

цессорами 386DX и последующими моделями. Слот шины EISA построен так, что

позволяет разрабатывать устройства, обладающие многими возможностями адапте-

ров МСА, но при этом может работать и с платами, созданными в старом стан-

дарте ISA.

Несмотря на существенное увеличение числа линий в шине EISA (55 новых

сигналов), 32-разрядный слот EISA выглядит

почти так же, как и 16-разрядный слот

ISA. Между тем слот шины EISA сдвоенный. Два ряда контактов соответствуют

16-разрядному слоту ISA, остальные расположены в глубине разъема и относятся к

расширению EISA, поэтому контакты кромкового разъема старых плат ISA, не имею-

щих специального ключа, попадают только на верхние контакты слота.

По шине EISA можно передавать до 32

бит данных одновременно при тактовой

частоте шины 8,33 МГц. В большинстве случаев передача данных осуществляется,

как минимум, за два такта, хотя возможна и большая скорость передачи. Макси-

мальную производительность шины реализует пакетный режим (

burst mode) – скоро-

стной режим пересылки пакетов данных без указания текущего адреса внутри паке-

та. В пакете очередные данные могут передаваться в каждом такте шины, т.е. мак-

симальная пропускная способность шины EISA составляет

8,33 МГц × 32 бита = 266,56 Мбит/с → 266,56 Мбит/с : 8 = 33,32 Мбайт/с.

Длина пакета может достигать 1024 байта. Передача данных по "неполной

ши-

не" (при работе с 8- или 16-разрядными платами адаптеров в стандарте ISA) осуще-

ствляется соответственно с меньшими скоростями.

В шине EISA (как и в МСА) предусмотрена возможность передачи управления

шиной одной из плат адаптеров (

bus mastering) для реализации режима ПДП или

обмена между двумя адаптерами. Работу адаптеров координирует устройство, на-

зываемое арбитром шины (CACP), которое иногда еще называют периферийным

контроллером (ISP – Integrated System Peripheral). Арбитр временно предоставляет

всю систему в полное распоряжение той или иной плате адаптера в соответствии с

четырехуровневой системой приоритетов, расположенных в следующем порядке (по

убыванию):