Дипломная работа - Проектирование 10 кВт преобразователя

Подождите немного. Документ загружается.

20

and its extension to fit the actual case.

(

)

2

_

2

_

)(

2

1

rippleMAXDCMAXDCtotrippleout

VVVCtP −−×=×

(2.4.2.1.2)

Where P

out

is the rated power of the inverter, V

DC_MAX

is the maximum voltage of the

rectified output, V

ripple

is the maximum ripple allowed and t

ripple

is the period time of the

ripple. The ripple frequency for a full wave bridge is the main grid frequency multiplied

by six. Solving for C

tot

in (2.4.2.1.3) with insertion of the proper values gives:

()

422

1067,4)16566(566

2

1

2400

1

10000

−

×=→−−×=×

tottot

CC = 467 μF (2.4.2.1.3)

As very few capacitors exist capable of handling this high voltage and still maintain a

large capacitance multiple capacitors has to be connected in series. Although when serial

connected a resistor has to be in parallel with each capacitor as explained more in detail

later in this chapter. A common way is to use two legs in parallel with two identical serial

connected capacitors maintaining the same capacitance as a single one while doubling the

maximum voltage. This precaution due to the voltage peaks during start-up when the

voltage over the capacitor can rise to a level between 1.4 and 1.8 times normal depending

on the size of the choke inductor and the protective circuits. The surge current appear

because during start-up the capacitor bank is virtually short circuited and the choke

inductor will try to maintain this current, thus inflicting a high voltage transient. The

surge current and voltage over-shoot can be reduced or almost eliminated with these

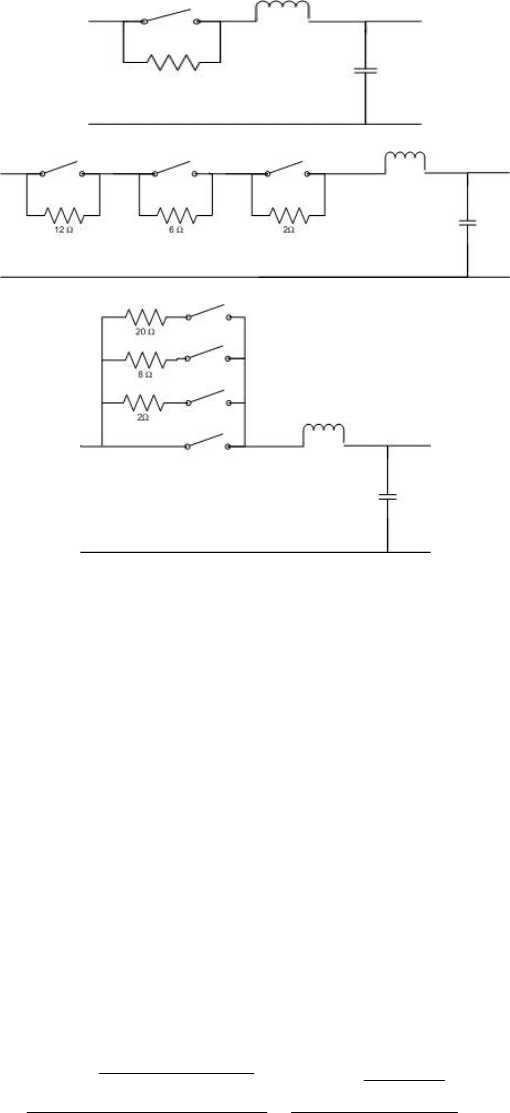

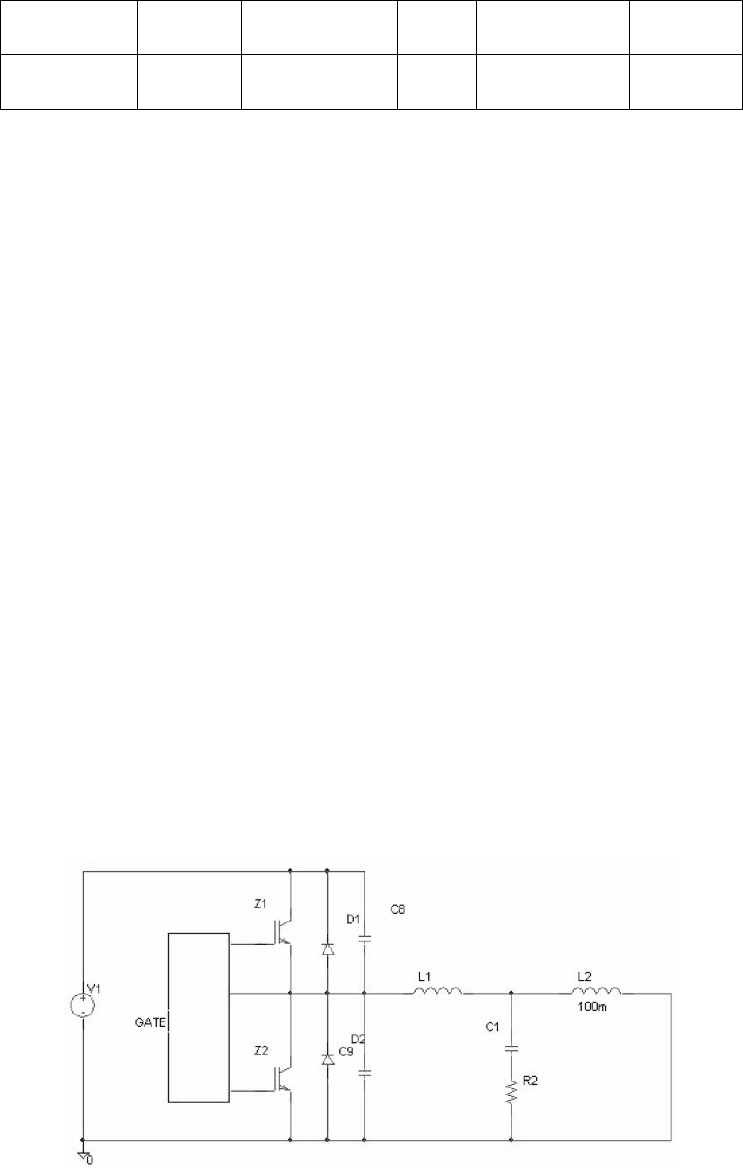

protective circuits as illustrated in figure 16. The switch in this case is a high power

transistor, most likely an IGBT with a low saturation voltage. As the resistor will initially

limit the charge time of the capacitor it will also decrease the over-shoot. The surge

limiter can be expanded into several levels reducing the resistance sequentially although

many copies of this circuit in series will accumulate a large on-resistance in steady state

and therefore add a non negligible loss. However, if connected in parallel they can

replace each other instead and will end up with only one transistor in series causing a

smaller on-resistance and a lower power loss. When this rather fast switching behavior

has occurred it can be relieved by a relay, these are usually much slower but have a much

smaller on-resistance than any semiconductor almost eliminating the added loss. A bonus

of this circuit is that it limits the converter inrush current significantly from a level that

would probably destroy the rectifier to a reasonable current. Simulations of this behavior

with and without the surge limiter can be seen in appendix A which is based on a system

simulation done in Matlab and Simulink, the circuitry can be found in appendix B.

21

Figure 16 : Protective circuits: simple, series and parallel connection

Not only does the capacitor require a wide margin for voltage but also for the capacitance

where tolerance (±20%) and wear-out (-10% can reduce the capacitance with up to 28%

(1-0,8*0,9).

Taking these precautions suggests the Evox Rifa PEH200 electrolyte capacitor with the

ratings 400V and 680 µF with an individual weight of 180g. The four combined

capacitors get a rating of 800V maximum and still has the same capacitance as a single

one but of course weights four times as much i.e. 720g.

A doubling in the rated power of the inverter would result in at least doubling the

capacitance required suggesting the 1500 µF version which would weight 430g each

increasing the weight of the capacitor bank by at least 140%.

However, the next step would be to calculate the ripple currents from the AC-line and

from to the load by first calculating the capacitor charging time with 2.4.2.1.4 [15]:

4002

566

16566

arccos

2

arccos

_

_

××

⎟

⎠

⎞

⎜

⎝

⎛

−

=

××

⎟

⎟

⎠

⎞

⎜

⎜

⎝

⎛

−

=

ππ

grid

MAXDC

rippleMAXDC

C

f

V

VV

T

=94.8 μs (2.4.2.1.4)

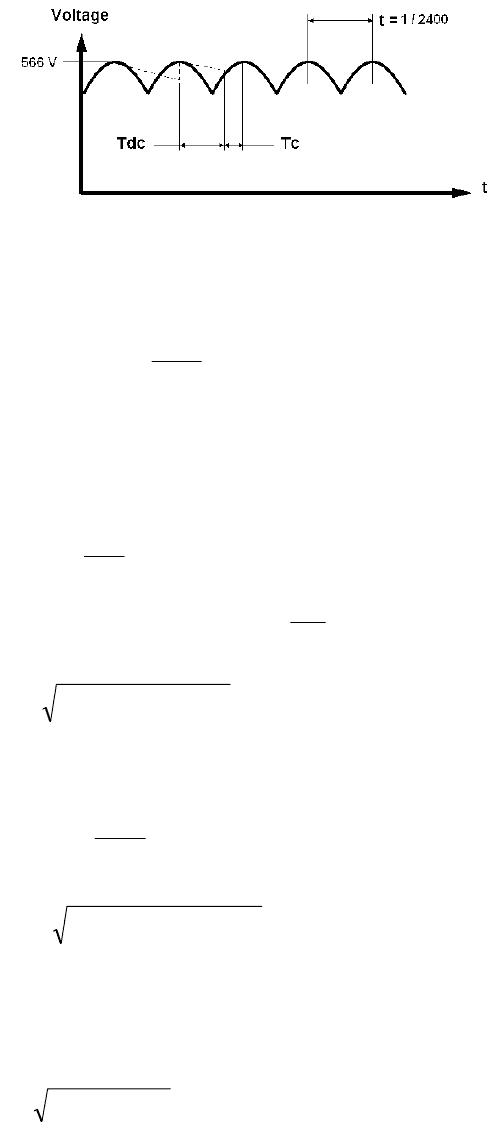

The capacitor charge time can be illustrated and defined as in figure 17:

22

Figure 17 : Charge and Discharge time of capacitor bank

With the charge time and the period time of the ripple voltage it is easy to derive the

capacitor discharge time as in equation 2.4.2.1.5.

0000948,0

2400

1

−=−=

CrippleDC

TTT

=321.8 μs (2.4.2.1.5)

Based on the change in voltage vs. time (dV/dt), the peak and RMS charge current (the

rectifier output current) through each capacitor leg can now be calculated as in equation

2.4.2.1.6 and 2.4.2.1.7.

A 39.4=×=

C

Cpeak

dT

dV

CI (2.4.2.1.6)

Where C is the capacitance in each leg, which is

2

tot

C

due to the serial connection.

A 18.8

2

=××=

rippleCCpeakCrms

fTII

(2.4.2.1.7)

In the same manner the peak and RMS discharge currents can be calculated using the

discharge time instead as in equation 2.4.2.1.8 and 2.4.2.1.9:

A 11.6=×=

DC

DCpeak

dT

dV

CI

(2.4.2.1.8)

A 10.2

2

=××=

rippleDCDCpeakDCrms

fTII (2.4.2.1.9)

With calculations done in equation 14 and 15 the ripple current resulting from the

rectification of the grid can now be calculated for each branch of the capacitor bank as in

equation 2.4.2.1.10.

A 21.4

22

=+=

DCrmsCrmsrms

III

(2.4.2.1.10)

Thus, through the whole capacitor bank it flows twice as much since it has two legs

adding up to 42.8 A.

23

The load ripple current for the whole capacitor bank is calculated as in equation

2.4.2.1.11.

()

A 17.92

2

550566

10000

2

__

_

=

⎟

⎠

⎞

⎜

⎝

⎛

+

=

⎟

⎟

⎠

⎞

⎜

⎜

⎝

⎛

−+

=

rippleMAXDCMAXDX

rated

rmsload

VVV

P

I

(2.4.2.1.11)

Which gives a load current of 8.96 A per leg. The total makeup of the current through the

capacitor bank is 17.92 A @ 10 kHz and 42.8 A @ 2400 Hz.

The next thing is to determine the power loss achieved in the capacitor bank and whether

it is to large enough to require extensive cooling or a large choke inductor to maintain

sufficient lifetime. The power loss can be calculated by somewhat altering the well

known formula P = U x I as done in equation 2.4.2.1.12.

ERSIIRIUP

rmsloss

×=×=×=

2

2

(2.4.2.1.12)

Where the ERS is the equivalent series resistance which can be found in diagrams within

the datasheet describing the capacitor. This ESR is strongly dependant on the frequency

and the hotspot

6

temperature (T

ht

) which is typically 20º C warmer than ambient

temperature(T

a

) of 70º C [15].

These expected typical values are found to be: ESR(2400Hz) = 13.5 mΩ

ESR(10kHz) = 12.5 mΩ

Using the estimated ESR values and the calculated current at each frequency two

components of power loss can be estimated for each capacitor, trivially four times this

loss would give the total loss of the capacitor bank excluding the choke inductor.

W6.180135.04.21)2400(

2

=×=HzP

loss

W10125.096.8)10000(

2

=×=HzP

loss

(2.4.2.1.13)

This gives each capacitor a loss of about 7 W which is dissipated through heat. Whether

the capacitor can withstand this produced heat is dependant on the thermal resistance

between hotspot and the ambient air as well as the temperature of this ambient air.

A too high temperature at the hotspot will result in a reduced lifetime and this

temperature can be calculated with equation 2.4.2.1.14.

CTRPT

R

TT

P

aahtlossht

aht

aht

loss

°=+×=+×=↔

−

= 4.94704.318.7

_

_

(2.4.2.1.14)

The thermal resistance 3.4ºC/W between the hotspot and the ambience (R

ht_a

) can be

found in the datasheets under a variety of conditions, this one is without any heatsink or

6

The center of the capacitor where the highest temperature is likely to arise.

24

airflow. As it can be seen the temperature at the hotspot is very close to where the ESR

was specified negating the need for further more detailed calculations concerning the

loss. However, if this increase in temperature would affect the lifetime too much the

choke inductor can be designed to extensively filter the high frequency components.

Usually it is just meant for suppressing the high frequent ripple.

Suppose the temperature would be too high and the power loss needed to be reduced.

To keep the hotspot temperature at 90 º C 1.3 W is needed to be transferred to the choke

inductor as explained in chapter 2.4.2.2.

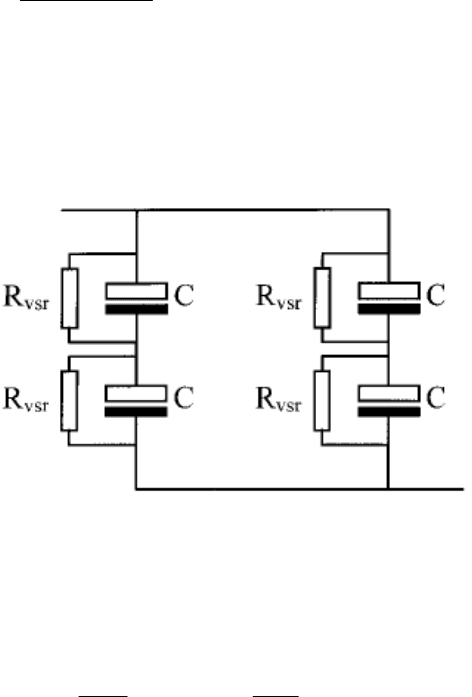

However, for the intended voltage sharing of the two serial capacitors to work correctly a

resistor has to be connected in parallel with each capacitor. The resistance of this resistor

is dependent on the capacitor value according to equation 2.4.2.1.15 [15]:

[]

FC

R

vsr

μ

×

=

015.0

1000

=143 kΩ (2.4.2.1.15)

As a precaution the power rating of the resistor should be at least 50% higher than

estimated and the tolerance should be kept below 5% to prevent failure. The electrical

layout is illustrated as in figure 18, the physical layout on the other hand should not be

taken to easily as the inductance has to be kept low.

Figure 18 : Electrical layout of capacitor bank

According to the equation for lifetime the capacitor will live for at least 30 kH which is

far beyond the limit of 5 kH. The uncertainty is due to few values of expected rate of

failure where an average had to be taken. Although in the worst case the lifetime is still

enough by far.

()

(

)

12

9485

4

85

21062

−

−

××=×=

C

T

ht

ALOP ≈36000 h (2.4.2.1.16)

Where A is the lifetime at reference temperature and C is the rise in degrees required for

cutting the lifetime in half, both of these available from the data sheet.

25

However, this lifetime can still prove uncertain in avionic applications as the thermal

resistance due to convection will increase with altitude resulting in a higher hotspot

temperature. The air pressure will also affect the lifetime of the capacitor as the

electrolyte degrade faster.

2.4.2.2. Choke inductor

The choke inductor is mainly for reducing the transients capable of causing fatal failure

in the capacitor bank. However it can be designed to filter some of the high frequency

components of the charge current resulting in transferring the loss from the capacitor to

the inductor

Suppose the 94.4 ºC is too high and need to be reduced to 90 ºC, based on previous

calculations a reduction of 1.29 W is needed in each capacitor. This combined loss

reduction achieved in the four capacitors will be withdrawn from the inbound charge

current. A rough estimation for the needed reduction in voltage can be done by using the

maximum ripple voltage over the capacitors and the reduction in power as explained by

equation 2.4.2.2.1.

pkpk

initial

reduction

ripplechoke

V

P

P

VV

−

=×== 34.3

18.6

29.1

16 (2.4.2.2.1)

rms

pkpk

rmschoke

V

V

V 58.1

11.2

_

==

−

(2.4.2.2.2)

The 2.11 factor in (is different than the normal

22 ×

since the voltage is not pure

sinusoidal to its form. The remaining fundamental ripple current can be estimated using

the new power loss and the ESR of the capacitors as in equation 2.4.2.2.3.

()

2

0135.02

29.118.62

_

×

×

−×

=×=

branches

branch

branchloss

ripple

n

ESR

P

I

=38.1 A (2.4.2.2.3)

This ripple current is a small reduction from the former value of 39.4 A and now the

proper inductance can be calculated as in equation 2.4.2.2.4:

1.3824002

58.1

2

2

×××

=

×××

=→=×××=

ππ

π

If

U

L

I

U

LfX

ripple

rippleL

=2.75 μH (2.4.2.2.4)

The power capabilities of the choke inductor are usually done with some empirically

established rules actually meant for transformers. However the figures given above are

enough to choose an inductor from an arbitrary manufacturer. Consider the DC3-56G

from WILCO, it weights approximately 30g each and measures 28 x 21.3 mm, to cover

the current two are used in parallel, hence the inductance of 5.6 µH.

Component Ratings Manufacturer

and Model

Mass

(g)

Volume

(mm

3

)

Power

loss (W)

26

L 5.6μH WILCO

DC3-56G

2*30 3*(28x22) 4*1.3

C 680μF EVOX RIFA

PEH200

4*180 3*(50x75) 4* 5.9

Table 4 : DC-bus filter components

2.4.2.3. Output filters

If there are long wires between the output of the inverter and the inductive load the stray

impedance (usually mostly capacitive) can induce annoying behavior both in the motor

and the driving transistors. The long wires would also serve as a good antennae emitting

EMI caused by the transistor transients when switching fast. Although, the problem with

emitted EMI can be treated with proper shielding of the conducting wire. In the following

chapter advantages/disadvantages and guidelines for an approximate design of an output

filter is carried out under the assumption that the cable is no longer than 30 meters. Near

and above this limit several phenomenons occur such as standing waves due to

impedance mismatch between the motor and the cable. Such standing waves can cause

serious over voltages and current oscillations too strong to be managed by a LC-filter.

Many motor manufacturers have recently published maximum dV/dt ratings for their

product, usually around 5 V/ns while the commutation of state of the art transistor can be

far above this rating, up to 10 V/ns or even more. Here a mean to reduce dV/dt at the

motor terminals are required and such a mean is often a simple LC-filter. It has also been

proven that placing the filter near the motor terminals can further improve this

misbehavior compared to placing it on the inverters board. However, as the task at hand

is to evaluate a complete inverter solution the choice is to have the filter within the

inverter unit, this filter will also be designed without any snubber circuits implemented.

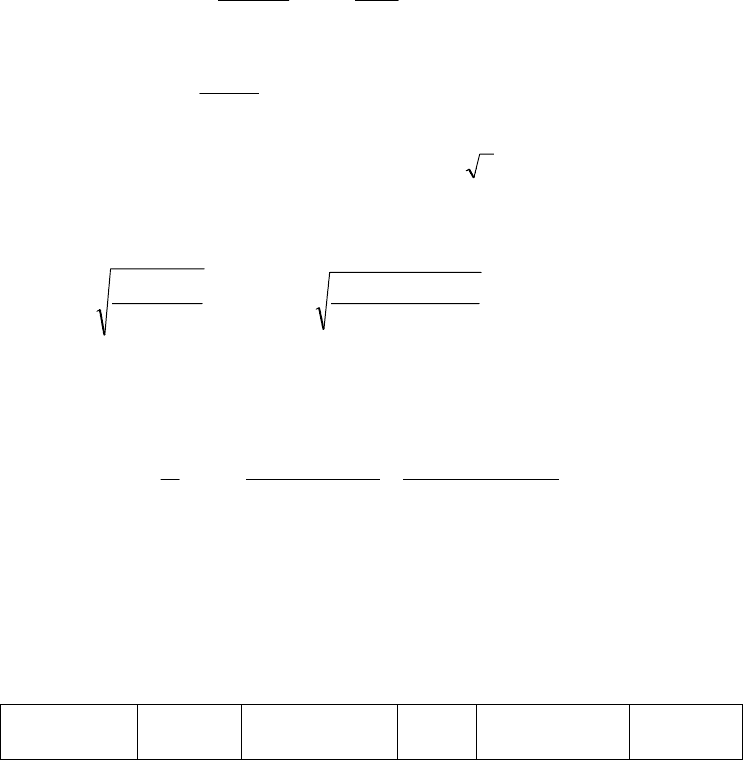

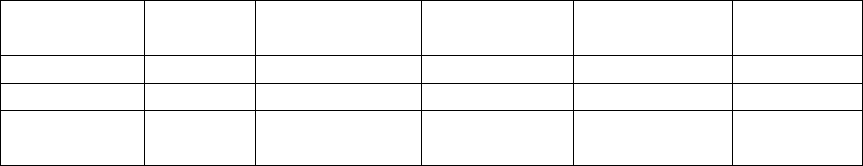

In figure 20 is an illustration presented where a LC-filter has been added between the

output of the transistor-bridge and the motor, although only one phase is represented. The

motor has been modeled as a large inductor L

2

corresponding to the phase/neutral

winding.

Figure 19 : Output filter

27

Where V

1

represents the DC-bus voltage and the two capacitors represents the Collector-

Emitter-capacitor (C

ce

) which also plays an important role during commutation.

Obviously the design of the filter is very simple and by assuming I

peak

is the peak motor

current, C

1

can be chosen as in equation 2.4.2.3.1.

max

1

/ dtdV

I

C

peak

= (2.4.2.3.1)

C

1

softens the switching from the IGBTs so that the maximum dV/dt at the motor

terminals is kept within limits supplied by the manufacturer or the EMI specifications are

met. However, C

1

cannot be left alone as there would run very large current peaks

through the IGBT leg during turn most likely to trigger the over-current protection

handled by the controlling circuit. This is where the inductor L

1

comes in to block this

high charge current and the dimensioning of the inductor will be such that current peaks

in the IGBT (or C

1

) does not trigger the over-current protection, at least. The over-current

protection is dimensioned in advance with respect to the switching devices and their

current handling capabilities. As so far this is a simple LC circuit and it is driven by very

high dV/dt it will soon start go generate oscillations higher than the DC-bus voltage

which is far from what the filter components and the motor are designed for. A damping

resistor in series with the capacitor would suppress this behavior and in addition

removing un-useful power dissipation otherwise dissipated in the capacitor. When this L

1

is involved the expression in equation 23 is obsolete due to the resonance between L

1

and

C

1

. Thus the actual dV/dt will also be determined by L

1

giving a new expression as

follows by equation 2.4.2.3.2 for the initial dV/dt:

11

CL

V

dt

dV

DC

×

=

(2.4.2.3.2)

The value of L

1

will be designed taking into account that each IGBT sees the phase

current of the motor, the recovery current of the opposite recovery diode and the peak

current of the filter. Although a fourth component could exist if the commutation causes

cross talk but it is not very common due to very potent controlling circuits and drivers.

After considering over-current limits and the peak recovery current the allowed peak

current contribution of the output filter can be determined. Excluding the damping

resistor R

2

the current through the filter can be calculated as in equation 2.4.2.3.3 where

the Z

C

is the characteristic impedance of the filter as determined in equation 2.4.2.3.4.

C

DC

filter

Z

V

I =

max_

(2.4.2.3.3)

1

1

C

L

Z

C

=

(2.4.2.3.4)

28

But as explained earlier the damping cannot be zero and thus the effect of R

2

has to be

considered. Critically damping is achieved when R

2

is equal to Z

C

but a lower value

could be chosen due to C

8

and C

9

. Suppose R

2

is chosen to Z

C

, then the current peak in

the IGBTs due to the output filter would be as determined in equation 2.4.2.3.5:

C

DC

filter

Z

V

I

×

=

2

max_

(2.4.2.3.5)

As current limiting is not the only constraint for L1 it also has to be designed to ensure

enough build-up voltage in the motor’s coils during a very low duty cycle [19]. The

minimum duty cycle time should at least be twice as long as the resonance cycle caused

by the LC circuit. Neglecting the damping caused by R

2

and adding some margins instead

gives the proper value of L

1

as in equation 2.4.2.3.6 assuming the minimum turn-on time

is known.

min_11 on

TCL ≤××

π

(2.4.2.3.6)

Combining the 2.4.2.3.2 and 2.4.2.3.6 an expression for the maximum dV/dt related to

V

DC

and the minimum turn-on time is achieved by equation 2.4.2.3.7.

min_on

DC

T

V

dt

dV

π

×

=

(2.4.2.3.7)

The result achieved in 2.4.2.3.7 seems highly logical as it would require a shorter turn-on

time to get a higher dV/dt. This overall gain in less EMI and enough slow dV/dt for the

motor does not come without loss, both in more weight and in more direct power loss.

The loss is dissipated in the damping resistor and cannot be neglected, in the case of R

2

being equal to Z

C

the power loss can be estimated as in equation 2.4.2.3.8 [19]:

swon

DC

lossfilteroutput

fT

R

V

P ××

×

=

min_

2

2

__

4

(2.4.2.3.8)

Applying the above given theory to the specific case examined in this paper gives some

guidelines for values and physical size of the filter components. As they should be

applied to each phase conductor pf course three of each has to be included.

Assuming as before the maximum dV/dt for the motor is the common 5V/ns and in the

data sheet for the IRG4PSH71UD it can be found that the typical dV/dt is 30 V/ns which

is much too fast. As the peak voltage through the IGBT is 20.5A (

5.142 × ) the value of

C

1

can be calculated using 2.4.2.3.1, which gives the value 4.1nF. According to 2.4.2.3.7

the T

on_min

is 350 ns which along with equation 2.4.2.3.6 gives the value for L

1

, 3μH. As

the characteristic impedance Z

C

is calculated as in equation 2.4.2.3.4 it receives the value

27Ω which is also the minimum value of R

2

, actually R

2

can be chosen a bit larger to

suppress some overshoot but it should remain between Z

C

and

C

Z

×

2

. Suppose the

29

maximum current due to opposite diode reverse recovery is 20.5 A and the maximum

current through the filter being according to 2.4.2.3.4 (if R

2

= Z

C

) 10 A. This along with

the well known maximum current through and IGBT gives a maximum current of 51 A,

this is what the over-current protection level should be set to. The power loss mainly

dissipated in the resistor is calculated using equation 33 and is estimated to be 10 W. Yet

again, this is for only one phase and the loss and weight of components has to be tripled

to make up the actual figures. When of-the-shelf products are considered the weight

estimated to be 60g for L

1

, 6g for C

1

and 7g for R

2

adding up to73g per phase.

Filter

component

Value Manufacturer

and model

Mass(g) Dimensions Power loss

R 27 Ω ARCOL HS 3*7 3*(30x10x10) 3*10

L 3 μH Pulse L100 3*60 3*(50x40x36) -

C 4.1 nF EVOX RIFA

PHE845

3*5.2 3*(6x14.5x26) -

Table 5 : Output filter components