Сушкин И.Н. Вычислительная техника и информационные технологии. Курс лекций

Подождите немного. Документ загружается.

101

Работа команды LOOP заключается в выполнении следующих действий:

- декремента регистра СХ (ЕСХ);

- сравнение регистра СХ (ЕСХ) с нулём.

Если СХ (ЕСХ) > 0, то управление передаётся на метку перехода; если

СХ (ЕСХ) = 0, то управление передаётся на следующую после LOOP команду.

Алгоритм работы команды LOOPЕ/LOOPZ таков:

- декремент регистра СХ (ЕСХ);

- сравнение регистра СХ (ЕСХ) с нулём;

- анализ состояния флага нуля ZF.

Если СХ (ЕСХ) > 0 и ZF = 1, то управление передаётся на метку

перехода; если СХ (ЕСХ) = 0 или ZF = 0, то управление передаётся на

следующую после LOOP команду.

Работа команды LOOPNE/LOOPNZ заключается в выполнении

следующих действий:

- декремента регистра СХ (ЕСХ);

- сравнение регистра СХ (ЕСХ) с нулём.

- анализа состояния флага нуля ZF.

Если СХ (ЕСХ) > 0 и ZF = 0, то управление передаётся на метку

перехода; если СХ (ЕСХ) = 0 или ZF = 1, то управление передаётся на

следующую после LOOP команду.

Команды прерывания. Программные прерывания бывают трёх типов:

- INT type – прерывание по номеру вектора (type);

- INTO – прерывание при переполнении;

- IRET – возврат из подпрограммы прерывания.

Во втором байте команды INT type помещается 8-разрядный номер

вектора прерываний, полученный процессором номер вектора умножается на

4, чтобы найти точку входа в таблицу векторов. В таблице векторов,

максимальный размер которой один килобайт, на каждый вектор отводится

по 4 байта: в первых двух байтах помещается значение IP, во вторых двух

байтах – значение CS. Новые значения регистров CS и IP помещаются в

соответствующие регистры микропроцессора, таким образом, адрес

соответствующей подпрограммы определён. Для того, чтобы адрес возврата

в основную программу не был утрачен, предварительно производятся

следующие действия: текущие значения регистра CS и указателя команд

записываются в стек, также в стек записываются значения регистра флагов F

и сбрасываются флаги IF и TF. Обычно пользовательский резерв начинается

с вектора № 32.

Однобайтная команда INT, отличающаяся от двухбайтной одним

битом, не требует специального указания уровня прерывания. Она

автоматически воспринимается процессором как прерывание третьего уровня

(type 3), и используется в программах для организации контрольной точки.

102

Однобайтная команда INTO вызывает переход на обслуживание

прерывания четвёртого уровня, связанного с переполнением, когда значение

флага переполнения OF=1. Команда INTO обычно используется после

арифметических команд над числами со знаком.

2.4.3.7. Команды управления процессором

Существует три типа команд управления процессором: команды

работы с флагами, установки МП в особые состояния и синхронизации с

сопроцессором.

Команды операций с флагами. Эти команды включают семь мнемокодов:

- STC – установка флага переноса CF;

- CMC – инвертирование флага переноса;

- CLC – сброс флага переноса;

- STD – установка флага направления передачи DF;

- CLD – сброс флага направления DF;

- STI – установка флага разрешения передачи;

- CLI – сброс флага разрешения прерывания.

Назначение этих команд очевидно и комментарий не требует.

Команды установки микропроцессора в особые состояния. Это

команды HLT (останов) и WAIT (ожидание). По той и другой команде

процессор начинает отсчитывать такты ожидания TW, которые

прекращаются при определённых внешних воздействиях. Из команды

останова HLT процессор может быть выведен двумя способами: подачей

начального сброса RESET или внешним прерыванием, что широко

используется при организации прерываний. В первом случае процессор

перейдёт к выполнению основной программы сначала, во втором – к

выполнению подпрограммы обслуживания прерывания. После выполнения

подпрограммы процессор обязан перейти к следующей за командой HLT

команде, следовательно, при необходимости возвращения к команде

останова в подпрограмме необходимо поставить команду JMP с указанием

адреса команды HLT.

При выполнении команды WAIT процессор аппаратно проверяет вход

TEST, когда процессор обнаружит на этом входе сигнал нулевого уровня,

состояние ожидания прекращается. Управление ожиданием с помощью

тандема WAIT–TEST позволяет осуществить синхронизацию, т. е. сопряжение

во времени работы процессора с внешними устройствами (например, с

арифметическим сопроцессором).

Другой способ вывода процессора из состояния ожидания заключается

в подаче запроса прерывания по входу INT. Необходимо отметить, что по

команде WAIT не происходит автоматического увеличения содержимого

103

указателя команд IP, поэтому после выполнения программы обслуживания

прерывания процессор вновь перейдёт к выполнению команды WAIT, т. е.

перейдёт в состояние ожидания. Таким образом, можно выполнять

прерывающие программы во время ожидания сигнала готовности TEST от

ВУ.

Команды синхронизации с арифметическим сопроцессором. Для

организации совместной работы основного процессора с сопроцессором

служит команда ESC. В первом байте команды находится пятиразрядный код

команды 11011 и трёхразрядное поле, расширяющее толкование конкретного

смысла операции. Во втором байте находится постбайт. Оба процессора

анализируют поток команд, и если получена команда с указанным кодом

операции, то сопроцессор дополнительно анализирует выводы QS0, QS1,

показывающие состояние очереди команд, чтобы определить именно первый

байт, а следовательно, это команда ESC. После чего сопроцессор переходит в

состояние обработки пришедшей команды. Более подробно этот процесс

будет рассмотрен при изучении арифметического сопроцессора.

2.5. Реализация микропроцессорной системы на базе 16-разрядных

микропроцессоров

2.5.1. Функционирование микропроцессора

2.5.1.1.Построение блока центрального процессора

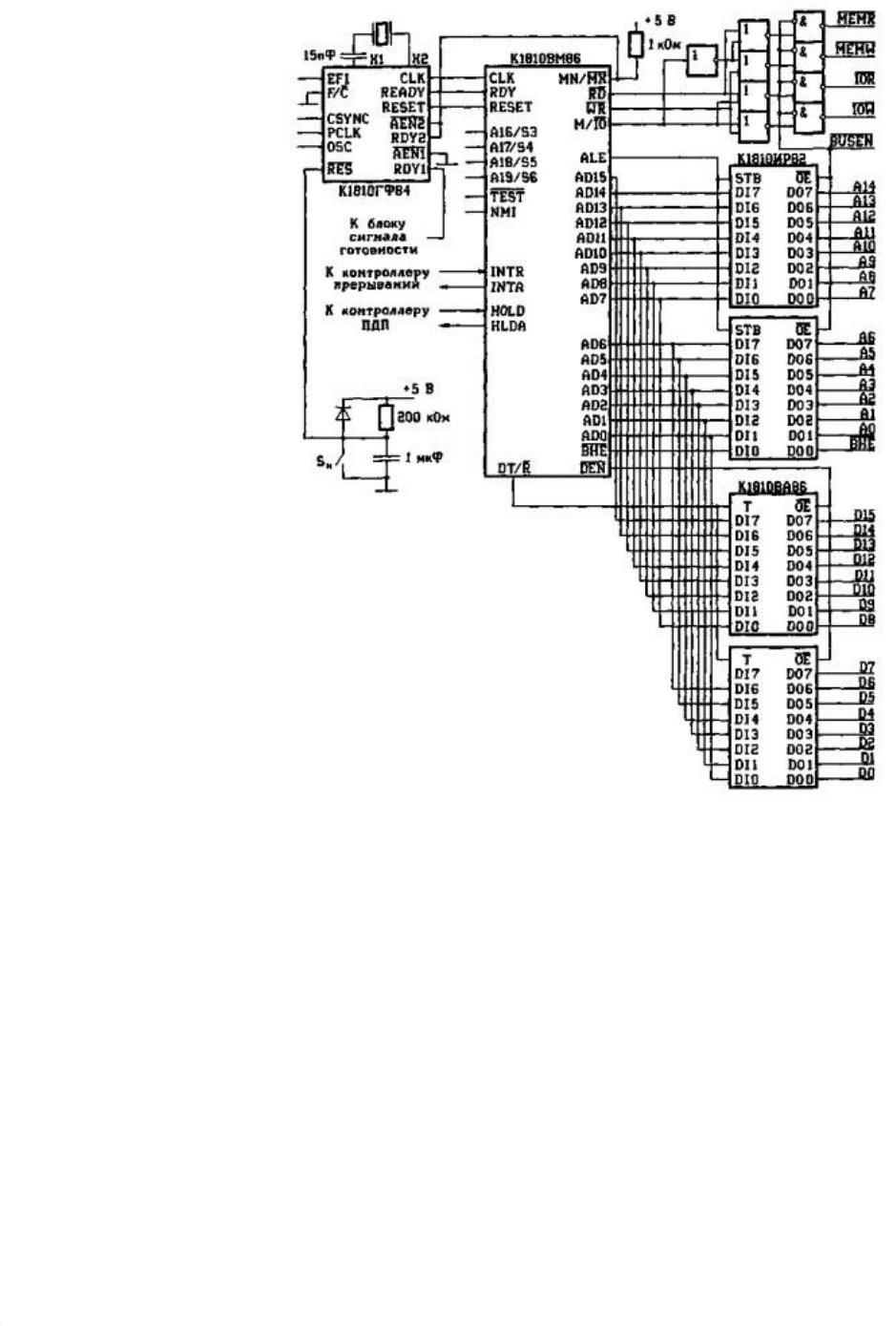

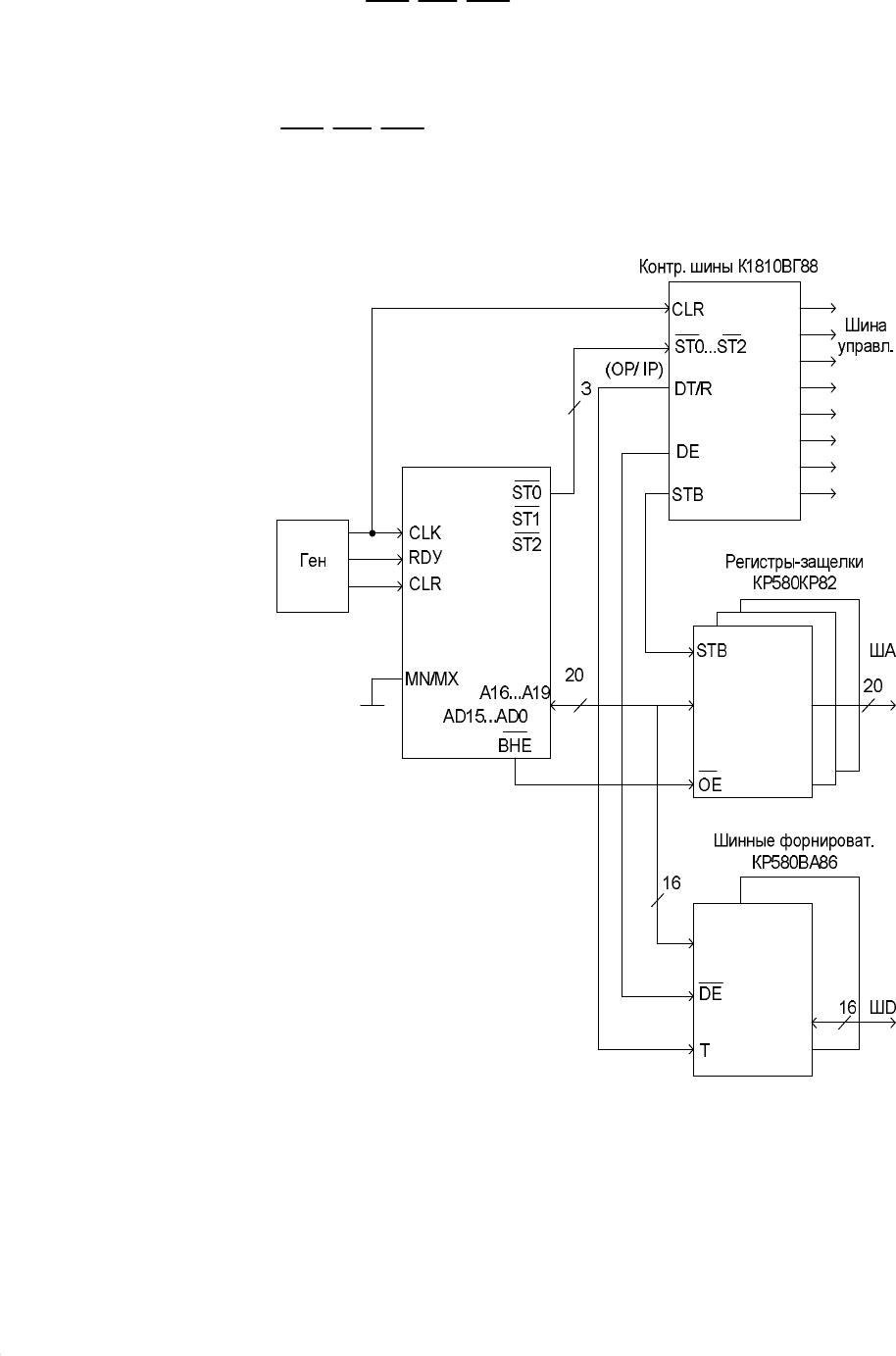

При разработке структуры блока ЦП (рис. 2.21) возникают задачи

разделения (демультиплексирования) шины адреса/данных (ШАД),

буферирования шин адреса (ША) и шин данных (ШД), а также

формирования системных управляющих сигналов для блоков памяти и

внешних усройств.

104

Рис. 2.21. Структурная схема ЦП на основе ВМ86

Первая задача решается с помощью ИС К1810ИР82/83, выполняющих

функции адресной защелки. Так как сигнал ВНЕ формируется в том же

интервале времени, что и адресные сигналы, то его также необходимо

зафиксировать в защелке. Поэтому изображенные на рис. 2.21 два 8-битовых

регистра К1810ИР82 обеспечивают запоминание 15 разрядов адреса. Для

доступа к памяти максимальной емкостью 1 Мбайт необходимо подключить

еще один регистр, на который подаются оставшиеся старшие разряды AD15,

A19/S 6 – A16/S3.

Вторая задача решается с помощью двунаправленных 8-битовых

шинных формирователей К1810ВА86/87, которые усиливают сигналы

системной шины данных.

105

Третья задача может быть решена с помощью комбинационных

логических схем, которые формируют требуемые управляющие сигналы на

основе сигналов

RD, WR и М/IO, вырабатываемых МП. Если в системе используется

адресное пространство ввода – вывода, изолированное от пространства

памяти, то целесообразно сформировать сигналы, аналогичные сигналам на

выходах системного контроллера К580ВК28: MEMR, MEMW, IOR, IOW. Эти

сигналы управляют запоминающими и внешними устройствами подобно

тому, как это делается в системах, построенных на основе МП К580ВМ80.

Роль формирователей сигналов могут выполнять элементы ИЛИ-НЕ (рис.

2.21) или дешифратор на три входа (например, К155ИД7). Если же в МПС

ввод – вывод организован с отображением на память, то сигнал М/ IO не

используется и на ЗУ и ВУ подаются сигналы RD и WR после усиления.

Используемые усилители и формирователи должны обеспечивать три

выходных состояния, чтобы можно было организовать прямой доступ к

памяти. В этом случае после перевода МП в состояние захвата эти

усилители переходят в третье состояние по сигналу РМ (BUSEN),

поступающему от контроллера ПДП. Если захват шин и обмен данными по

ПДП не предусмотрен, то необходимость в таком переключении отпадает.

2.5.1.2. Минимальный режим

Минимальный и максимальный режимы отличаются по своим

функциональным возможностям. Для введения минимального режима

контакт

/

MNMX

подключается к «1». Типичная конфигурация

минимального режима представлена на рис. 2.21. поскольку 16 младших

разрядов ША мультиплексированы с ШД, адрес необходимо фиксировать в

регистрах защелках.

Для 8-разрядных регистра К1810ИР82 (I8282), каждый из которых

рассчитан на 8 бит, запоминают адреса, один из разрядов используется для

фиксирования сигнала разрешения старшего байта шины

BHE

. Для доступа

ко всему объему памяти (1 Мбайт) необходимо включение в систему еще

одного регистра, на который следует подать пять старших адресных

разрядов: АD15 и А16

÷

А19. Для фиксирования адреса используется сигнал

STB

. Вход DЕ регистров-защелок позволяет перевести регистры в

высокоимпедансное состояние в режиме ПДП. В однопроцессорных

системах без контроллера ПДП этот контакт заземляется.

106

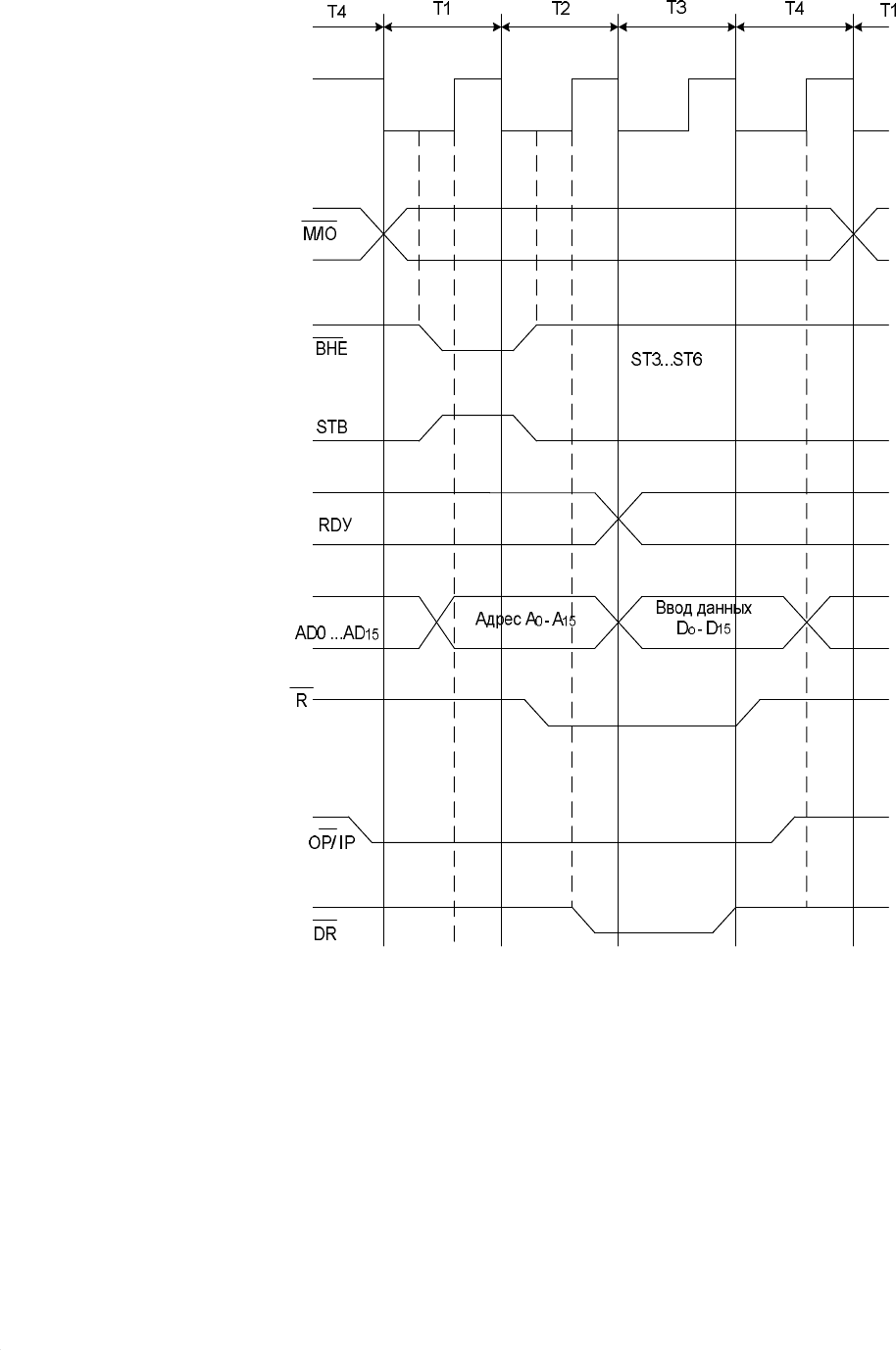

Рис. 2.22. Временные диаграммы последовательности чтения для min

режима КР1810ВМ86

107

Для управление взаимодействием с памятью и внешними устройствами

МП генерирует сигналы чтения

RD

, записи

WR

и обращения к памяти или к

ВУ

/

MIO

. С помощью внешней логики, (рис. 2.21), можно сформировать

сигналы ,

MEMRMEMW

, позволяющие разделить адресное пространство

памяти и ВУ.

В системе с несколькими интерфейсами требуются приемопередатчики

на ШД. Для этого предназначаются микросхемы К1810ВА86 (18286). Каждая

микросхема содержит 16 тристабильных элементов – 8 приемников и 8

передатчиков (драйверов). Следовательно, для обслуживания 8 линий ШД

18086 – две таких микросхемы.

Сигнал DE разрешения пересылки данных подается на вход

разрешения вывода DЕ шинных формирователей К1810ВА86. Направление

пересылки определяется сигналом

/

OPIP

, поступающим от процессора на

вход T (DT/

)

R

приемопередатчика. Процессор переводит линии

DE

и

/

OPIP

в высокоимпедансное состояние в ответ на запрос шины по линии

HLD

.

Иногда системная шина проектируется так, что сигналы адреса или

данных инвертируется. Поэтому микросхемы К1810ИР82 (I8282) и

К1810ВА86 (I8286) имеют свои полные аналоги I8283 и I8287,

осуществляющие инверсию сигналов при передаче со входов на выходы.

Все типы циклов по обмену информации могут быть объединены в 2

базовых цикла: чтения и записи. На рис. 2.22 представлены диаграммы

работы микропроцессора, работающего в минимальном режиме, для

машинного цикла «чтение». Машинный цикл (м. ц.) чтения начинается в

такте

1

T

с установки адресной информации и с подачи разрешения фиксации

адреса

STB

. Адрес запишется в буферах К1810ИР82 (или ИР83).

Сигнал

BHE

показывает, будет ли пересылаться только младший байт

(«1») или все слово («0»). В тактах Т1 – Т4 сигнал

/

MIO

указывает, что

является источником данных – память или ВУ.

В такте T2 завершается выдача адреса, и выходы буферов

014

AA

−

переводятся в 3-е состояние, на линиях

1619

AA

−

появляются

сигналы

3...6

STST

, которые сохраняются до конца Т4, начинается

управляющий сигнал

(4)

T

R

. Данные передаются в тактах Т3, Т4, при этом в

такте Т3 адресуемое устройство выдает сигнал готовности RДУ,

позволяющий синхронизировать скорость работы памяти и МП введением

между Т3 и Т4 дополнительных тактов ожидания, если на входе RДУ

окажется «0». Затем в такте Т4 сигнал

(4)

T

R

устанавливается в «1», тем

самым выводы адресуемого устройства устанавливаются в 3-е состояние и

освобождают системную ШД.

108

Сигнал

/

OPIP

в Т1–Т4 определяет сигналы формирователям ВА86

режим приема (т. е. направление), а сигнал DЕ разрешает передачу данных в

точке Т3. Чтение кода команды и данных осуществляется аналогично,

отличие в том, что данные направляются в блок регистров, а код операции в

регистр очереди команд.

Подключение ВУ в минимально укомплектованной структуре часто

осуществляется аналогично обращению к ячейкам памяти, т. е. используется

общее адресное пространство для памяти и внешних устройств (совмещенная

адресация). Преимущество такого способа подключения ВУ в том, что

появляется возможность использования большого числа команд,

предназначенных для обработки данных из памяти, вместо двух – команд

IN

и

OUT

.

2.5.1.3. Максимальный режим

Максимальный режим используется в структурах микропроцессорных

систем повышенной сложности. Он устанавливается при заземлении вывода

/

MNMX

. Режим характеризуется тем, что устанавливаются дополнительные

управляющие сигналы, обеспечивающие совместную работу

микропроцессора с другими микропроцессорами, арифметическими

сопроцессорами или процессорами ввода-вывода. При установке

максимального режима изменяется назначение восьми выводов

микропроцессора. Еще раз акцентируем внимание на этих выводах,

рассмотрев их в таблице 2.12.

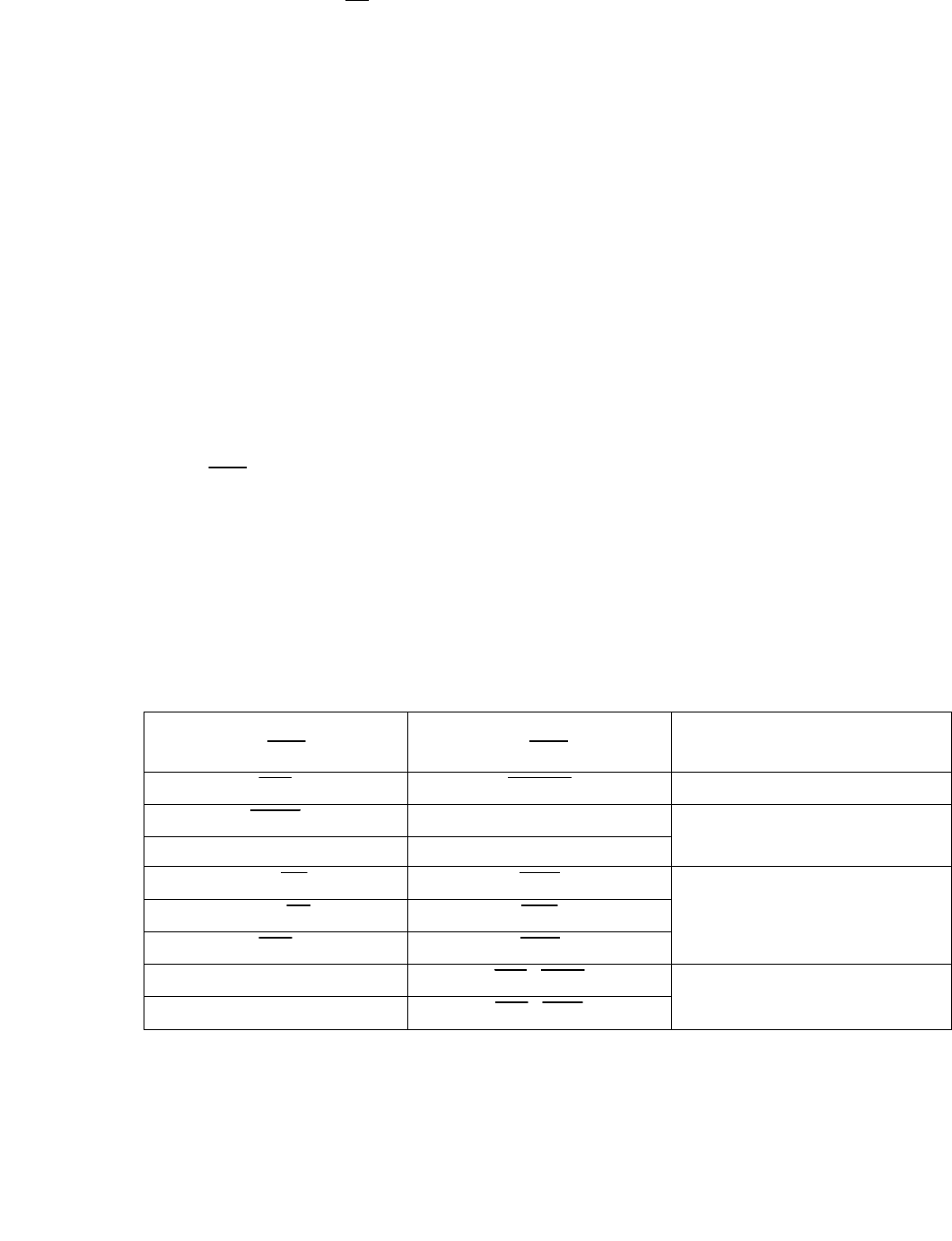

Таблица 2.12

Назначение восьми выводов МП в максимальном режиме

Минимальный режим

(/1)

MNMX

=

Максимальный режим

(/0)

MNMX

=

Назначение выводов в

максимальном режиме

WR

LOCK

Блокировка

INTA

0

QS

Состояние очереди команд

STB

1

QS

/

MIO

2

ST

Состояние МП

/

OPIP

1

ST

DE

0

ST

HLD

/0

ROGT

Запрос/предоставление

HLDA

/1

ROGT

На рисунке 2.23 приведена типичная конфигурация максимального

режима, на рисунке 2.24 временные диаграммы работы.

109

На выводы

0,1,2

STSTST

в тактах Т1, Т2 и Т4 выводится код состояния

микропроцессора, характеризующий текущий цикл и определяющий способ

использования ША/ШД. За счет кодирования кодов состояния освобождается

ряд выводов. Во время тактов Т3 и

TW

, когда шины не используются МП, на

выводах

0,1,2

STSTST

присутствует код 111. Код состояния позволяет

выработать все необходимые управляющие сигналы при помощи внешнего

средства – системного контроллера К18010ВГ88.

Рис. 2.23. Максимальный режим

110

Выводы

/

RQGTO

и

/1

RQGT

являются двунаправленными линиями,

причем вывод

/

RQGTO

имеет более высокий приоритет. Вывод служат для

захвата системной шины другими устройствами. Захват начинается с

поступления на один из входов /

RQGTO

и

/1

RQGT

запроса захвата, во

время очередного такта Т1 или Т4 микропроцессор подает на этот же вывод

ответственный сигнал разрешения захвата. В следующем такте

микропроцессор входит в режим захвата и устанавливает шины и ряд других

выводов в высокоимпедансное состояние. После окончания использования

системных шин ВУ сообщает об этом микропроцессору по тем же линиям.

Получив этот сигнал, микропроцессор возобновляет работу.