Онищенко Г.Б. и др. Автоматизированный электропривод промышленных установок

Подождите немного. Документ загружается.

чкигпе/тьный

«рази

чюкаё) адрес

"j

Ci/мнатор^S^

I

!

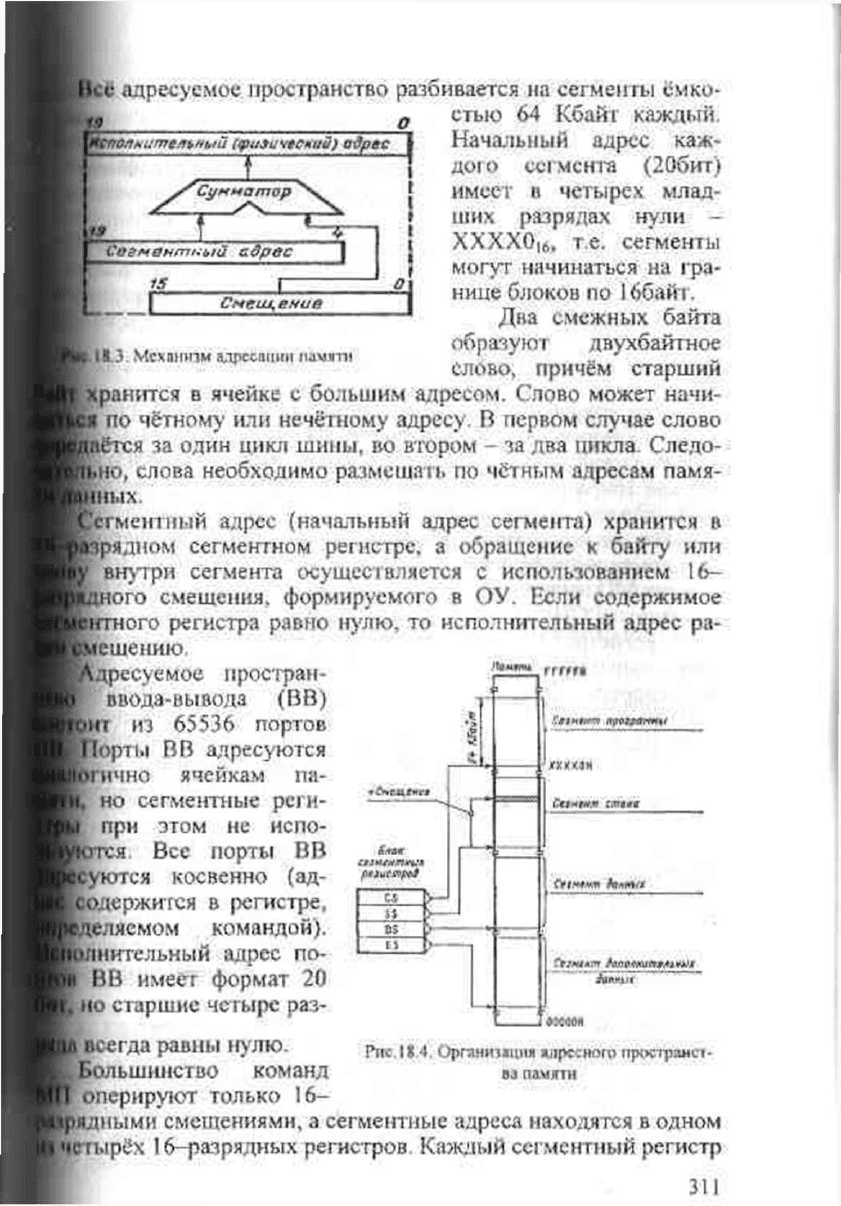

pkc адресуемое пространство разбивается на сегменты емко-

0

стью 64 Кбайт каждый.

Начальный адрес каж-

дою сегмента (20бит)

имеет в четырех млад-

ших разрядах нули -

ХХХХ0|

6

, т.е. сегменты

могут начинаться на гра-

нице блоков по 16байт.

Два смежных байта

образуют двухбайтное

слово, причём старший

Соёментный сОрес "]

15

:

Сыеш, p. sua

i!13. Механизм алреепшш намят

нится в ячейке с большим адресом. Слово может начи-

по четному или нечётному адресу. В первом случае слово

я за один цикл шины, во втором - за два цикла. Следо-

, слова необходимо размешать по чётным адресам памя-

IX.

ментиый адрес (начальный адрес сегмента) хранится в

дном сегментном регистре, а обращение к байту или

внутри сегмента осуществляется с использованием 16-

ого смещения, формируемого в ОУ. Пели содержимое

ого регистра равно нулю, то исполнительный адрес ра-

щению.

" ггг*гш

гсуемое простран-

ввода-вывода (ВВ)

•HI из 65536 портов

Ш1орты В В адресуются

"

1Чно ячейкам па-

но сегментные регн-

прн этом не испо-

;я. Все порты ВВ

1суютея косвенно (ад-

[содержится в регистре,

юмом командой),

тигельный адрес по-

ВВ имеет формат 20

но старшие четыре раз-

Sm*

puucnfvi

С4

$1

В»

Л $ И W-t tflfflfPtUt (

тон

Ct»iм« tariwir

CVtм^ми Mrtdii

Ctr/aian

Awawuwyifj w/

iun-iu

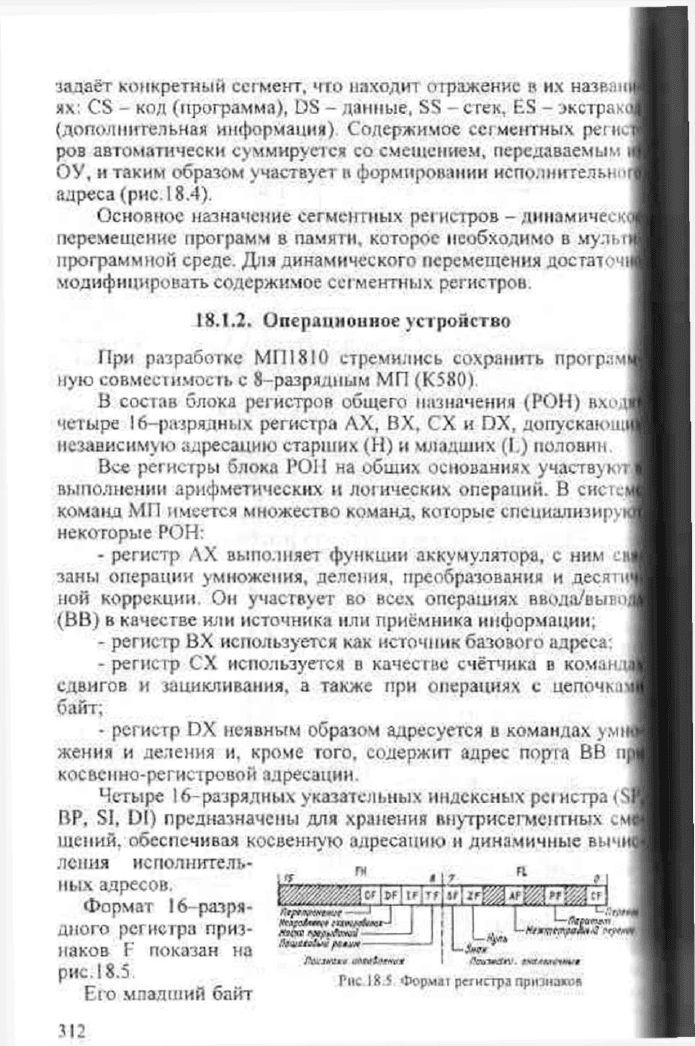

Рис, 18 4 Органимция *лрс:ного пространст-

ва памлтн

;гда равны нулю.

1ьшинств0 команд

Итерируют только 16-

(ными смещениями, а сегментные адреса находятся в одном

четырёх 16-разрядных регистров Каждый сегментный регистр

задаёт конкретный сегмент, что находит отражение в их назван

ях: CS - код (программа), DS - данные. SS - стек, ES - экстра к

(дополнительная информация) Содержимое сегментных регне

ров автоматически суммируется со смещением, передаваемым

ОУ, и таким образом участвует в формировании исполнительно

адреса (рис. 18.4).

Основное назначение сегментных регистров - дннамическ

перемещение программ в памяти, которое необходимо в мулы

программной среде. Для динамического перемещения достаток

модифицировать содержимое сегментных регистров.

18.1.2. Операционное устройство

При разработке МП1810 стремились сохранить програ.м

ную совместимость с 8-разрядным МП (К580).

В состав блока регистров общего назначения (РОИ) BXW

четыре 16-разрядных регистра ЛХ, ВХ, СХ и DX, допускают

независимую адресацию старших (Н) и младших (I.) половин

Все регистры блока POI1 на общих основаниях участвую

выполнении арифметических и логических операций. В систе

команд МП имеется множество команд, когорые спсциализиру

некоторые РОН:

- регистр АХ выполняет функции аккумулятора, с ним с;

заны операции умножения, деления, преобразования и десятг

ной коррекции. Он участвует во всех операциях ввода/выво

(ВВ) в качестве или источника или приёмника информации;

- регистр ВХ используется как источник базового адреса:

- регистр СХ используется в качестве счётчика в комам;

-

сдвигов и зацикливания, а также при операциях с цепочки

байт;

- регистр DX неявным образом адресуется в командах умг

жения и деления и. кроме гого, содержит адрес nopia ВВ п

косвенно-регистровой адресации.

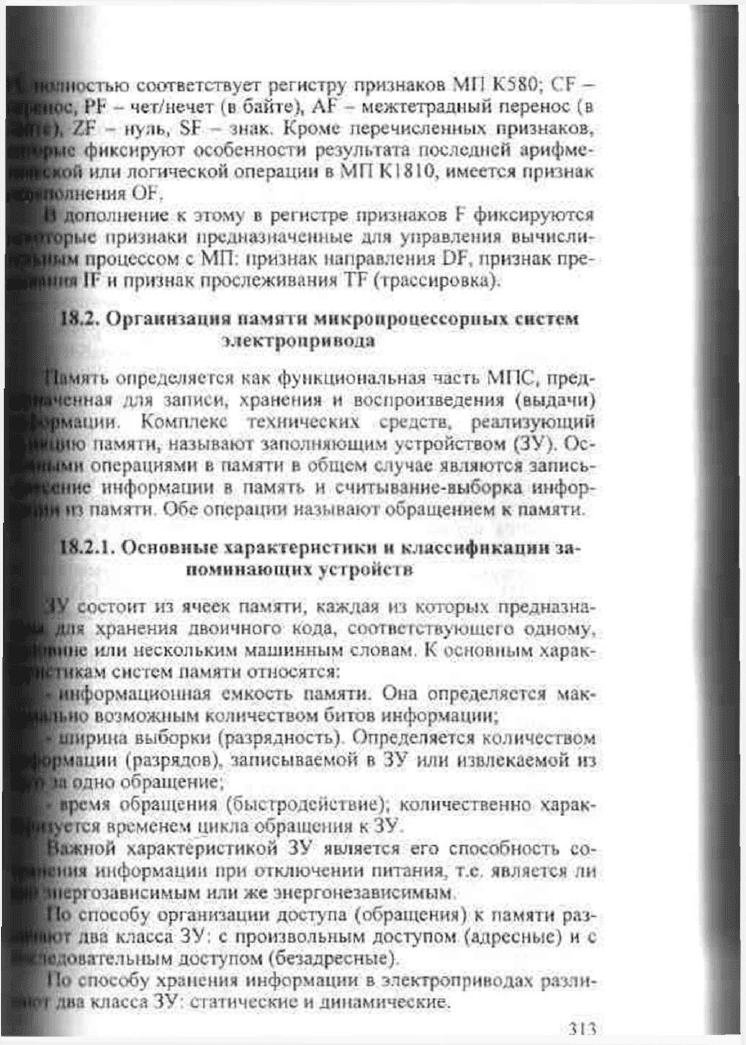

Четыре 16-разрядных указательных индексных pci истра

BP, SI, DI) предназначены для хранения внутрисегментных с,

щений. обеспечивая косвенную адресацию н динамичные выч*

ления исполнитель- ™

ных адресов.

Формат 16-разря-

дного регистра приз-

наков F показан на

рис. 18.5

Его младший байт

ШШШШШШШЕШЕШШШЕЗ

^Mtmttnfeba i

I— Ляг

Ашпмм

iMw Дммм I

Яeavtu\<. гмалмtim/i

РИС.18.S Форма! регистра признаков

:тью соответствует регистру признаков МП К580; CF -

PF - чег/нечет (в байте), AF - межтетрадный перенос (в

[ZF - нуль, SF знак. Кроме перечисленных признаков,

фиксируют особенности результата последней арифме-

или логической операции в МП К1810, имеется признак

*ения OF.

шолнение к этому в регистре признаков F фиксируются

Цэыс признаки предназначенные для управления вычнслн-

процессом с МП: признак направления DF, признак пре-

Ьл

П

и признак прослеживания TF (трассировка).

[18.2. Организация памяти микропроцессорных систем

электропривода

щь определяется как функциональная часть МПС, пред-

анная ;шя записи, хранения и воспроизведения (выдачи)

^ации. Комплекс технических средств, реализующий

||ю памяти, называют заполняющим устройством (ЗУ). Ос-

1н операциями в памяти в общем случае являются эапись-

Йие информации в память и считывание-выборка инфор-

(»п памяти Обе операции называют обращением к памяти.

\.2Л. Основные характеристики и классификации за-

поминающих устройств

)стоит из ячеек памяти, каждая из которых предназна-

)'я хранения двоичного кода, соответствующего одному,

|нс или нескольким машинным словам. К основным харак-

Й»кам систем памяти относятся:

>рмационная емкость памяти. Она определяется мак-

возможным количеством битов информации;

бйирина выборки (разрядность) Определяется количеством

Мании (разрядов), записываемой в ЗУ или извлекаемой из

[одно обращение;

№рсмя обращения (быстродействие), количественно харак-

:я временем цикла обращения к ЗУ.

(НОЙ характеристикой ЗУ является его способность co-

ffin* информации при отключении питания, т.е. является ли

швнеимым или же энергонезависимым

способу организации доступа (обращения) к памяти раз-

лва класса ЗУ: с произвольным доступом (адресные) и с

звательным доступом (безадресные).

Ко способу храпения информации в электроприводах разли-

\

два класса ЗУ' статические и динамические,

зп

По функциональному назначению большинство типов

можно разделить на следующие группы: сверхоперативные

(СОЗУ); оперативные ЗУ (ОЗУ); постоянные ЗУ (ПЗУ); пояуг

стоянные или перепрограммируемые ЗУ (ППЗУ); программнр

мые логические матрицы (ПЛМ), специальный вид постояни

памяти: буферные ЗУ (БЗУ), предназначенные для согласован

различных типов ЗУ между собой и с внешними устройствам

стековые ЗУ: внешние ЗУ (ВЗУ).

18.2.2. Сверхоперативные и оперативные запоминают nj

устройства (СОЗУ н ОЗУ)

СОЗУ - представляют собой набор регистров (РГ), содер"

мое которых непосредственно используется прн обработке

формации в МП. Такое ЗУ встроено в БИС МП и предпазначе

для хранения команд, операндов и результатов промежугочн'

преобразований. СОЗУ используется для расширения функн

нальных возможностей и повышения производительности МП.

ОЗУ - предназначено для хранения оперативной (порем

ной) информации, требующейся в процессе обработки, операн'

числа, программы, промежуточные результаты и т.д. Иногда О

называется памятью с произвольным доступом. Для ОЗУ в

можны режимы как считывания, так и записи информации. Вн

ренняя организация ОЗУ содержит большое число элементов

мяти (311) и имеет некоторую регулярную структуру. Сущест

ют ОЗУ со статическими и динамическими элементами памяти.

Статические ЭП способны хранить информацию (тол

один бит) как угодно долго, пока подается электропитание В

чествс такого ЭП используется статический триггер.

Динамические ЭП

способны хранить бит информации тол

короткое время (единица мс иди мкс). Поэтому для сохране»

информации необходимое время ее нужно периодически оби

лять. т.е. регенерировать В качестве такого ЭП может исполь

ваться электрический конденсатор. В динамических ЗУ вре

цикла считывания (записи) больше, чем в статических.

18.2.3. Постоянные запоминающие устройства

ПЗУ - это постоянное запоминающее устройство, содер-

мое которого не может быть заменено МП в ходе выполнен

рабочей программы и сохраняется при снятии питания систем

ПЗУ представляет собой память, работающую только в режи

считывания. ПЗУ как устройство памяти может работать в од и

ЗИ

режимов: чтение или программирование, т.е. в процессе

информации в него.

способу программирования выпускаемые полупроводни-

ПЗУ делятся на два типа: МПЗУ - масочные ПЗУ, в кото-

'формация заносится в процессе изготовления масочным

м; создаются они на базе полевых или биполярных ipan-

ППЗУ - электрически программируемые ПЗУ, в которых

"ция может быть занесена электрическим способом, т.е.

/екают в своем режиме программирование или репро-

эвание (перепрограммирование) с помощью электриче-

::гналов. Их называют также ПЗУ. программируемые поль-

м

li признак)' кратности программирования ЭГ1ПЗУ можно

ь на ПЗУ с однократным программированием (ППЗУ

)

и

«ОГОкратной сменой информации (РПЗУ). Стирание ни-

щи в РГ13У осуществляется двумя способами* элекгриче-

рание и воздействие ультрафиолетовыми (УФ) лучами.

^ построения MI1C управления электроприводами спспи-

Ьазработаны многоразрядные БИС ОЗУ КР537РУ8А и

УI; СППЗУ К573РФ2, К573РФЗ. К573РФ4, К573РФ5 и

5А; ЭППЗУ К573РР2 и ПЗУ K1809PEI [3-10].

.3. Организация ввода - вывода в мнкринроцессорных

системах

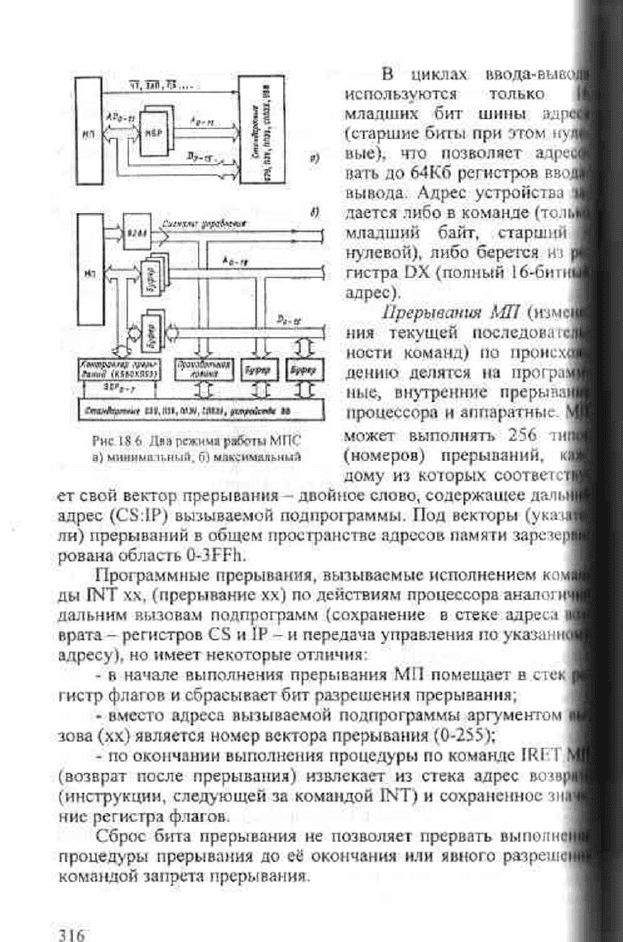

висимости от значения сигнала на управляющей линии

|$10 может работать в минимальном или максимальном

J3-7. 3-8].

•доказано на рис. 18.6,а в минимальном режиме, рассчи-

Ип простые системы. МП сам вырабатывает управляющие

ь| для системы (для памяти и УВВ), а в максимальном ре-

1рнс. 18.6,6). рассчитанном на большие, сложные системы,

срабатывает управляющие сигналы только для специализи-

Юй БИС контроллера шины, которая управляет системой.

(.18.6 приведено функциональное назначение линий управ-

ЦЛ в минимальном режиме.

Ксация ввода-вывода

Для обращения к устройствам вво-

"да процессор имеет отдельные команды FN и OUT, ре-

ом выполнения которых является формирование шинных

"Вц для чтения или записи одного или двух байт. Данные

нии могуг помещаться только в регистр AL или АХ и вы-

№я из этих же регистров.

Рис 18 6 Два режима работы МПС

а) мннимшьнмЛ. б) максимальный

В циклах ввода-выв

используются только

младших бит шины адр

(старшие биты при этом иу

:

вые), чзо позволяет адре

вать до 64Кб регистров в во.

вывода. Адрес устройства

лается либо в команде (тол

младший байт, старший

нулевой), либо берется из

гистра DX (полный 16-бип

адрес).

Прерывания МП (нам

ния текущей последоват

ности команд) по пронсх

дению делятся на програ

пыс, внутренние прерыпа

процессора и аппаратные,

можегг выполнять 256 тн

(номеров) прерываний, к

дому из которых со ответе

ет свой вектор прерывания - двойное слово, содержащее далг

адрес (CS:IP) вызываемой подпрограммы. Под векторы (ука

ли) прерываний в общем пространстве адресов памяти зарезе^

рована область 0-3FFh.

Программные прерывания, вызываемые исполнением ко

ды INT хх. (прерывание хх) по действиям процессора аналог»

дальним вызовам подпрограмм (сохранение в стеке адреса

врата - регистров CS и IP - и передача управления по указан»

адресу), но имеет некоторые отличия:

- в начале выполнения прерывания МП помещает в стек

гистр флагов и сбрасывает бит разрешения прерывания;

- вместо адреса вызываемой подпрограммы аргументом

зова (хх) является номер вектора прерывания (0-255);

- по окончании выполнения процедуры по команде IRHT

(возврат после прерывания) извлекает из стека адрес возе

(инструкции, следующей за командой INT) и сохраненное зн

ние регистра флагов.

Сброс бита прерывания не позволяет прервать вы пол н

процедуры прерывания до её окончания или явного разрешу

командой запрела прерывания.

но программное прерывание выполняется независимо от

1

флага IF Программные прерывания позволяют легко и

вызывать общеупотребительные процедуры из любого

^•а

без применения дальних вызовов.

ренине прерывания возбуждаются процессором по осо-

йовиям:

Ьрсрыванне 0 вырабатывается в случае переполнения при

ЦНн деления на 0;

прерывание I вырабатывается после выполнения каждой

Ы

при установленном флаге трассировки TF:

рывание 4 вырабатывается по команде INTO (Interrupt

^(прерывание по переполнению), если установлен флаг

ения OF.

аратные прерывания, в отличие от программных и внут-

I

прерываний, могут возникать асинхронно по отношению

ияемон программе. Они подразделяются на маскируемые

(скируемые. МП может воспринимать прерывания после

юния каждой команды, длинные строковые команды име-

Йккприятия прерываний специальные окна.

ируемые прерывания,вызываются переходом в высокий

[ сигнала на входе INTR (Interrupt Rci|uestX3nP-3anpoc

Ения, рис. 18.2) и выполняются при установленном флаге

Ьния (IF=l). В этом случае МП сохрзияет в стеке регистр

«сбрасывает флаг IF и вырабатывает два следующих друг

DM цикла подтверждения прерывания, в которых генери-

[ управляющие сигналы INTA # (Interrupt Acknowlege)

утверждение прерывания, рис. 18.2). Высокий уровень

: 1NTR должен сохраняться до подтверждения прерыва-

рвый цикл подтверждения - холостой, по второму им-

[

внешний контроллер прерываний передаёт по шине дан-

Г, содержащий номер вектора, обслуживающий данный

Кратного прерывания. Прерывание с полученным номе-

([Тора выполняется процессором так же. как и программ-

DTKa текущего прерывания может быть прервана не-

/ечым прерыванием, а если обработчик установит флаг

К другим маскируемым аппаратным прерыванием. После

|цого сброса флаг IF сброшен, и маскируемые прерывания

кны до их явного разрешения.

Шцаскируемые прерывания выполняются независимо от со-

№

флага IF по сигналу NMI (Non Mascable Interrupt). Высо-

эвень на этом входе вызовет прерывание с типом (векго-

, которое выполняется так же. как и маскируемое. Его об-

r, I

i— m

работка не может прерываться под действием сигнала на и

NMI до выполнения команды IRhl .

Управление МП в режиме прямого доступа к памяти (Ц

На вход запрос МД11 от контроллера быстродействующего ви|

него устройства поступает сигнал запроса Г1ДП. По окончи!

текущего цикла передачи по шине МП переводит буферные

мы шины AD0-19 и некоторых управляющих сигналов ь выс

импедансное состояние и формирует сигнал подтверждение

жима прямого доступа к памяти (ППДП), по которому ynpai

ние шиной передаётся контроллеру внешнего устройства. Из

стояния «приостановки» выполнения программы МГ1 выходи

окончании си! нала ЗПДИ.

18.4. Работа устройства управления МП

На рис. 18 7 показана временная диаграмма МП КР18КЩ

[2-1]. Модель дискретного машинного времени лая МП зада^

на входе СС синх-

росигналом от внеш-

него генератора (fcc=-

5МГц). Каждый ма-

шинный цикл на МП

состоит из четырёх

тактов, которым соот-

ветствуют состояния

Tl, Т2, ТЗ, Т4 автома-

та управления МП.

Между тактами ТЗ и

Т4 с помощью сигнала готовности ГТ можно ввести пронзв

нос число состояний ожидания 7'

гыг

, «гто обеспечивает МП

можность работы с любым гипом внешних медленно деист

ишх устройств.

Каждый машинный цикл МП представляет собой цикл

ны, так как МП а так же П, каждого МЦ выдаёт на линии д|

19 код адреса памяти н формирует сигнал сопровождения и ц,

тнфикации информации разрешения регистра адреса (PPA)j

этому сигналу код адреса должен быть обязательно зафиксирс

па внешнем регистре, так как в следующих тактах машиш«|

цикла на шине осуществляется передача данных Кроме г

тактах Т2-Т4 по линиям А16-19 передаётся код состояния sfl

который идентифицирует тип машинного цикла в минимальИ|

режиме.

Рис 18.7 Временная лиыраыыа работы МП

временно с передачей адреса по шине МП может фор-

сигнал передачи байта (ПБ), который сопровождает

t байта данных по линиям AD8-15. В такте Т1 по шине

^передаётся адрес, а в тактах Т2-Т4 принимается или пе-

II двухбайтовое слово Стробируюшнй сигнал чтения

используются для управления режимом работы регистра

памяти или УВВ' В режиме прямого доступа к памяти

ГГ переводится в высокоимпсдансное состояние. Стробн-

сигнал подтверждения прерывания (Г1ПР ) используется

,а в МП вектора прерывания из котроллера УВВ, запро-

Ъ

прерывание. В режиме прямого доступа к памяти линия

водится в высокоимпсдансное состояние,

[ал готов (ГТ) используется МП в качестве сигнала под-

пил окончания передачи данных из памяти или порта

^тройство управления МП опрашивает значение сигнала

ГТ в начале такта ТЗ и в зависимости от него переходит

1ЯНИЮ Т

ож

или к состоянию^.

|Ь«ал обмена данными (ПЕР/ПР) управляет работой шнн-

веров и определяет направление передачи из МП в па-

В или в МП из памяти/YBB. Управляющий сигнал стро-

пя данных (CD) формируется в МП при обращении к

И УВВ в тактах передачи данных по шине, а так же ма-

I

цикле подтверждения прерывания Сигнал запись (ЗАП)

вет действующее нулевое значение в циклах записи в

ft вывода информации в адресуемый порт УВВ.

18.5. Особенности МП семейства х8б

18.5.1. Процессоры 80186/80188 [3-Я|

Иессоры i80186/80188 и их модификации 80C186/80CI88

представляют нового поколения архитектуры: как и

{, они являются процессорами с 16-разрядной внутренней

рой и программно совместимы с 8086. Разрядность ши-

i - 20бит, шины данных у 80186 - 16бит, у 80188 - 8бит

бцсссоры имеют встроенные периферийные контроллеры

^аний, прямого доступа к памяти, трехканальный таймер и

I синхронизации. Процессоры 80С186/88 имеют средсг-

пения энергопотреблением, есть их модификации со

Внными последовательными портами и контроллерами рс-

Цции динамической памяти.

18.5.2. Процессор $0286

Процессор 80286 представляет второе поколение

разрядных процессоров. Он имеет специальные средства дня

боты в многопользоватедьных и многозадачных системах. Са

существенным отличием от 8086/88 является механизм упра:

ния адресацией памяти, который обеспечивает четырёхуро

вую систему данных и по дде ряску виртуальной памяти. Си

альные средства предназначены для поддержки механизма л

ключения задач. Процессор имеет расширенную систему ком

которая кроме команд управления защитой включает все ко

ды 8086 и несколько новых команд обшего назначения. Про

сор может работать в двух режимах:

8086 Real Address Mode - режим реальной адресации (

ный режим), полностью совместимый с 8086. В этом ре-

возможна адресация до

1

Мбайт физической памяти.

Protected Virtual Address Mode - защищенный режим ви

апьной адресации (защитный режим). В этом режиме нроце

позволяет адресовать до 16Мб физической памяти, через кот

при использовшгии механизма страничной адресации могут

бражаться до ГГб виртуальной памяти каждой задачи. Сие

команд в этом режиме так же включает набор команд 8086,

ширенный для обеспечения аппаратной функции супере'

многозадачной операционной системы и виртуальной памяти

По составу и назначению в реальном режиме регистры 8

в основном совпадают с регистрами 8086/88. Изменения ка-

назначения бит регистра флагов и использования сегмситны.

гистров в защищенном режиме МП 80286 имеет 16-битную

ну данных и очередь команд

1

ббайт. За счёт архитектуры со

щено время выполнения операций; процессор 80286 с такт

частотой 12,5МГц работает более чем в 6 раз быстрее, чем 80

частотой 5МГц.

18.5.3. 32 - разрядные процессоры

Первыми 32 - разрядными процессорами фирмы Intel б

процессоры i386. Эти процессоры вобрали в себя все свой

своих 16-разрядных предшественников 8086/88 и 80286

обеспечения программной совместимости с огромным обьё:

ранее написанного программного обеспечения. В них преодол

очень жёсткое ограничение на длину непрерывного сегмента

мяти - 64Кб. В защищенном режиме 32-битных процессоров

составляет 4Гб - предела физически адресуемой памяти. Все

ры имеют поддержку виртуальной памяти ооъёмом до

строенный блок управления памяти поддерживает меха-

аентации и страничной трансляции адресов. Процсеео-

ечивают четырехуровневую систему зашиты памяти и

|вода. переключения задач. Они имеют расширенную

оманд, включающую все команды 8086, 80286 Процес-

работать в двух режимах, между которыми обеспечи-

аточно быстрое переключение в обе стороны:

Р Address Mode - режим реальной адресации (реальный

олностыо совместимый с 8086. В этом режиме возмож-

цня до I Мб физической памят и

ectcd Virtual Address Mode - защищенный режим в и рту-

сацни (защипанный режим). В этом режиме происс-

пяет адресовать до 4Гб физической памяти, через кото-

спользовании механизма страничной адресации могут

ься до I6T6 виртуальной памяти каждой задачи. До-

м является Virtual 8086 Mode - режим виртуального

ра 8086 Этот режим является особым состоянием зада-

ренного режима, в котором процессор функционирует

ссоры могут оперировать с 8, 16 и 32-битпымн опе-

роками байт, слов и двойных слов, а также с битами.

|н полями и строками бит. В архитектуру процессоров

едства отладки и тестирования

пне 32-разрядных относятся: 386, 486, Pentium. Pentium

itium 2.

троенные микропроцессорные системы управления

по 21 века, по мнению специалистов в области автома-

тного электропривода и систем управления, является

широкого внедрения систем встроенного управления

внием - высокопроизводительных и надежных цнфро-

троцессорных систем управления, интегрированных в

[ машину, механизм, прибор, изделие станок, робот и

енной системой управления называется система управ-

руктнвно интегрированная в оборудование. Напри-

£гсма управления, встроенная в статический преобразова-

ы для асинхронных двигателей представляет собой,

Ьнло. одно- или многоплатную микроЗВМ с необходи-

мы интерфейсов для обеспечения как непосредствен-

Нравлеиия инвертором и приводом в целом, так и взаимо-