Иванов Ю.И., Югай В.Я. Интерфейсы средств автоматизации

Подождите немного. Документ загружается.

81

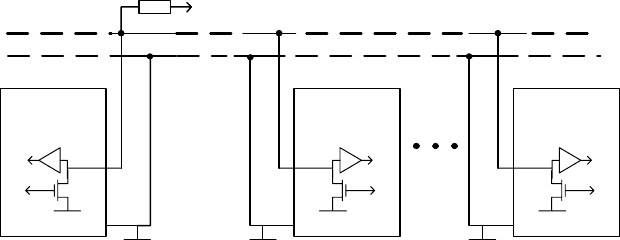

2.4. Приборный интерфейс 1-W

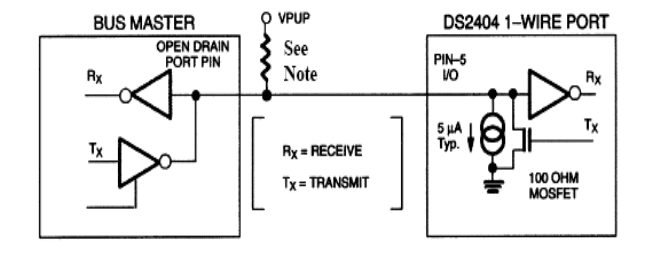

Разработанный фирмой Dallas Semiconductor интерфейс 1-W (1-Wire) по

основным свойствам и алгоритмам обмена данными во многом подобен ин-

терфейсу I2C. Особенности и ограничения интерфейса 1-W связаны с пере-

дачей всех необходимых сигналов по единственной сигнальной шине (рис.

2.33). Интерфейс – одномастерный, с единственным управляющим узлом

1W-Master, и количеством ведомых узлов 1W-Slave, ограничиваемым

нагрузочной способностью приемопередатчиков и

паразитными параметрами

сигнальной цепи. Интерфейс также называют сетью MicroLAN.

Рис. 2.33. Интерфейс 1-W.

Интерфейс 1-W предусматривает передачу данных с двумя скоростями:

стандартной скоростью – 15,3 кбит/с и повышенной скоростью – 100 кбит/с.

Скорость задается при начальной настройке интерфейса. Так как протокол

обмена требует передачи и тактовых, и информационных сигналов по един-

ственной сигнальной шине, временные соотношения

между сигналами долж-

ны жестко выдерживаться и строго соответствовать скорости передачи дан-

ных. Начало битового временного интервала определяется по падающему

фронту сигнала на шине, формируемого узлом 1W-Master. Все остальные из-

менения сигналов и их прием в этом битовом интервале должны выполняться

только в определяемые протоколом интервалы времени. Эти интервалы вре-

мени

различны для разных скоростей передачи.

При отключенных внутренних источниках питания приемо-передатчики

узлов 1W-Slave могут работать, потребляя необходимый небольшой ток от

сигнальной шины. Каждый узел имеет уникальный 64 битовый адрес (ID).

Этот адрес формируется при изготовлении устройства, в протоколе интер-

фейса 1-W называется ROM-номером и имеет следующую структуру: 8 бит –

+5

B

GND

1W-Master

RxD

TxD

GND

1W-Slave

RxD

TxD

GND

1W-Slave

RxD

TxD

82

код производителя, 48 бит – серийный номер устройства, 8 бит – контрольное

поле адреса по алгоритму CRC с образующим полиномом (X

8

+ X

5

+ X

4

+ 1).

Отдельный цикл передачи данных в протоколе 1W называется транзакци-

ей и состоит из следующих этапов: передача инициализационной последова-

тельности (начало транзакции), передача ROM команды (адресация транзак-

ции), передача команды (управление транзакцией), передача данных (тран-

закция). Транзакция всегда выполняется под управлением узла 1W-Master, он

задает начало транзакции инициализационной последовательностью и фор-

мирует сигналы для

выделения каждого битового интервала независимо от

этапа транзакции и направления передачи данных. Как указывалось ранее,

узлы 1W-Slave имеют право влиять на состояния сигнальной шины только в

строго определенные интервалы времени.

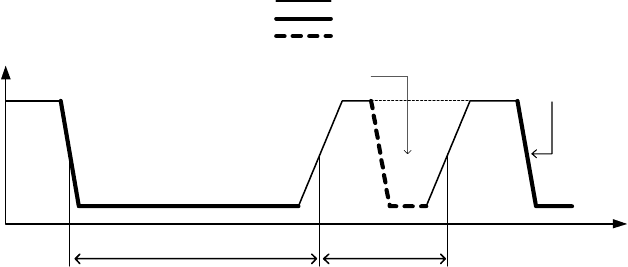

Инициализационная последовательность (рис. 2.34) начинается сигналом

"Reset" – низкий уровень сигнальной шины непрерывно в течение 8-10 бито-

вых интервалов (t

RSTL)

, формируемый узлом 1W-Master. После возврата сиг-

нальной шины в высокое состояние 1W-Master принимает сигналы присутст-

вия (низкий уровень шины, передаваемый всеми узлами 1W-Slave) в течение

интервала t

RSTH

(рис. 2.34). Хотя бы один узел должен передать сигнал при-

сутствия на шине для продолжения транзакции. После приема сигнала

присутствия 1W-Master переходит к формированию 1-го такта передачи

ROM команды.

Рис. 2.34. Сигналы инициализационной последовательности

После приема сигнала "Reset" и передачи сигнала присутствия все 1W-

Slave переходят в режим приема ROM команды, а адресованный в этой ко-

манде узел принимает далее команду управления. ROM команды и команды

управления имеют однобайтовый формат, разновидности команд, выполняе-

мых узлами 1W-Slave, зависят от реализуемых ими функций. На последнем

уровень сигнала формируется

резистором шины

узлом 1W-Master

узлом 1W-Slave

U

t

t

RSTL

t

RSTH

передача сигнала

Reset

прием сигнала

присутствия

начало 1-го такта

83

этапе транзакции выполняется заданная в команде управления передача дан-

ных либо передается подтверждение выполнения другой заданной операции.

Фирма Dallas Semiconductor [www.dallas.com] выпускает набор специали-

зированных компонентов, предназначенных для построения однопроводной

сети [www.rtcs.ru]. Базовым элементом является адресуемый ключ DS2405,

имеющий в своем составе 1W интерфейс, построенный по КМОП техноло-

гии, и управляемый ключ (N - канальный полевой транзистор с

открытым

стоком). Управление работой адресуемого ключа осуществляется независимо

от присутствия в сети других таких же приборов. Применение других компо-

нентов таких, как сдвоенный адресуемый ключ, контроллер двухпортовой

памяти, цифровой термометр, часы, счетчики, ветвители сети и т.п., расши-

ряет возможности построения сети в промышленных и бытовых приложени-

ях (см. табл. 2.5).

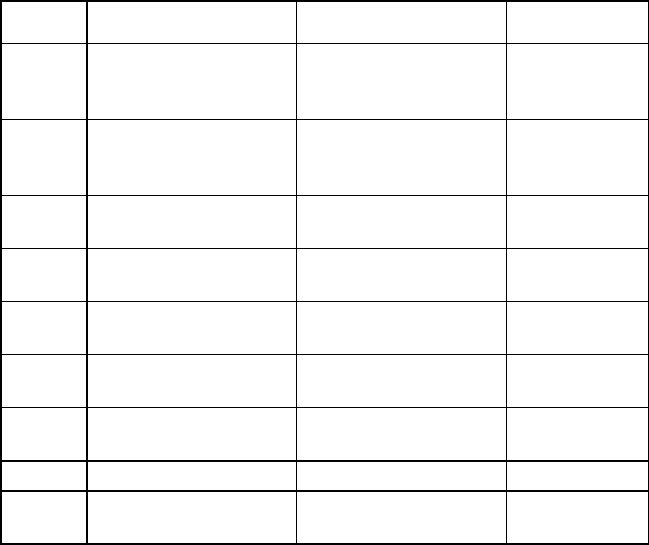

Таблица 2.5

Тип ИС Описание Особенности Тип корпуса

DS1822

Цифровой термометр с

программируемым

разрешением

точность 2.0 °С TO-92, SOIC-8

DS18B20

Цифровой термометр с

программируемым

разрешением

точность 0.5 °С,

24 бит EEPROM

TO-92, SOIC-8

DS18S20

Высокоточный цифро-

вой термометр

точность 0.5 °С,

16 бит EEPROM

TO-92, 8- SOIC

DS2401

Кремниевый серийный

номер

-

TO-92, SOT-

223, CSP

DS2404

Двухпортовое ОЗУ +

часы

4096 бит RAM 16- SOIC

DS2405 Адресуемый ключ -

TO-92, SOT-

223, TSOC

DS2406

Сдвоенный адресуе-

мый ключ с памятью

1024 бит EPROM TO-92, TSOC

DS2409 Ветвитель сети - TSOC

DS2417

Часы реального време-

ни с прерыванием

- TSOC

84

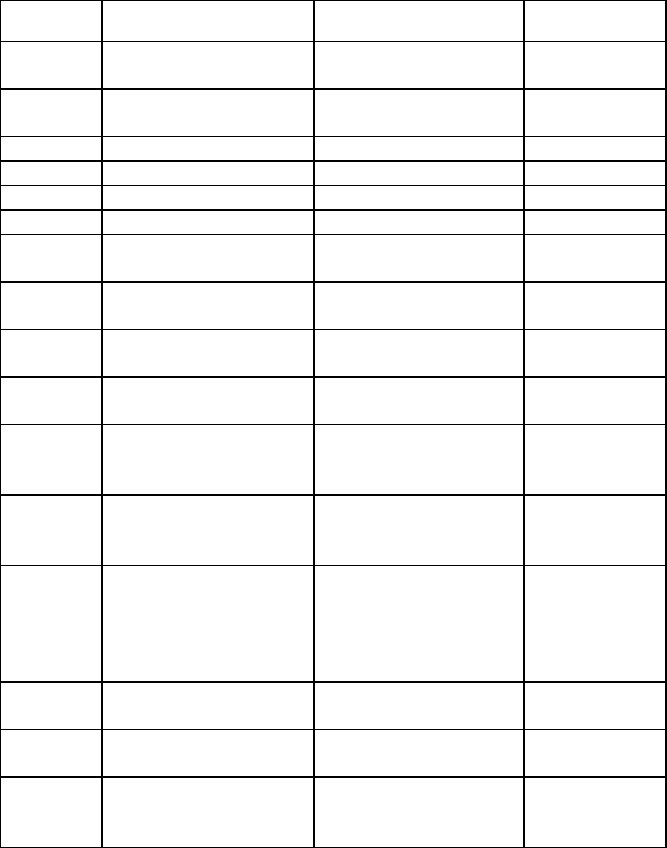

Продолжение табл. 2.5

Тип ИС Описание Особенности Тип корпуса

DS2422 1-проводной цифро-

вой термометр

512 байт RAM SO-24

DS2423 1-Wire RAM with

Counters

4096 бит RAM TSOC

DS2430A 1-Wire EEPROM 256+64 бит EEPROM TO-92, TSOC

DS2433 1-Wire EEPROM 4096 бит EEPROM PR-35, SOIC

DS2450 4 канальный АЦП - SOIC

DS2480B драйвер сети - SOIC

DS2490 преобразователь USB

в 1-Wire сеть

- SOIC-16

DS2502 EPROM с однократ-

ной записью

1024 бит EPROM TO-92,SOIC-

8, CSP

DS2505 EPROM с однократ-

ной записью

16384 бит EPROM TO-92, TSOC

DS2506 EPROM с однократ-

ной записью

65536 бит EPROM PR-35, SOIC

DS2740 Высоко точный изме-

ритель заряда

Измерение двуна-

правленного тока с

15 битной точностью

µMAX-8

DS2761 Высокопрецизионный

контроллер Li+ бата-

реи

16 байт памяти

SRAM общего назна-

чения

TSSOP-16

DS2770 Контроллер заряда и

монитор батареи

Измерение темпера-

туры с разрешением

0.125°С, 16 байт

SRAM общего назна-

чения

TSSOP-16

DS2890 цифровой потенцио-

метр

- TSOC-6, TO-

92

DS9502 диод электростатиче-

ской защиты

- TSOC

DS9503 диод электростатиче-

ской защиты с рези-

стором

- TSOC

85

Однопроводная сеть с интерфейсом 1-Wire (рис. 2.35) может эффективно

применяться в системах охранной сигнализации, контроля доступа, сбора и

обработки данных и т.п., например, iButton.

Обмен данными в iButton производится через интерфейс 1-Wire. Питание

устройства iButton получают из сигнального проводника, заряжая внутрен-

ний конденсатор в моменты, когда на шине нет обмена данными. Скорость

обмена достаточна

для передачи данных в момент касания контактного уст-

ройства.

Протокол интерфейса 1-Wire обеспечивает возможность работы с множе-

ством устройств iButton, подключенных параллельно к однопроводной шине.

Команды интерфейса позволяют запросить адреса (ID) всех iButton, подклю-

ченных в данный момент к линии, и затем работать с конкретным устройст-

вом, переведя остальные в режим ожидания. Управление линией

данных и

выдачу команд производит ведущее устройство (1W-Master), в качестве ко-

торого может использоваться любой микроконтроллер или персональный

компьютер (ПК). Для контроля данных используется вычисление контроль-

ного кода (CRC), а также аппаратный промежуточный буфер в ОЗУ iButton.

Данные сначала записываются в этот буфер, затем ведущий проверяет их

правильность, и только после этого выдает команду

ведомому устройству для

их копирования из буфера в основную память.

Для подключения iButton к персональному компьютеру фирмой Dallas

Semiconductor выпускаются адаптеры, преобразующие сигналы стандартных

портов компьютера (RS-232, LPT и USB) в сигналы 1-Wire. Программные

драйверы и комплект разработчика iButton TMEX SDK свободно доступны

на сайте фирмы, посвященном iButton [www.ibutton.com].

Рис. 2.35. Сетевая организации MicroLAN

86

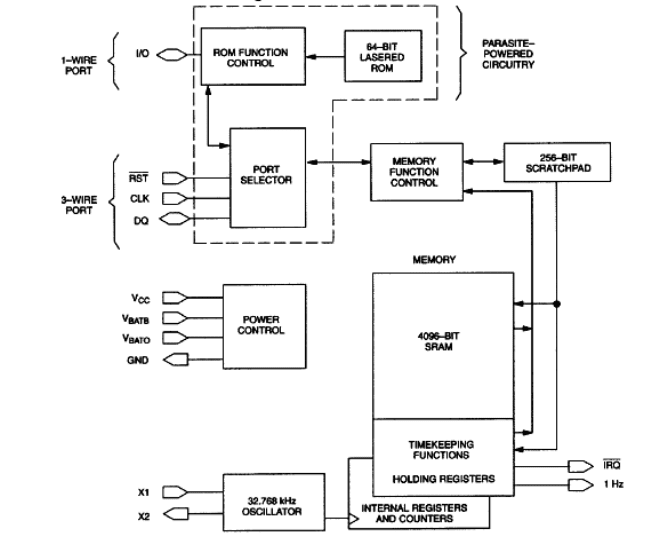

В качестве примера на рис. 2.36 показана структурная организация мик-

росхемы часов реального времени DS2404, а на рис. 2.35 – схема подключе-

ния к ведущей микросхеме, например, микроконтроллеру.

Рис. 2.36. Структурная схема DS2404

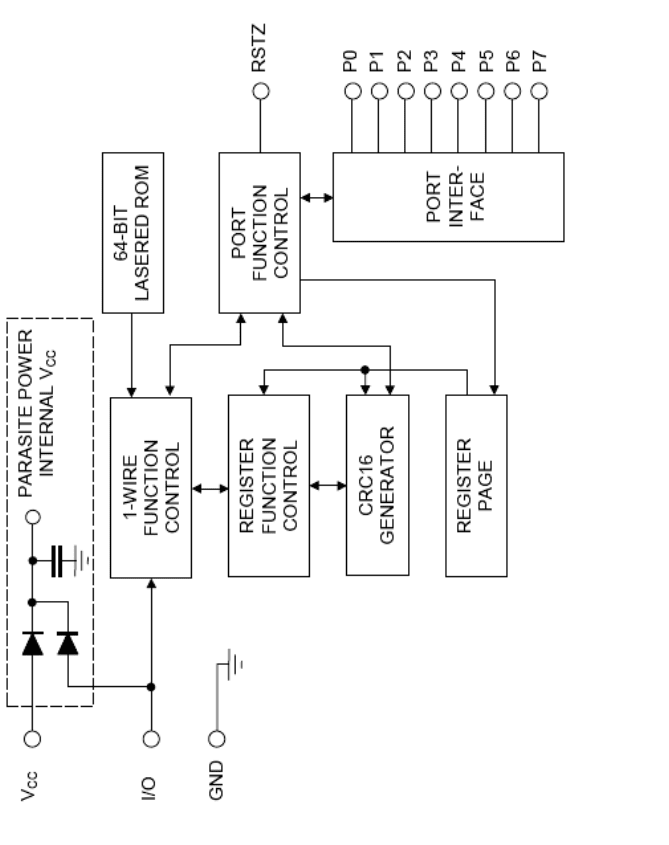

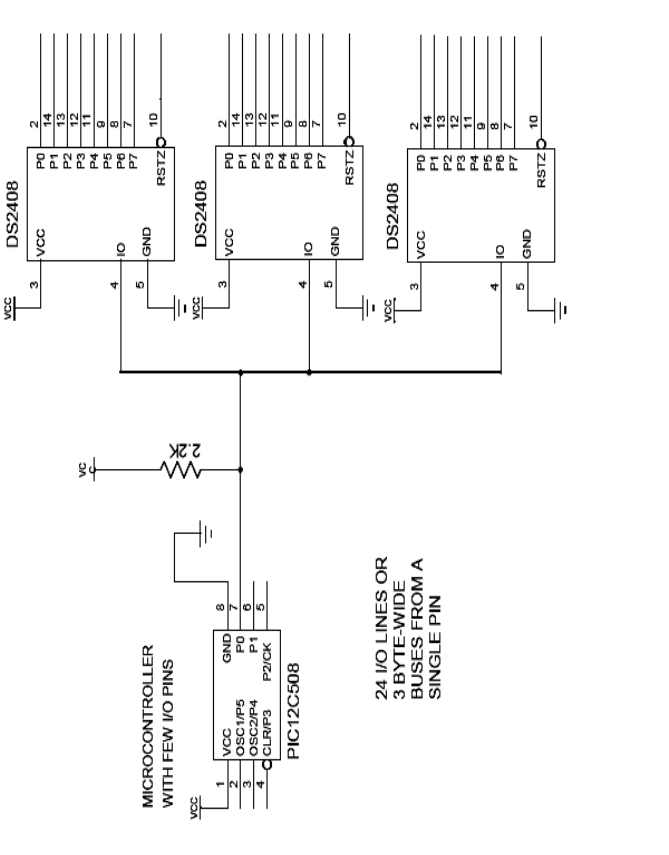

Компания Dallas Semiconductor начинает выпуск микросхемы DS2408 – 8-

канального адресуемого ключа с интерфейсом 1-Wire. Новый двунаправлен-

ный расширитель портов работает со стандартным интерфейсом Dallas

Semiconductor 1-Wire. Микросхема DS2408 (рис. 2.37)

хорошо подходит для

применений, в которых требуется большое число портов ввода/вывода на

удаленной периферии или системе, в тех случаях, когда управляющее уст-

ройство имеет недостаточное число доступных портов. Кроме того, несколь-

ко микросхем DS2408 могут работать на одной шине 1-Wire независимо друг

от друга.

87

Рис. 2.37. Функциональная схема ИС DS2408

88

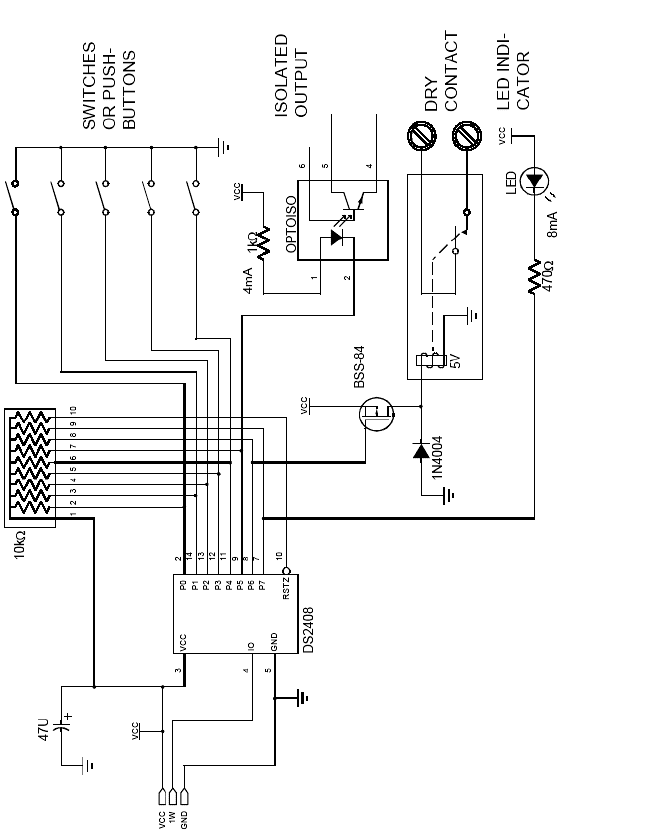

Микросхема DS2408 – двунаправленный порт с 8 каналами ввода/вывода,

управляемый по одной сигнальной линии интерфейса 1-Wire. Выходы 8 ка-

налов выполнены по схеме с открытым коллектором и имеют максимальное

сопротивление 100 Ом. В новой микросхеме реализован вывод строба досто-

верности данных, который может использоваться для защелкивания вход-

ных/выходных данных, управлять преобразованием данных во внешней

схе-

ме или работать с шиной данных микроконтроллера. Состояние выводов мо-

жет быть сохранено во внутреннем регистре для фиксирования мгновенных

значений. Эта функция полезна для поддержки работы клавиатуры или опро-

са кнопок (рис. 2.38).

Каждый DS2408 содержит 64-разрядный номер, который записан в ПЗУ

лазером на этапе производства микросхемы, что гарантирует уникальность

каждого

прибора и абсолютную идентификацию в сети. Большое число мик-

росхем DS2408 может быть подключено на одну шину 1-Wire независимо

друг от друга. Управление DS2408 выполняется по стандартному интерфейсу

1-Wire, который реализуется минимальными аппаратными средствами

управляющего устройства (одним выводом порта ввода/вывода микрокон-

троллера)

Например, один канал порта ввода/вывода микроконтроллера может

управлять тремя DS2408

и обеспечивать доступ к 24 дополнительным кана-

лам ввода/вывода (рис.2.39). Этот канал ввода/вывода микроконтроллера

должен аппаратно или программно поддерживать все функции интерфейса 1-

Wire. Кроме того, увеличение числа доступных каналов ввода/вывода связано

с ограничением скорости передачи данных. Конечно, для очень многих при-

менений время доступа к данным в единицы мс

вполне приемлемо.

89

Рис. 2.38. Схема подключения двухпозиционных устройств к DS2408

90

Рис. 2.39. Схема “расширения” параллельных портов микроконтроллера