Хмелевский И.В., Битюцкий В.П. Организация ЭВМ и систем. Однопроцессорные ЭВМ. Часть 4

Подождите немного. Документ загружается.

70

====================================================================

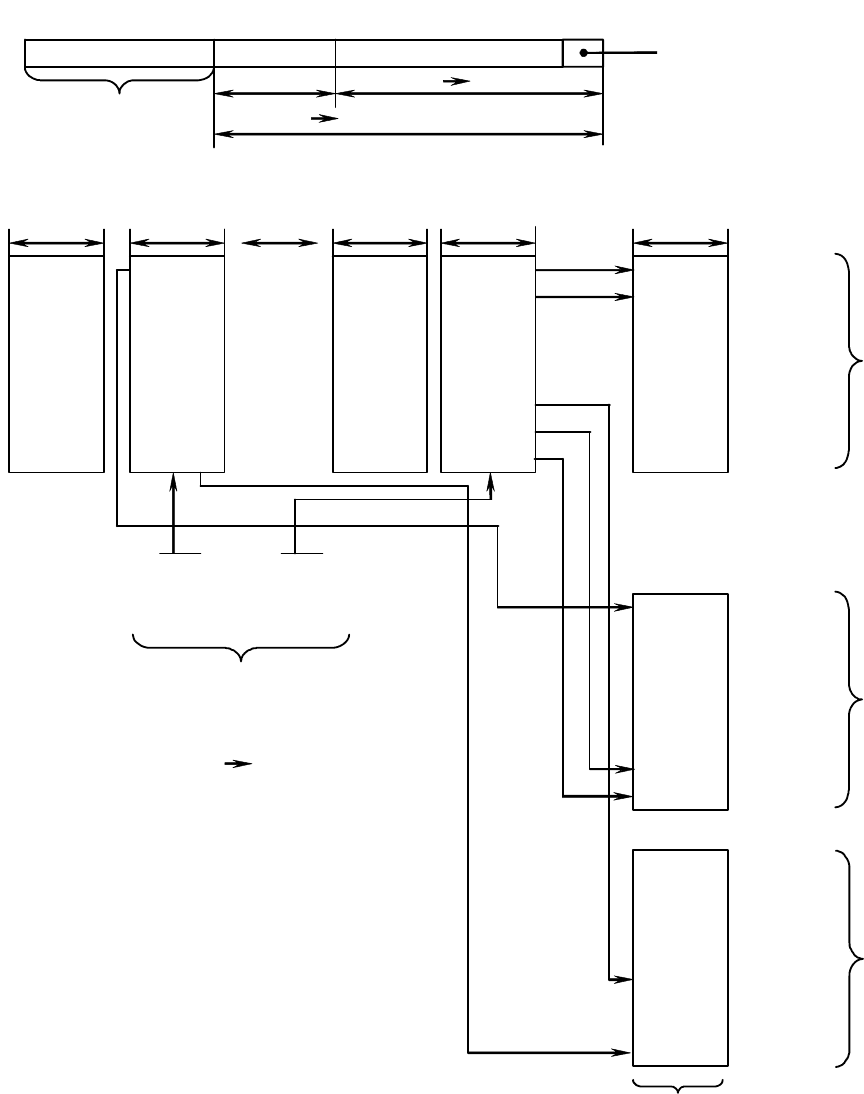

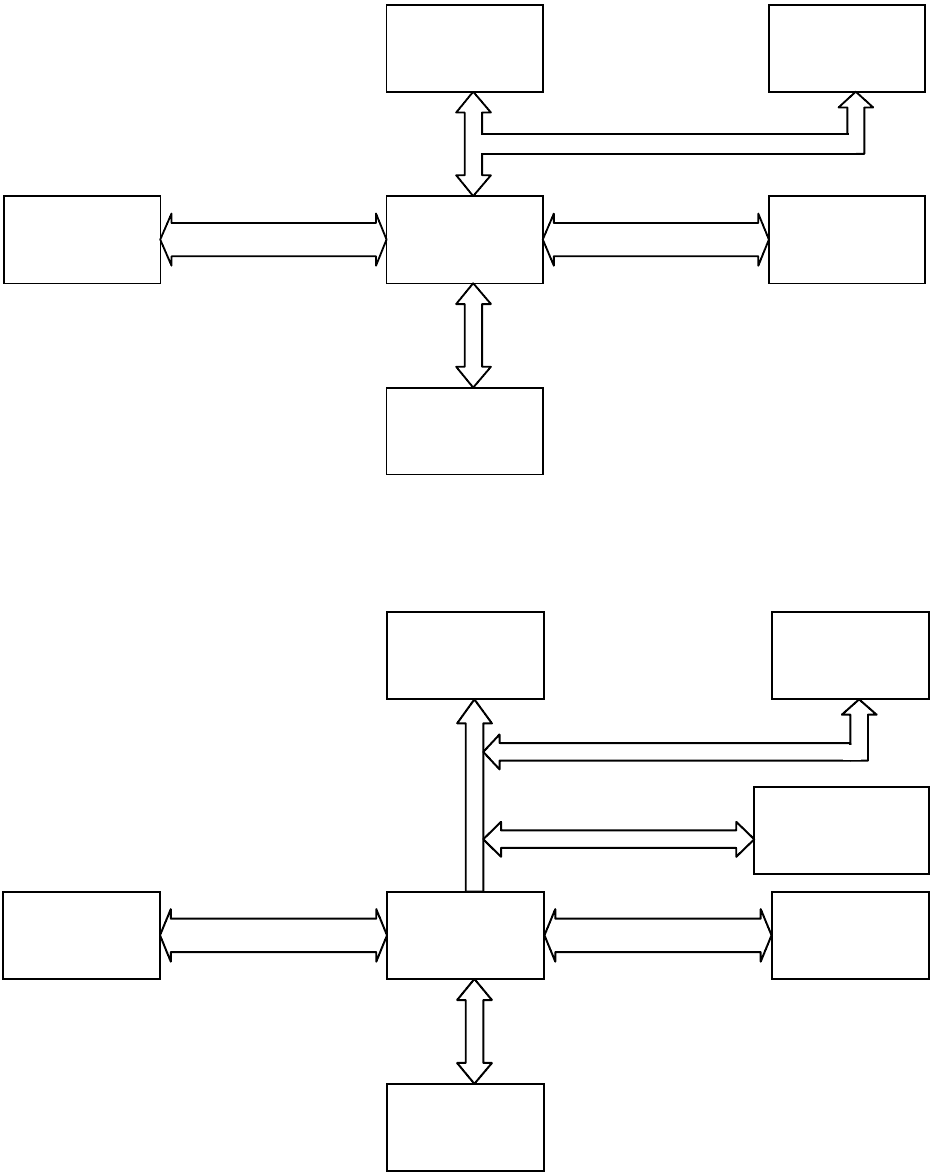

Рис. 9.10. Организация двухвходового множественного ассоциативного кэш

0 ….. 0

31 24

П

р

изнак Индекс

15 223

В случае ОП

16 Мбайт

1

0

9 бит

Номер байта

15 бит 32 К кэш

24 бита 16 Мбайт

д

инамич. ОП

4 байта

Данные

В

Ж

А

Б

Е

Г

Д

4 байта

Данные

64 К кэш памяти

Оба блока кэш имеют

одинаковую адресацию

000…1FF 512 стр.

А

Б

4 байта

Данные

В

Г

Д

- - - - - -

- - - - - -

- - - - - -

- - - - - -

Е

Ж

7FFC

7FF8

- - - -

- - - -

- - - -

000C

0008

0004

0000

7FFC

7FF8

- - - -

- - - -

- - - -

000C

0008

0004

0000

1FF

001

7FFC

7FF8

- - - -

- - - -

- - - -

000C

0008

0004

0000

000

16 Мбайт

динамич. ОП

Буквами русского

алфавита А, Б, В

и т.д. обозначены

4-байтовые блоки,

хранящиеся в ОП

и кэш

001

000

9 бит

Признак

7FFC

7FF8

- - - -

- - - -

- - - -

000C

0008

0004

0000

13 бит

Индекс

32К

стат.

ОП

32К

стат.

ОП

Индекс Признак

9 бит

Признак

1FF

1FF

000

001

001

14

====================================================================

71

====================================================================

А

В

С

D

E E

C

B

или

E

C

B

Начальное

распреде-

ление ОП

Вводимая

программа

из ВП

Конечное распре-

д

еление ОП

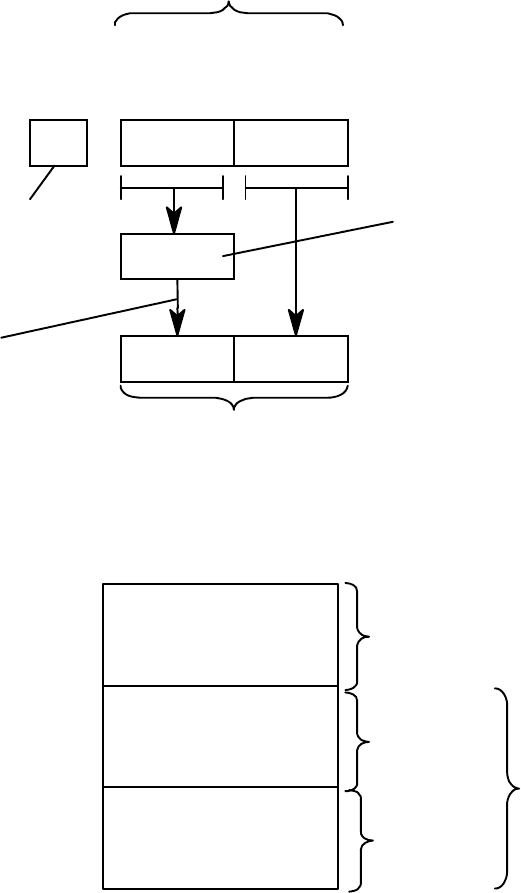

Рис. 9.11. Пример распределения памяти

====================================================================

Виртуальная

память n-й

программы

Рис. 9.12. Упрощенная схема страничной организации памяти

ОП

ОП

ОП

ВП

ВП

ОП

ОП

ОП

5

0

7

4

10

8

9

1

Тип

памяти

Номер

физической

страницы

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

8

9

10

0

1

2

3

4

5

6

7

8

9

10

ОП ВП

Физическая память

Страничная

таблица

====================================================================

72

====================================================================

n

LP

Рг номера

программы

N(n, P)

N(n, P)

L

Страничная таблица

n-й программы

Физический адрес

Номер физической

страницы из стра-

ничной таблицы

Номер вир-

туальной

страницы

Номер

байта

Виртуальный адрес

Рис. 9.13. Формирование физического адреса

====================================================================

Системное ПЗУ

Видеоадаптер

Сетевой адаптер

Область

прикладных

программ

DOS, драйверы,

резидентные

программы

1024 К

640 К

70 К

0 К

70

Кбайт

570

Кбайт

384

Кбайт

ОП

Рис. 9.14. Упрощенная структура прямоадресуемой памяти PC/XT

====================================================================

73

====================================================================

Системное ПЗУ

Память видео-

адаптера

0К

640К

1024К

ОП

Кадр EMS-

памяти

(

64 Кбайт

)

16 Кбайт

Расширение

д

о 32 Мбайт

EMS-память

Рис. 9.15 Отображение адресного пространства на страницах EMS-памяти

Пространство

адресов прямо-

адресуемой

памяти

16 Кбайт

16 Кбайт

16 Кбайт

====================================================================

x

<

α

Память

α + N

РгА

α

Схема

сравнения

N ячеек

α

Разрешенная

область памяти

x >

α +N

Прерывание

РгВ

РгН

x ≥ α

x

≤

α + N

Разрешение

обращения

Схема

сравнения

РгН - регистр нижней границы;

РгВ - регистр верхней границы;

α

- адрес нижней границы допустимой зоны обращений;

N - количество ячеек разрешенной зоны памяти

Рис. 9.16. Защита памяти с помощью граничных регистров

Прерывание

====================================================================

74

====================================================================

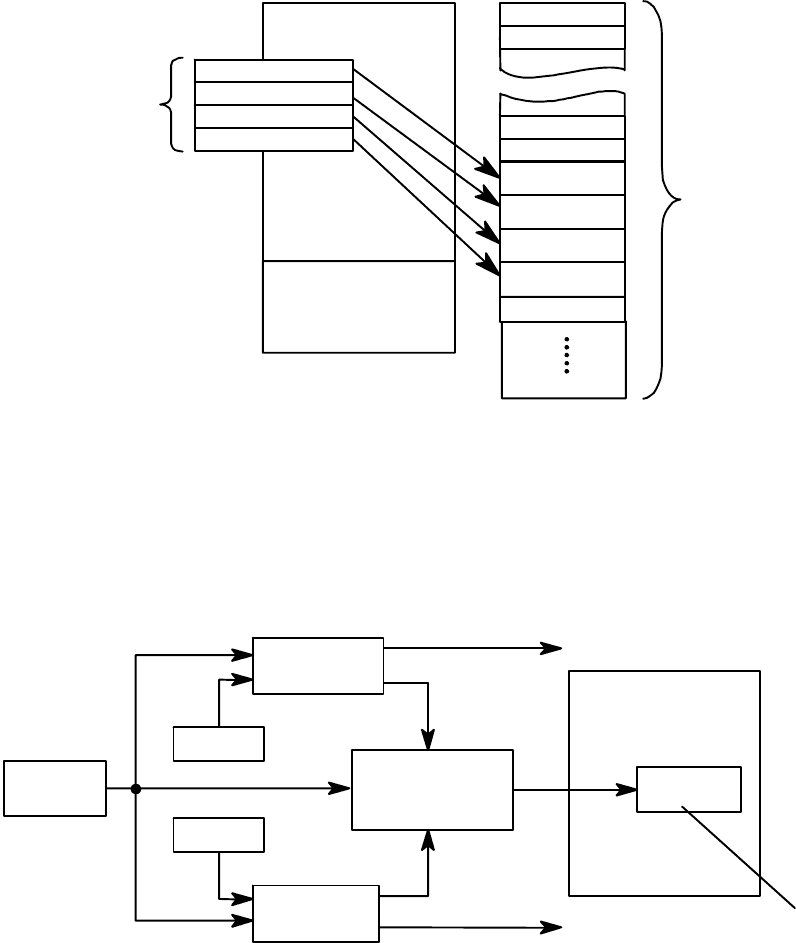

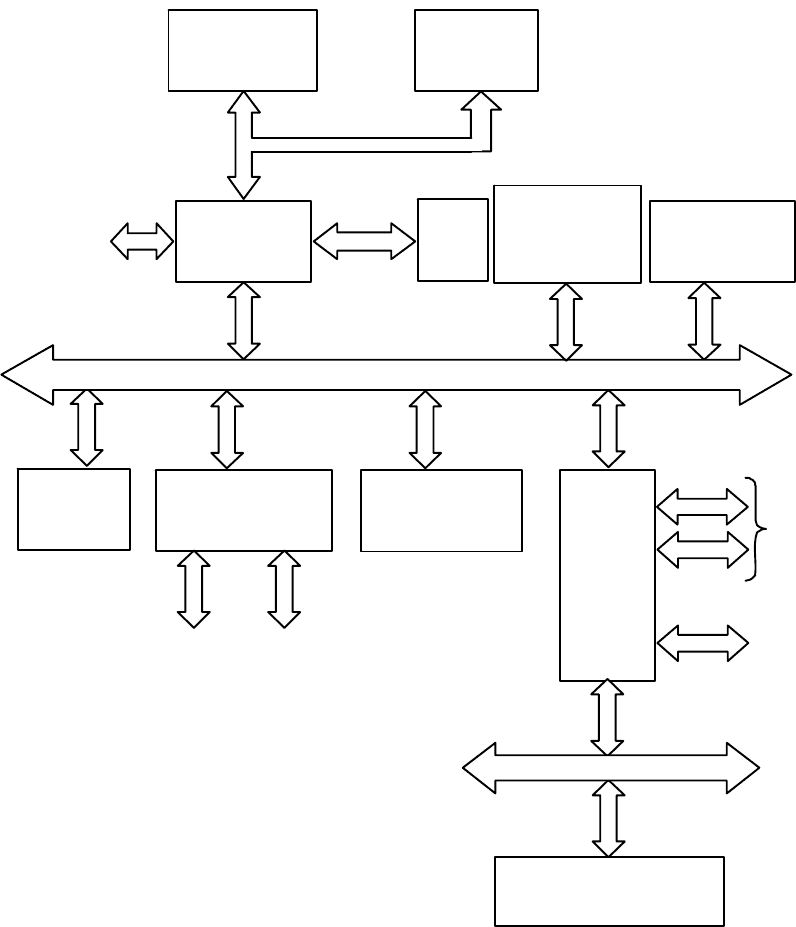

Рис. 9.17. Система защиты памяти ЭВМ на процессоре I80386

Задача А

Задача В

Прикладные програм-

мы (Р=3)

Межзадачное распространение

ошибок, предотвращаемое

проверкой атрибутов доступа

Прикладной сервис (Р=2)

Системный сервис (Р=1)

Ядро (Р=0)

Межуровневое

распространение

ошибок, предот-

вращаемое систе-

мой приоритетов

Задача С

====================================================================

j

1

j

2

…

j

m-1

j

m

j

m+1

j

r-1

j

r

…

…

…

…

Память

верхнего

уровня

Память нижнего

уровня

q

S

∉

t

t

Рис. 9.18. Алгоритм замещения "карабкающаяся страница"

====================================================================

75

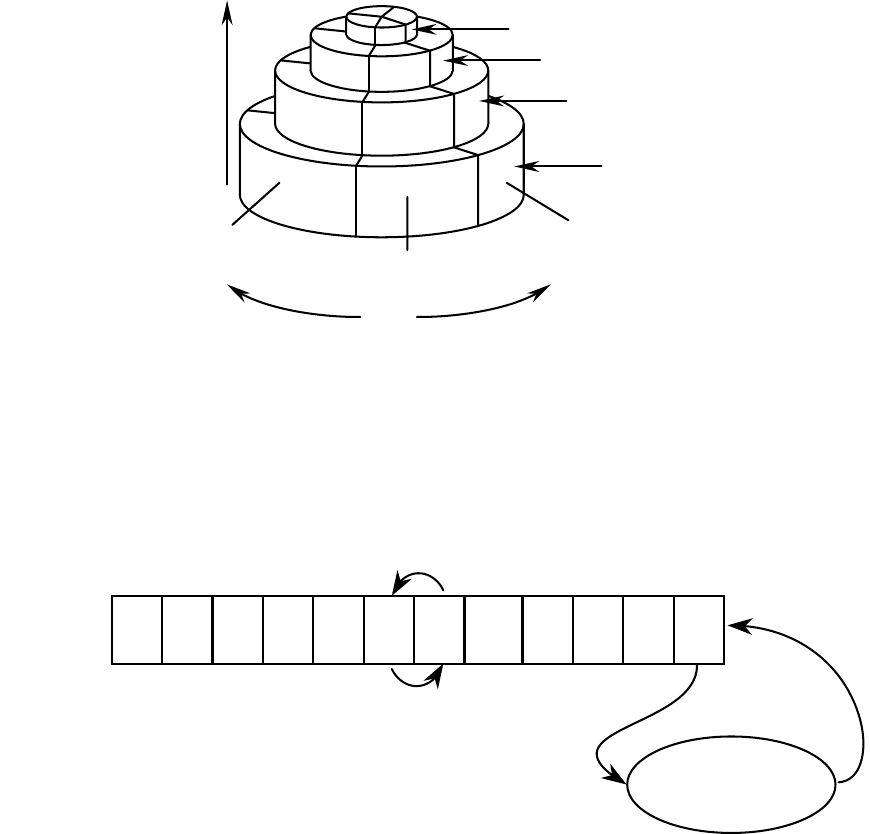

10. Эволюция шинной архитектуры IBM PC

====================================================================

Шина

процессора

Шина

памяти

Микросхемы

контроллера

шины

Процессор

Основная

память

Внешний

кэш

Встроенные

устройства

ВВ

ВВ через

слоты

Шина расширения Шина расширения

Рис. 10.1. Упрощенная структура шин первых IBM PC

====================================================================

Шина

памяти

Чипсет

Процессор

Основная

память

Внешний

кэш

Встроенные

устройства

ВВ

ВВ через

слоты

Шина расширения Шина расширения

ВВ через

слоты или

встроенный ВВ

Шина

процессора

Рис. 10.2. Упрощенная схема подключения локальной шины

====================================================================

76

====================================================================

Интерфейс

IEEE 1394

Процессор

Внешний

кэш

Главный

мост

Мост

PIIX

Шина

процессора

Интерфейс

AGP

Сетевой

адаптер

Адаптеры

устройств PCI

Интерфейс

SCSI

Графический

адаптер

Интерфейсы

IDE

Интерфейс

USB

Шина

PCI

"Медленные"

устройства ВВ

Шина ISA

(EISA), MCA

Шина

памяти

ОП

Обработка

изобра-

жения

Рис 10.3. Упрощенная структура шин IBM PC

Звуковой

адапте

р

====================================================================

77

11. Принципы организации систем прямого доступа к памяти

====================================================================

Процес-

сор

СУМ

Арбитр

Контроллер ПДП

ИЗПД

1

Запро-

счик

ОЗПД

РПД

ИЗПД

k

Запро-

счик

ЛЗПД

1

ЛЗПД

k

ЛЗПД

i

ЗПД

k

А

Р

Б

И

Т

Р

ИЗПД

1

Запро-

счик

ЛЗПД

1

ИЗПД

k

Запро-

счик

ЛЗПД

k

ЛЗПД

i

ЛПЗ

i

СУМ

ЛПЗ

1

ЛРПД

1

СУМ

ЛПЗ

k

ЛРПД

k

ЛРПД

i

РПД

ПЗ

ЗПД

а

б

ИЗПД – источник запросов прямого доступа; РПД – сигнал разрешения прямого доступа;

СУМ – средства управления магистралью; ПЗ – сигнал подтверждения захвата магистрали;

Л

РПД – линия разрешения прямого доступа; ЗПД – сигнал запроса прямого доступа;

Л

ПЗ – линия подтверждения захвата магистрали; ШАр – шина арбитража;

ОЗПД – общий сигнал запроса прямого доступа; ЛЗПД – линия запросов прямого доступа

Рис. 11.1. Радиальная структура системы: а – Slave DMA, б – Bus Master DMA

ШАр

Системная магистраль

Системная магистраль

====================================================================

78

====================================================================

А

Р

Б

И

Т

Р

СУМ

ИЗПД

1

Запро-

счик

СУМ

ИЗПД

2

Запро-

счик

СУМ

ИЗПД

3

Запро-

счик

СУМ

ИЗПД

4

Запро-

счик

Slave

Slave

ШАр

1

ШАр

2

Рис. 11.2. Обобщенная цепочечная структура системы Bus Master DMA

Системная магистраль

====================================================================

79

====================================================================

Слот ”0”

Слот ”1” Слот ”i”

Слот ”k”

ШАр

2

ШАр

1

А

Р

Б

И

Т

Р

СУМ

ИЗПД

n,1

Запросчик

СУМ

ИЗПД

n,i

Запросчик

СУМ

ИЗПД

n,k

Запросчик

ЛРПД

n

РПД

n

ШАр

n

ЛБПД

n

ЛПЗ

n

ЛЗПД

n

БПД

n

ПЗ

n,i

ЗПД

n,i

ИЗПД – источник запросов прямого доступа;

СУМ – средства управления магистралью;

ЛЗПД – линия запросов прямого доступа;

ЛРПД – линия разрешения прямого доступа;

ЛПЗ – линия подтверждения захвата магистрали;

ЛБПД – линия блокировки прямого доступа;

ШАр

n

– одна из шин арбитража;

ЗПД – сигнал запроса прямого доступа;

РПД – сигнал разрешения прямого доступа;

ПЗ – сигнал подтверждения захвата магистрали;

БПД – сигнал блокировки прямого доступа

Рис. 11.3. Структура шины арбитража "n" системы bus master DMA цепочечного типа

Системная магистраль

====================================================================