George W. Stimson introduction to Airborne Radar (Se)

Подождите немного. Документ загружается.

CHAPTER 42 Low Probability of Intercept (LPI)

531

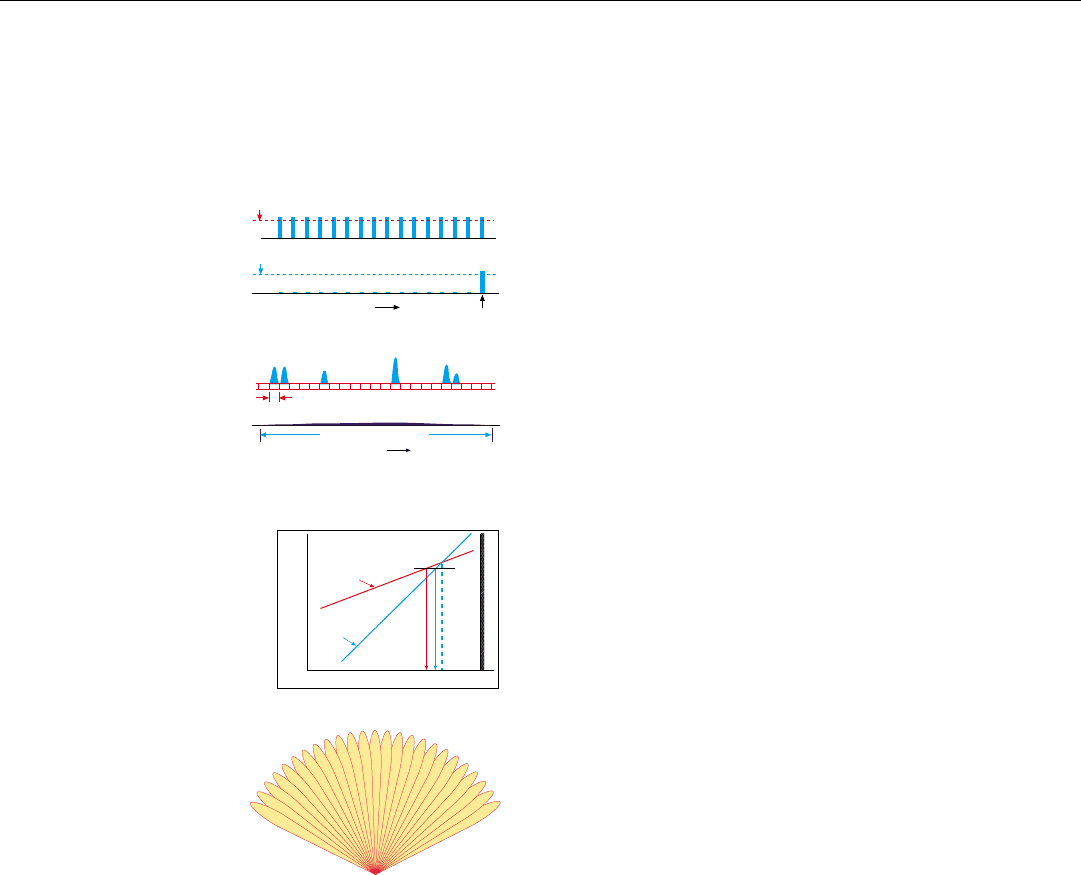

6. Increase in dwell time achievable by radiating multiple beams on different frequencies. For the same detection sensitivity, as the number, N,

of beams is increased, peak power can be reduced by a factor of 1/N.

7. Enough beams might be provided to completely fill the scan

volume. Then, no scanning would be needed, and the coher-

ent integration time would equal the frame time.

with a single beam, the maximum allowable dwell time

would equal T/V (Fig. 6a).

On the other hand, if this same volume (V) were subdi-

vided into N sectors and every sector were simultaneously

searched by a different beam using a different radio fre-

quency (Fig. 6b), the dwell time in each beam direction

could be increased by a factor of N. Then, if the coherent

integration time were increased to match the dwell time—

now equal to NT/V—the peak power emitted in any one

beam direction could be reduced by the factor 1/N.

In the extreme, provided adequate processor throughput

is available, enough beams might be emitted to completely

fill the scan volume (Fig. 7). No scanning would then be

needed. Consequently, the coherent integration time could

be made equal the total frame time, T.

Multiple beams may also be employed to advantage in

other ways. They may, for example, be used to selectively

search different portions of the total scan volume. Or, each

beam may be used to scan the entire volume on a different

frequency, thereby increasing detection sensitivity through

frequency diversity rather than through increased integra-

tion time.

Random Waveform Parameters. For all practical pur-

poses, in a dense signal environment a signal has not been

usefully intercepted unless it has been successfully de-inter-

leaved (sorted) and identified (Table 2). Consequently,

besides reducing the probability that the radar’s signals will

be detected by an interceptor, the radar designer has oppor-

tunities for confounding the de-interleaving and identifica-

tion processes, as well.

V

V = Scan Volume, in multiples of antenna’s 3-dB beamwidth

T = Frame Time

Dwell Time =

T

V

Sector 1

Sector 2

Sector 3

Sector 4

N = Number of sectors volume V is divided into

T = Frame Time

Dwell Time = N

T

V

a. Single

Beam

b. Multiple

Beams

3-dB beamwidth

TABLE 2 Basic Intercept Receiver Functions

Detection

De-interleaving

(Sorting)

Identification

Detect single pulses (peak power), with

little or no integration.

Separate pulses of individual emitters, in

a dense signal environment.

Identify emitters by type; possibly even

identify specific emitters.

These are binary phase codes which appear to

be entirely random in virtually every respect—

except for being repeatable. Their advantages:

• A great many different codes can be generated

easily and conveniently

• Codes can be made almost any length, hence

provide extremely large compression ratios.

The codes are commonly generated in a shift

register having two or more feedback paths.

Filled initially with 1s or 1s and 0s, the register

produces a code of 1s and 0s of length

where N is the number of digits output before the

code repeats, and n is the number of digits the

register holds.

An 11-digit register with the 9th and 11th digits

fed back to the input, for example, produces a code

2,047 digits long. By changing the feedback

connections, 176 different codes of that length can

be produced .

The 0s and 1s in the code specify the relative

phases—0° and 180°—for successive segments of

the radar's transmitted pulse.

By shifting the register at intervals equal to the

desired length of the segments, successive output

digits can directly control the phase modulation of

the radar signal.

When the received pulse is decoded, the seg-

ments are superimposed, producing a pulse

roughly N times the amplitude of the uncompressed

pulse and only a little wider than the segments.

The code generated by the 11-digit register of this

example would thus yield a pulse compression ratio

of roughly 2,000 to 1.

PSEUDO-RANDOM

PULSE COMPRESSION CODES

N = 2

n

– 1

Code: 1 0 1 0 0 1 . . .

180° 180° 180°0° 0° 0°

Segments of a phase-coded pulse

Output

1 0 1 0 0 1 . . .

1 2 3 n - 3 n - 2 n - 1 n

Phase

Modulator

From Exciter To Transmitter

RegisterShift Pulses

With No

Carry

+

8. By cooperatively shifting radar transmission randomly

between them, two or more aircraft can even vary the angle

of arrival of their emissions.

PART IX Advanced Concepts

532

Among the waveform parameters typically used for both

de-interleaving and classification are:

• Angle of arrival

• Radio Frequency

• PRF

Among those parameters typically used for classification

alone are:

• Pulse width

• Scan rate

• Intrapulse modulation

• Interpulse modulation

• Beam width

• Signal polarization

Except for angle of arrival, all of the above-listed para-

meters can be varied randomly from one coherent integra-

tion period to the next.

Variations can be achieved without reducing detection

sensitivity by taking advantage of the waveform agility

available in modern airborne radars. Moreover, with two or

more aircraft operating cooperatively—i.e., alternately pro-

viding target illumination for each other (Fig. 8)—even

angle of arrival can be varied.

Randomizing any of the parameters can confuse the clas-

sification process. That is particularly true for those inter-

cept systems which classify signals by comparing their

parameters with parameters stored in threat tables.

Mimicking Enemy Waveforms. Mimicking may also con-

fuse signal classification. To be able to mimic an enemy’s

waveforms, though, the radar must not only have consider-

able waveform agility, but be able to operate over the full

range of radio frequencies the enemy employs.

Cost of LPI

LPI techniques are not free; each of the LPI-enhancing

features adds to the radar’s cost. Most increase the costs of

both software and hardware.

But by far the greatest cost of LPI is in digital processing

throughput. As instantaneous bandwidth is increased, for

instance, the required throughput goes up proportionately

because of the increased number of range bins whose con-

tents must be processed.

For, to the extent that bandwidth is increased through

pulse compression coding, the wider the bandwidth, the

narrower the compressed pulses will be, hence the more

range bins required to cover the same range interval.

Throughput similarly goes up with the number of simulta-

neous beams radiated.

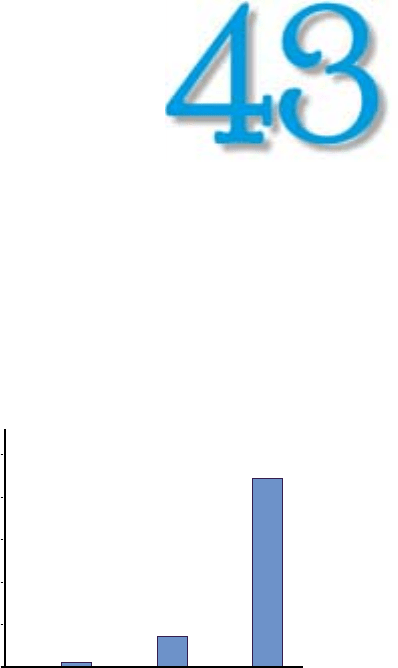

To support a wide instantaneous bandwidth and a few

simultaneous beams, the required throughput is staggering

(Fig. 9). In fact, not until the 1990s were these features

even deemed practical. With the dramatic advances being

made in digital processor technology, however, the costs of

these features are rapidly decreasing.

Be that as it may, in any discussion of costs one impor-

tant fact must be borne in mind. With the exception of

power management, virtually all of the LPI features maxi-

mize detection sensitivity greatly moderating the cost of LPI

in performance.

Moreover, in those situations where the advantages of

maximum detection range and situation awareness out-

weigh the advantages of LPI, the operator always has the

option of overriding power management, operating the

radar continuously, and searching the antenna’s entire field

of regard.

Possible Future Trends in LPI Design

Looking to the long-term future, one thing is certain:

competition between radar designer and intercept receiver

designer will never be static. For every improvement in LPI,

improvements in intercept receiver design can be expected.

LPI designers will continue to exploit coherent processing,

which the intercept receiver cannot duplicate. And design-

ers of intercept receivers will continue to exploit the R

2

advantage of one-way versus two-way propagation.

Probably, the most spectacular gains in both LPI and

intercept receiver design will occur in signal processing,

which is the subject of the next chapter.

Summary

There are four generic types of intercept receivers: radar

warning receivers (RWR); intercept receivers of ECM sys-

tems; ground-based passive-detection systems (DOA and

EL); and ARMs. RWRs typically detect only mainlobe radia-

tion; the others, sidelobe radiation.

CHAPTER 42 Low Probability of Intercept (LPI)

533

9. Ranges of throughputs in billions of computer operations per

second (BOPS) required for long integration time and spread-

spectrum/multifrequency operation. High PRF is shown for

comparison.

0

30

20

10

High

PRF

Long

Integration

Time

Spread

Spectrum

Multifreq.

B

O

P

S

PART IX Advanced Concepts

534

Operational strategies for LPI include limiting radar “on”

time, using collateral intelligence and reconnaissance infor-

mation wherever possible, relying heavily on onboard pas-

sive sensors, and searching only narrow sectors in which

they indicate the target to be.

LPI design strategies capitalize primarily on the intercept

receiver:

• Having to detect individual pulses, so that it can de-

interleave them and identify their sources

• Having limited channel widths, so that the receiver can

separate closely spaced signals.

Consequently, LPI can be enhanced by trading both long

coherent integration time and wide instantaneous band-

width for reduced peak power.

High antenna gain, reduced sidelobe levels, high duty

factor, and increased receiver sensitivity can likewise be

traded for reduced peak power.

LPI can be further enhanced by several special features.

First among these is power management—keeping the peak

emitted power just below the level at which it can be use-

fully detected by an intercept receiver in an approaching

aircraft, yet just above the level at which the radar can

detect the aircraft.

Added to this feature are (a) using extremely large

amounts of pulse compression to spread the radar’s signals

over an exceptionally wide instantaneous bandwidth; (b)

simultaneously transmitting multiple beams on different

frequencies to reduce the constraint imposed on integration

time by limits on scan-frame-time; (c) randomly changing

waveform characteristics to confound the intercept receiv-

er’s signal de-interleaving and identification process; and

(d) mimicking enemy waveforms.

The principal cost of LPI is greatly increased signal pro-

cessing throughput.

Radar

Intercept Receiver

Detection

Threshold

Detection

Threshold

Integrated

Returns

Time

Radar

Intercept Receiver

Channel Width

Instantaneous Bandwidth

Frequency

Peak

Trans-

mitted

Power,

P

Detection of Radar

by Intercept

Receiver

Detection of

Target by

Radar

Horizon

Target Range, R

R

d

max

P

det

P

int

535

Advanced Processor

Architecture

H

aving read of the many advanced radar tech-

niques in the offing, processor architecture may

seem of little import. But the fact is that most

of the advanced capabilities of airborne radars

to date have only been made practical by substantial

increases in digital processing throughput (Fig. 1).

In the 1970s, multimode operation was made possible in

fighters by replacing the hardwired FFT processor with a

programmable signal processor (PSP) having a throughput of

around 130 MOPS.

1

In the 1980s, the addition of real-time

SAR was made possible by quadrupling processing

throughput. In the 1990s, the active ESA and other

advanced capabilities of the F-22 were made possible by

again quadrupling throughput.

Vastly higher throughputs will be needed to make practi-

cal some of the advanced radar capabilities currently envi-

sioned. Spread spectrum, for example, is highly desirable

for both ECCM and LPI. Yet, even a 500 MHz instanta-

neous bandwidth will require 500,000 MOPS.

In this chapter, we’ll examine the key architectural fea-

tures of the late 1990s-era processors: parallel processing,

high throughput density, efficient modular design, fault tol-

erance, and integrated processing. We’ll then take stock of a

few technology advances which promise substantial

throughput increases in the future.

Parallel Processing

To meet radar throughput requirements, two levels of

parallel processing are typically employed: at the signal-

processing element level, pipeline processing; at the process-

ing system level, distributed processing.

1. MOPS = Million operations

per second.

Multimode

Radar

F-22

Radar’s

Capabilities

1970s 1990s1980s

Multimode

Radar

Including

Real-Time

SAR

5,000

M

O

P

S

1,000

0

3,000

1. Growth of radar capabilities made possible by increases in

processor throughput.

PART IX Advanced Concepts

536

Pipeline Processing. This technique was devised in the

early days of digital signal processing to enable a program-

mable machine to perform the vast number of arithmetic

operations required for doppler filtering fast enough to

process radar returns in real time.

2

The technique is implemented with a multistage register

plus associated arithmetic elements (see panel, left). Keyed

by successive clock pulses, each number to be processed—

together with the multistep instruction for processing it—is

sequentially loaded into the register’s first stage.

The numbers are shifted down, a stage at a time, by suc-

cessive clock pulses. In the first stage, the first step of the

instruction is carried out. In the second stage, the second

step; and so on.

The number of stages is the same as the number of indi-

vidual processing operations necessary to execute the

instruction for which the pipeline is designed. That number

can vary from 2, for a very simple algorithm, to 8 or 10 for

an FFT butterfly.

3

Once the pipeline is filled, one butterfly

(or equivalent) may be computed in every clock time.

The increased throughput thus realized may be multi-

plied many times by distributing processing tasks among

multiple processing elements (PEs) operating in parallel.

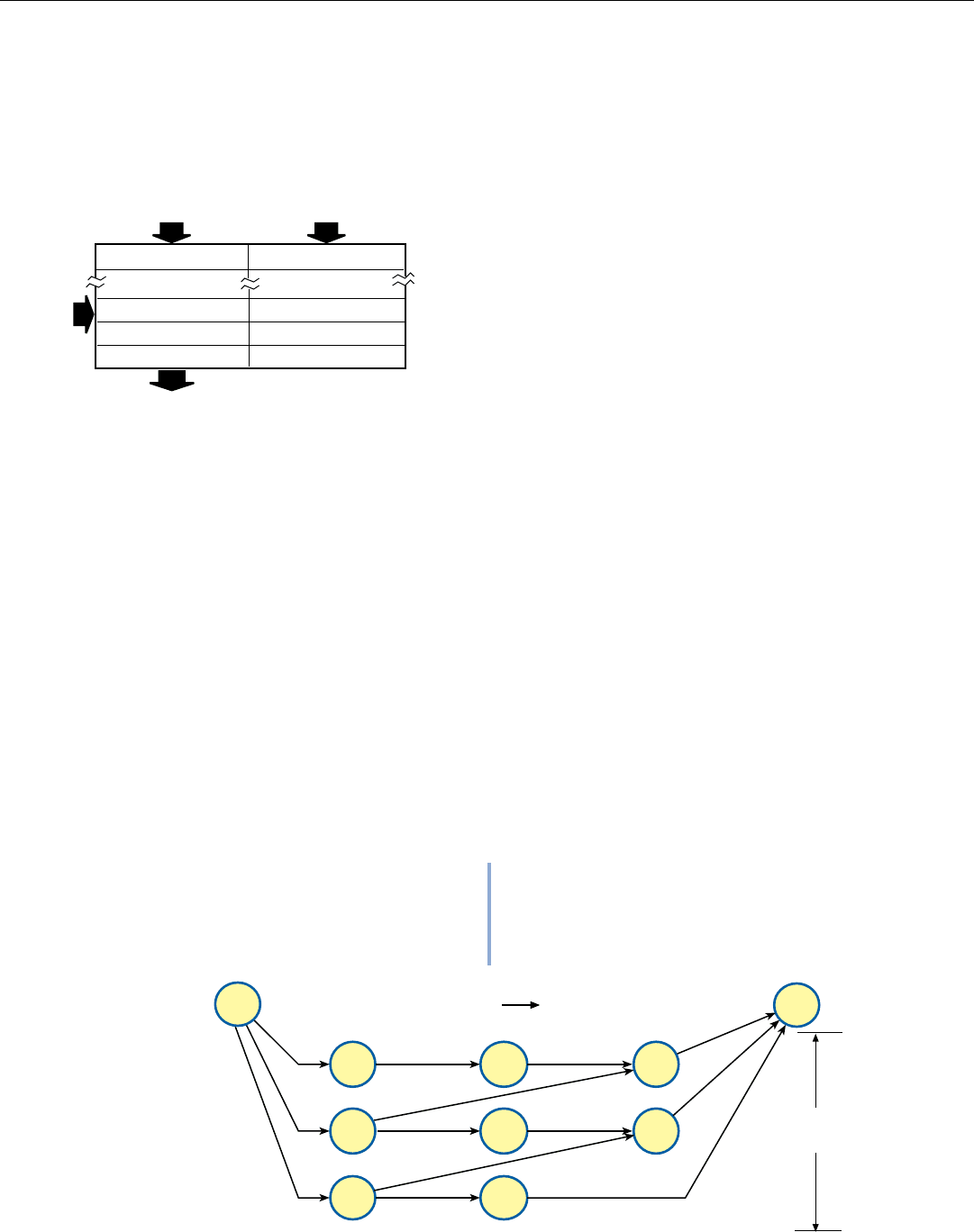

Distributed Processing. Both throughput and intercon-

nect bandwidth increase directly with the number of PEs.

Consequently, as throughput requirements have increased,

the number of PEs used in airborne systems has been

increased from three or four (see panel below) to a hundred

or more, and no end is in sight.

SIMPLE DISTRIBUTED PROCESSING EXAMPLE

Distribution of processing tasks for parallel

execution of a range-gated tracking mode by a

processor employing one general purpose pro-

cessing element—Array Controller—and three

identical Signal Processing Elements.

Arrows indicate flow of data, e.g., Job 4 (as-

signed to Element 1) and Job 2 (assigned to

Element 2) must be completed before Job 7 can

be performed. Jobs 3 and 5 must be completed

before Job 8 can be performed.

Array

Controller

Processing

Element 1

Processing

Element 2

Processing

Element 3

Job

1

Job

2

Job

3

Job

4

Job

5

Job

6

Job

7

Job

8

Job

9

Parallel

Execution

Time

Job

0

2. The technique is applicable to

performing any series of addi-

tions, subtractions and multi-

plications of real, complex, or

floating-point numbers.

3. The computations called for in

the butterfly algorithm are

detailed on pages 273 and 277.

Each of the complex numbers to be processed,

together with the multistep instruction for processing

it, is sequentially loaded into a multistage register

and shifted down, one stage at a time, by succes-

sive clock pulses. In each stage one step of the

instruction is executed.

Once the pipeline is full, one butterfly or other algo-

rithm is completed in every clock time.

Assuming a clock rate of 25 MHz and a 10

stage pipeline, such as might be provided for the

FFT butterfly, the throughput would be:

10 operations x 25 million/sec. = 250 MOPS

PIPELINE PROCESSING

Result

Number (n3)

Number (n2)

Number (n1)

Instruction (n3)

Instruction (n2)

Instruction (n1)

Clock

Complex Numbers Multi-Step Instructions

Number (N) Instruction (N)

IN IN

OUT

In one of many possible implementations (Fig. 2), com-

munication between PEs is provided via two-dimensional

mesh connections.

In another, the PEs are interconnected via nonblocking

crossbar switches (Fig. 3). Large distributed systems of this

type have been used to perform the billions of floating-

point computations required in ultra-fine-resolution SAR

applications.

4

CHAPTER 43 Advanced Processor Architecture

537

PE PE PE

PE PE PE

PE PE PE

CROSSBAR SWITCH

PE

C

R

O

S

S

B

A

R

PE

PE

PE

PE

PE

PE

PE

PE

C

R

O

S

S

B

A

R

PE

PE

PE

PE

PE

PE

PE

2. One of many practical distribution schemes. Processing ele-

ments (PEs) are interconnected in a two-dimensional mesh.

Pattern can be expanded in either dimension to accommo-

date more PEs.

3. Another distribution scheme. Same PEs as shown in Fig. 2

are clustered around crossbar switches. Number of PEs can

be increased by adding more clusters.

Since the space available for avionic equipment in a

high-performance military aircraft is limited, the maximum

realizable throughput depends largely on how high the

processor’s throughput density is.

Achieving High-Throughput Density

Throughput density is a processor’s maximum through-

put divided by the volume of the processing hardware.

High density is achieved primarily by implementing the

processor with very large-scale integrated circuits (VLSIs).

Types of VLSIs Used. The VLSIs used are generally of

three standard types:

• RISC

5

microprocessor chips

• Random-access memory (RAM) chips

• Programmable logic chips

plus custom designed signal processing and interface chips,

called gate-arrays.

Gate Array Chips. Early in the era of VLSIs, the gate

array was conceived as an economical means of (a) easing

the limitation that defects impose on the maximum practi-

cal size of an integrated circuit and (b) producing affordable

complex signal processing circuits for which there may be

only a limited market. The basic building blocks of these

circuits are logic gates.

4. They have also been used in

electro-optical applications.

5. RISC stands for reduced

instruction set computer.

PART IX Advanced Concepts

538

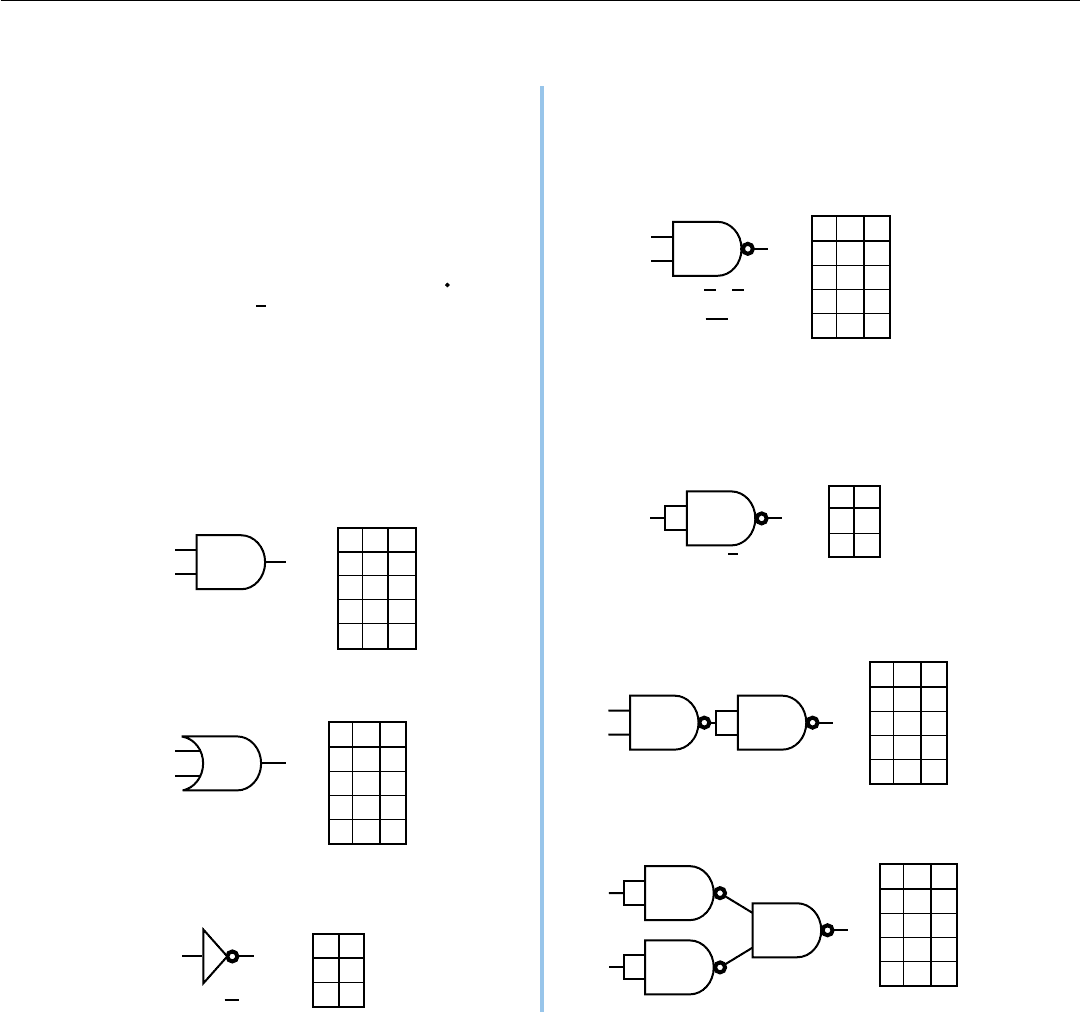

As illustrated in the panel above, logic gates are of many

different types. All possible types, however, may be pro-

duced with various combinations of just one: the “NAND”

(not and) gate. Therefore, if an array of a great many NAND

gates is produced on a single semiconductor chip, by

appropriately interconnecting the usable gates when the

interconnection layers are added, very large custom circuits

can be economically produced.

Moreover, by implementing the gates with CMOS

6

tech-

nology (see panel facing page), relatively simple semicon-

ductor processing can be employed. This leads to a low

percentage of defects, hence high yields, making practical

6. CMOS is a combination of

MOSFETs (metal oxide silicon

field effect transistors) having

complementary characteristics.

A gate is a digital circuit that performs a logic

function. It may have one or more inputs, but only

one output. Inputs and outputs are voltages of op-

posite polarities: “

+ ” representing binary 1, and

“ – ” representing binary 0.

Gates may be represented either by graphic

symbols or by simple equations whose terms have

values of 0 or 1 and whose connectives have spe-

cial meanings., e.g., a “

+ ” means “ or ”; a “

” means

“and”; and a bar “

” over a term means “not”.

A gate's functions are defined by a truth table.

It indicates what the gate’s outputs will be for all

possible combinations of inputs.

The most commonly used gates are the “and”,

“or”, and “not” (inverter) gates.

An AND gate produces an output of 1 only if

both inputs, A and B, are 1s. Otherwise, it pro-

duces an output of 0.

An OR gate, on the other hand, produces an

output of 1 if A, or B, or both A and B are 1s.

A NOT, (inverter) gate produces an output of 0

if its single input is 1 and an output of 1 if its single

input is 0.

There are many other gates. But all can be

produced by combinations of just one: the NAND

(not and) gate, commonly used in CMOS circuitry.

A NAND gate produces an output of 1 only if

both inputs are not 1. Otherwise its output is 0.

Consequently, if both inputs are tied together,

an input of 0 produces an output of 1, and an input

of 1 produces an output of 0. The gate acts as a

NOT gate, or inverter.

If the output of a NAND gate is connected to

both inputs of a NAND gate, therefore, the output

is inverted. The two gates form an OR gate.

If the inputs to a NAND gate are similarly in-

verted, the three gates form an AND gate.

THE GATE: Signal Processor Building Block

A

B

C = A + B

OR

C = A

NOT

(Inverter)

C = A

.

B

C = AB

A

B

C

A

B

C

C = A B

AND

ABC

000

100

010

111

C = A

.

B

C = AB

C = A + B

AC

C = A

A

B

C

A

B

C

ABC

000

101

011

111

ABC

000

100

010

111

ABC

000

101

011

111

ABC

001

100

010

110

AC

01

10

AC

01

10

NAND

A

C

NAND

C

NANDNAND

NAND

NAND

NAND

CHAPTER 43 Advanced Processor Architecture

539

CMOS is a combination of MOSFETs (Metal

Oxide Silicon Field Effect Transistors) having

complementary characteristics. Because MOS-

FETs can be produced with relatively simple

semiconductor processing, they make practical

producing exceedingly large numbers of gates on

a single semiconductor chip.

This panel explains what MOSFETs are, what

their complementary characteristics are, and how

they may be interconnected to form a NAND gate,

with which all other gates may be produced.

A MOSFET is produced by heavily doping a

lightly doped region on the surface of a silicon

crystal substrate, to produce a channel of high

conductivity. Centered over this channel is a tiny

metal plate— called a “gate”— insulated from the

crystal by an extremely thin layer of oxide.

Terminals are provided at both ends of the chan-

nel; a terminal for a control voltage, on the gate.

Two complementary doping schemes are

used. In one, N-type doping—which produces

free negative charge carriers (electrons)—is used

for the channel and P-type doping—which pro-

duces free positive charge carriers (holes)—is

used for the substrate.

At the channel's lower edge, holes and elec-

trons combine, depleting the number of free car-

riers there, and narrowing the channel .

If a negative voltage corresponding to a

binary digit is applied to the gate, it attracts more

holes from the substrate. They combine with more

free electrons, narrowing the channel sufficiently

to pinch it off, so no current can pass through.

If a positive voltage corresponding to a binary

digit is applied to the gate, it repels the holes in the

substrate, widening the channel and maximizing

its conductivity.

The gate thus acts as a switch, which is closed

by a positive control voltage and opened by a neg-

ative one.

The other doping is P for the channel and N

for the substrate.

With it, the control voltage has the opposite effect.

A positive voltage opens the switch; a negative,

closes it.

A NAND gate may be constructed by intercon-

necting 2 N-channel and 2 P-channel MOSFETs,

as shown below. When inputs A and B are positive,

both P-channel switches open, disconnecting the

positive supply voltage.

And the two N-channel switches close, connect-

ing the negative supply voltage to the output, C.

When A or B is negative, at least one of the

two P-channel switches closes, connecting the

positive supply voltage to C.

CMOS: Key To Practicality Of Exceptionally Large Gate Arrays

Gate

(–)

Gate

(+)

Equivalent Circuit, P-Channel MOSFET

PP

Equivalent Circuit, N-Channel MOSFET

Gate

(+)

Gate

(–)

NN

And at least one of the two N-channel switches

opens, disconnecting the negative supply voltage.

Gate

Oxide

Insulation

MOSFET

Metal

Channel

Silicon Substrate

N - Channel

MOSFET

Gate

NN

P

P - Channel

MOSFET

NAND GATE

(Input A Assumed

Negative; B ,

Positive)

NAND GATE

(Inputs A and B

assumed positive)

(–)

C

A

B

P

P

N

N

(+)

(+)

(–)

Gate

PP

N

(+)

(–)

C

A

B

P

P

N

N

(–)

(+)

(+)

(+)

PART IX Advanced Concepts

540

the production of integrated-circuit chips containing hun-

dreds of thousands of usable NAND gates.

The VLSIs used in a processor are mounted on plug-in

circuit boards, called modules. Their makeup and electrical

grouping are crucial to the processor’s efficiency.

Efficient Modular Design

The goal here is to implement the processor with stan-

dard modules while— in the interest of low cost and ease

of logistic support—keeping the number of different types

of modules to a minimum. For a radar, most of the proces-

sor’s modules are of four basic types:

•

General-purpose processing

• Global bulk memory

• Signal processing • Interface

To these may be added a relatively small number of special-

purpose modules. Depending on the physical design stan-

dard chosen, one or more PEs of the same type may be

included in a single module.

For operational simplicity and convenience in program-

ming, the PEs are grouped electrically—though not neces-

sarily physically—into clusters of various types.

One Approach to Clustering. A generic cluster of one

general type is illustrated in Fig. 4. It consists of a cluster-

control element and an appropriate mix of general-purpose

PEs and signal-processing PEs, all sharing a multiport glob-

al bulk memory. The cluster controller, itself, is a general-

purpose PE. A control bus provides low-latency control

paths from the cluster controller to each PE and the bulk

memory. Low-latency paths are also provided between each

PE and the bulk memory.

Up to a limit imposed by electrical considerations, as

many clusters of this sort may be included in a processor as

are necessary to meet processing requirements (Fig. 5).

4. A generic cluster. Number of PEs may vary. Array controller is

a general-purpose PE. Each of the others may be either gener-

al purpose or signal processing. Since all are not physically

collocated, this is considered a virtual cluster.

5. Generic four-cluster processor. Crossbar is implemented with gate array chips and modularized.

Cluster

Controller

PE PE PE PE

Control

Bus

Global Bulk

Memory

Test &

Maintenance

(TM) Bus

Crossbar Switch

Data

Data

Data

HSDB

Control

Signals &

Associated

Data

Parallel

Instruction

(PI) Bus

Bulk Memory

Fiber

Optic

Fiber

Optic

Fiber

Optic

Fiber

Optic

NIU

Data

Bulk Memory

Bulk Memory

Bulk Memory

NIU

NIU

NIU

NIU