Фафурин В.А., Терюшов И.Н. Автоматизация технологических процессов и производств

Подождите немного. Документ загружается.

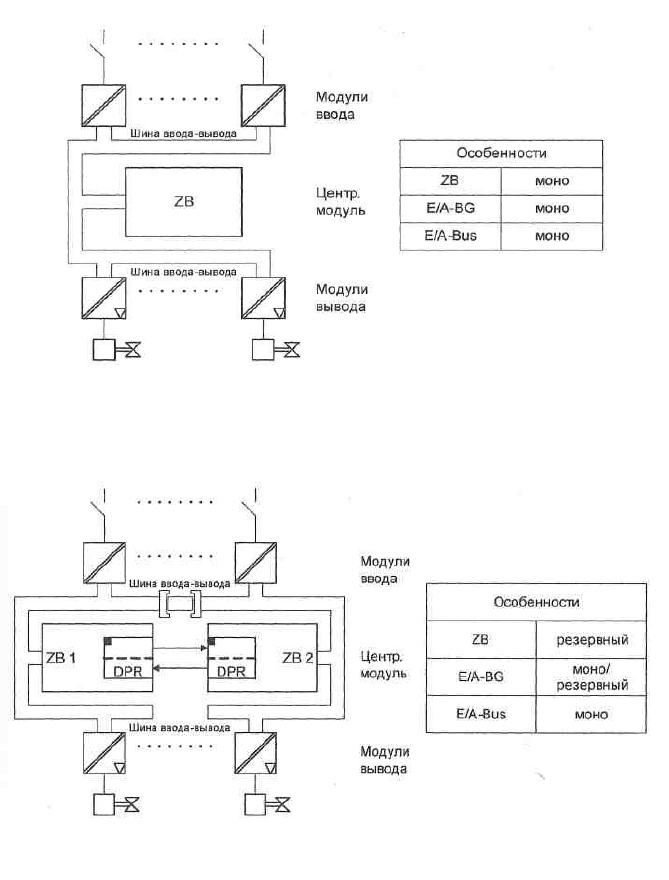

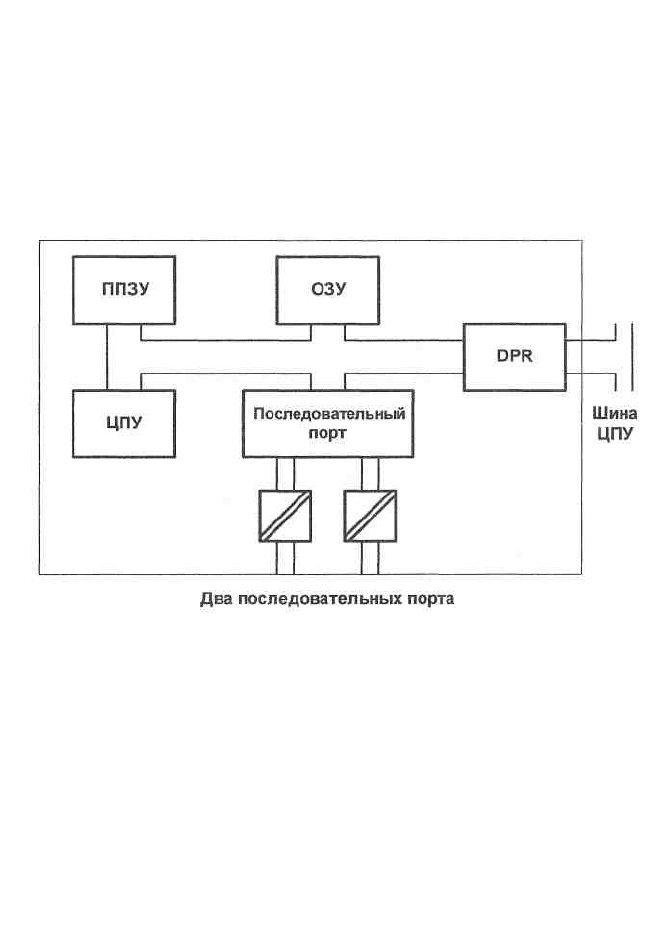

Рис. 7.1.27

Блок-схема системы H41q-H, HS/H51q-H, HS

Рис. 7.1.28

Концепция H41q-HR, HRS / H51q-HR, HRS (рис. 7.1.29). H41q-

HR / H51q-HR - резервированные центральные модули и

двухканальная шина ввода-вывода для PES высокой готовности. H41q-

HRS / H51q-HRS - резервированные двухпроцессорные центральные

модули и двухканальная шина ввода-вывода для безопасных систем

высокой готовности. Сертифицировано TUV для классов 1 - 6

стандарта DIN V 19250.

Блок-схема системы H41q-HR, HRS/H51q-HR, HRS

Рис. 7.1.29

Особенности архитектуры:

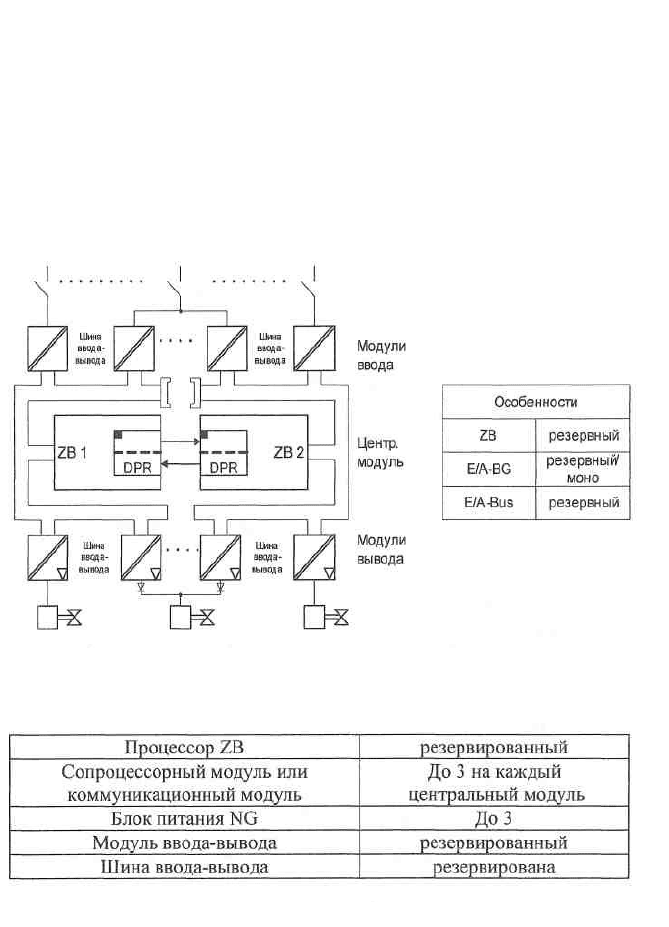

Структурная схема комплекса H51q-HRS представлена на рис. 7.1.30

Структурная схема комплекса Н51q-HRS

Рис. 7.1.30

Обозначения:

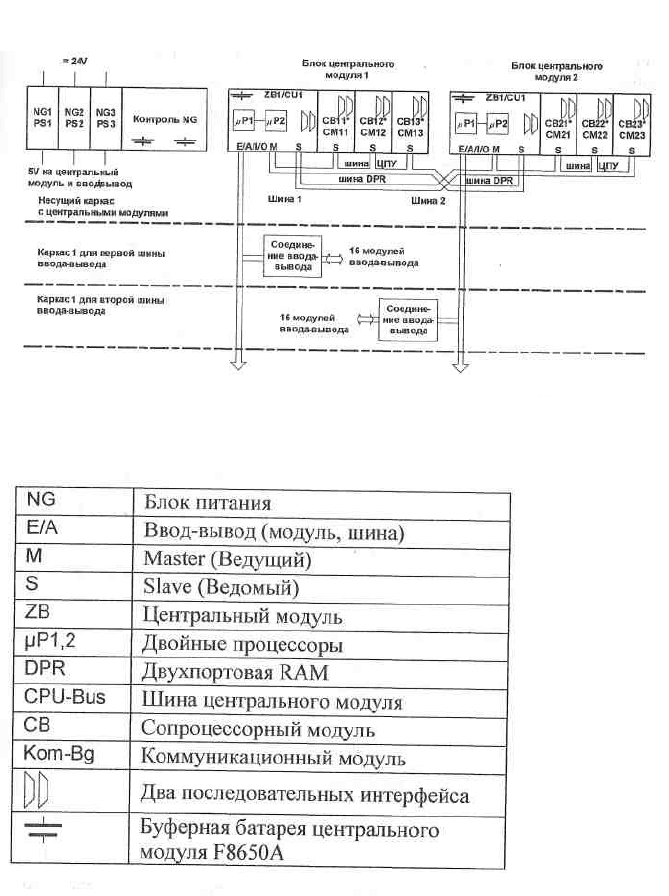

Центральный модуль F 8650A (сертифицирован TUV). Безо-

пасный центральный модуль для комплекса H51q-HRS. Состоит из

цементов, представленных на структурной схеме рис. 7.1.31.

Структура центрального модуля F 8650А

Рис. 7.1.31

Общие характеристики:

• Два микропроцессора с тактовой синхронизацией

• Каждый микропроцессор имеет собственное ОЗУ. При этом

один процессор работает с обычными данными и программами, а

другой - с инвертированными.

• Тестируемый аппаратный компаратор для сравнения резуль-

татов на шинах данных обоих микропроцессоров. При возникновении

разницы срабатывает механизм обнаружения неисправности, и сигнал

контроля времени переводится в безопасное состояние. Состояние

процессора выводится на табло.

• ППЗУ типа Flash EPROM для хранения ОС и прикладных

программ с мин. 100 тыс. циклов записи.

• ОЗУ типа SRAM.

• Мультиплексор для подключения шины ввода-вывода, DPR

или резервного центрального модуля.

• Резервное питание ОЗУ SRAM от буферных батарей в цен-

тральном модуле и на основной плате. Обе батареи контролируются

на наличие и величину напряжения.

• Два интерфейса RS 485 с гальванической развязкой и скоро-

стью передачи до 57600 бит/сек. Переключение на 9600 бит/сек и

57600 бит/сек переключателем или программно (программно

доступны и другие скорости). Значения скорости, установленные

программно, имеют приоритет.

• Индикатор состояния и диагностики и два светодиода для

отображения информации о системе, блоке модулей ввода-вывода, и

прикладной программе.

• Двустороннее ОЗУ (DPR) для быстрого, взаимного доступа к

памяти со второго центрального модуля.

• Системные часы с резервированием питания через буферную

батарею.

• Логика шины ввода-вывода для соединения с модулями ввода-

вывода.

• Тестируемый контроль блоков питания с напряжением 5 В.

• Контроль состояния буферных батарей.

Сопроцессорный модуль F 8621А (рис. 7.1.32). Справа от

каждого из центральных модулей комплекса H51q-HRS можно

установить до трех сопроцессорных модулей. Основные элементы

сопроцессорного модуля:

• Микропроцессор HD 64180 с тактовой частотой 10 МГц.

• EPROM с операционной системой.

• ОЗУ для хранения прикладной программы ведущего ком-

плекса (мастер-программа).

• Два интерфейса RS 485 со скоростью 57600 бит/сек.

• Двустороннее ОЗУ (DPR) для связи с центральным модулем.

Рис. 7.1.32

Примечание: Питание ОЗУ для хранения мастер - программы

имеет в качестве резервного источника буферные батареи основной

платы комплекса.

Коммуникационный модуль F 8625/F 8626. Справа от цен-

трального модуля комплекса H51q-HRS можно установить до пяти

коммуникационных модулей. Основные элементы коммуникацион-

ного модуля:

• 32-разрядный микропроцессор

• Операционная система

• ОЗУ для приема протоколов

• F 8625 Ethernet-интерфейс

• F 8626 Profibus-DP - интерфейс

• Двустороннее ОЗУ (DPR) для связи с центральным модулем

по шине I.

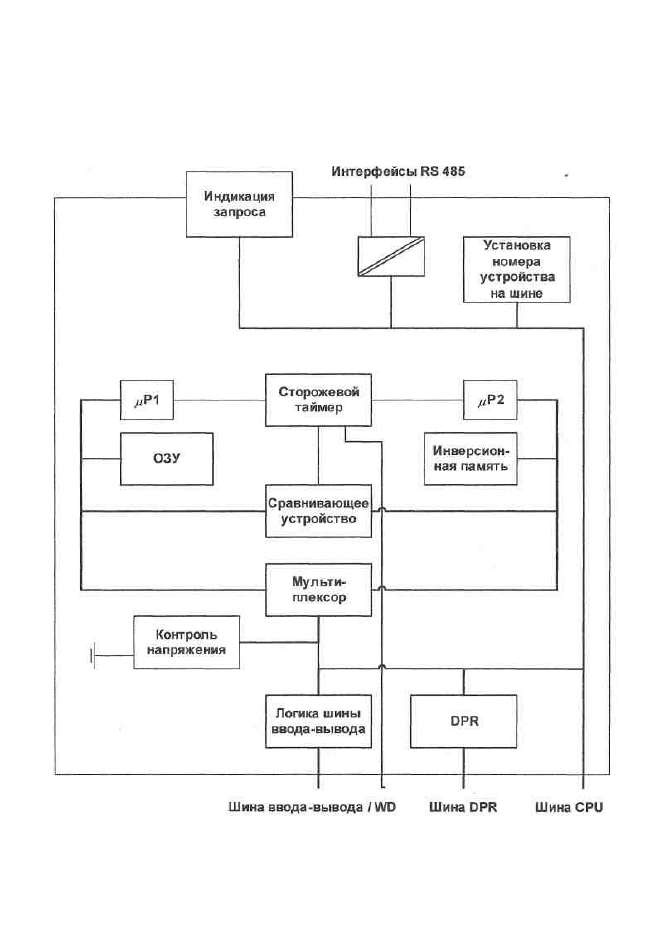

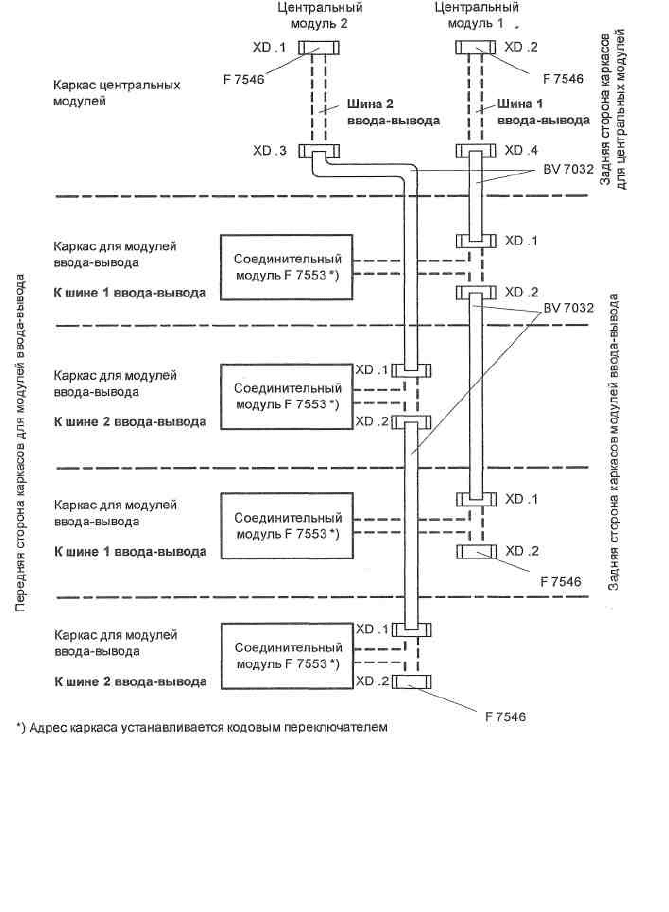

Шина ввода-вывода (рис. 7.1.33). Обмен данными между

уровнем ввода-вывода и центральными модулями осуществляется

через шину ввода-вывода. Так как шина ввода-вывода выполнена в

резервированном варианте, каждый из обоих центральных приборов

имеет собственную шину ввода-вывода, и, соответственно, только ему

присвоенные каркасы модулей ввода-вывода.

На первую шину ввода-вывода назначен центральный модуль 1,

а на вторую - центральный модуль 2. В каркас центральных модулей

интегрированы модули для соединения шины ввода-вывода. К

каркасу для модулей ввода-вывода шина ввода-вывода подключается

через соединительный модуль F 7553. Шины ввода-вывода отдельных

стоек соединяются с задней стороны с помощью кабеля BV 7032. Для

замыкания шины ввода-вывода в начале и в конце используется мо-

дуль F 7546. Принципиальная схема шины ввода-вывода приведена на

рис. 7.1.33.

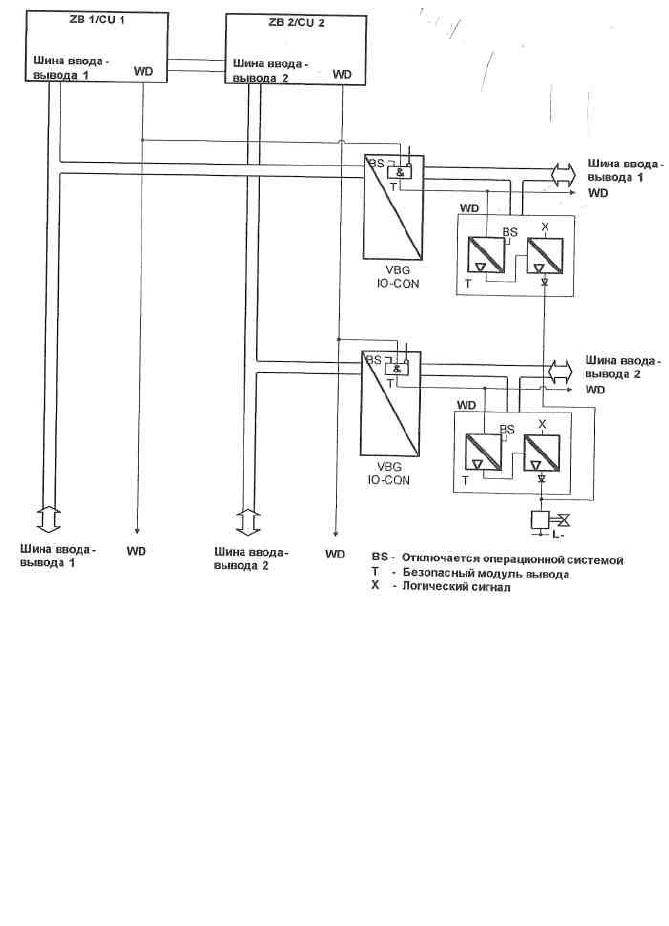

Аварийное отключение (рис. 7.1.34). В случае возникновения

неисправностей установка должна быть переведена в безопасное со-

стояние. Безопасное состояние комплекса определяется как состояние

минимального энергетического уровня на всех выходах. В зави-

симости от установленного типа реакции на неисправность исполь-

зуются различные способы отключения.

Если в связи с возникновением неисправности в системе H51q-

HRS требуется централизованное выключение, отключается сторо-

жевой таймер контроля времени (WD) соответствующего централь-

ного модуля.

Принципиальная схема шины ввода-вывода

Рис. 7.1.33

Схема аварийного отключения

Рис. 7.1.34

Программный продукт SILense. Фирма HIMA обладает пол-

ным пакетом средств конфигурирования своих систем, таким как

ELOP II. Но что действительно делает подход HIMA уникальным - это

пакет SILense, позволяющий производить расчеты надежности

проектируемой системы безопасности в конкретном применении. Это

полностью соответствует рекомендациям МЭК, и находится в

согласии с отечественным ГОСТом 34.602 на создание АС.

Пакет первым получил сертификат TUV на право проведения

расчетов надежности - как отдельных контуров защиты, так и системы

безопасности в целом в полном соответствии со стандартом IEC

61508. И в полном соответствии с требованиями МЭК, расчеты про-

водятся не только для центральной части системы - контроллера, но

для всего контура безопасности, включая датчики и исполнительные

устройства. Пакет имеет обширную библиотеку по параметрам на-

дежности сертифицированного оборудования систем безопасности

для подавляющего большинства фирм-изготовителей полевого обо-

рудования. При появлении нового оборудования библиотека может

быть дополнена.

Возможности пакета таковы, что для него требуется отдельное

представление. Конкретные особенности пакета будут подробно рас-

смотрены в главе 6 "Проектная оценка надежности системы ".

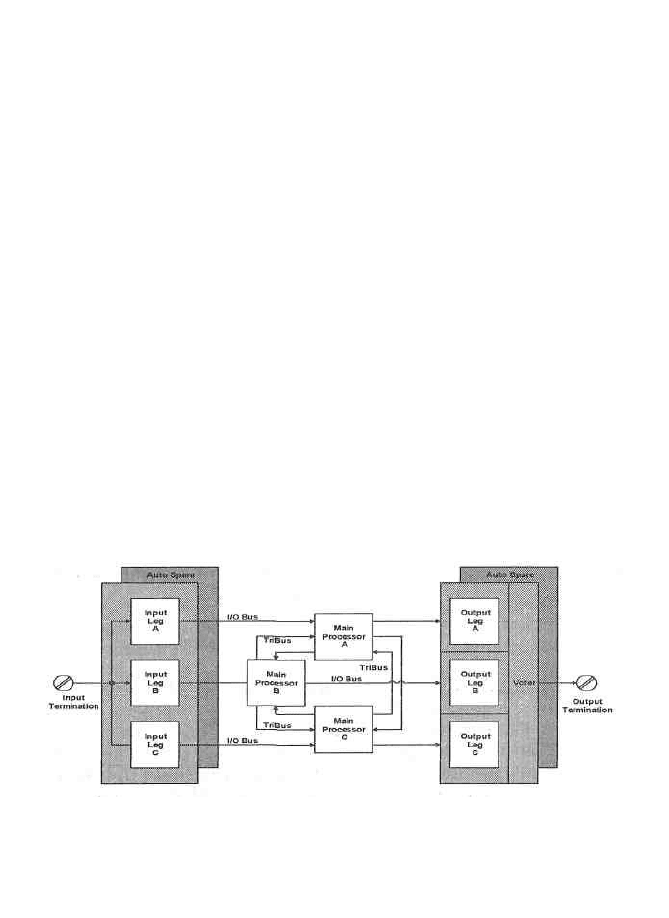

22. Контроллер с тройным модульным резервированием

Tricon (Tnvensys Systems Inc.)

Основные технические решения. Базовая система безопасно-

сти фирмы Triconex спроектирована с использованием троированного

контроллера Tricon V9, разработанного специально для управления

критическими и аварийными ситуациями. Реализованная в системе

философия построения системы объединяет высокую надежность и

высокую готовность. Троированная технология обеспечивает высокий

уровень обеспечения безопасности и надежности (рис. 7.1.35).

Рис. 7.1.35

Система TRICON спроектирована как система, которая обесто-

чивает выходы при возникновении аварийной ситуации. Это значит,