Иванов Ю.И., Югай В.Я. Интерфейсы средств автоматизации

Подождите немного. Документ загружается.

171

Продолжение табл. 4.4

Тип

Производи-

тель

Интернет-

сайт

CAN-версия

Наличие МК

Примечание

C515C

Infineon

www.infineon

.com

2.0B 8-bit

64k OTP, ROMless, 32k or 64k

ROM, 4 x PWM

SAE81C90/91

Infineon

www.infineon

.com

2.0Bp none 2 x 8-bit I/O ports

IniCAN

Inicore

www.inicore.

com

2.0B

8-bit or

DSP

technology independend functions

for chip integrations

AN82527

Intel

developer.intel.

com

2.0B none

AN87C196CA

Intel

developer.intel.

com

2.0B 16-bit

172

Окончание табл. 4.4

Тип

Производи-

тель

Интернет-

сайт

CAN-версия

Наличие МК

Примечание

MCP2510

Microchip

www.microch

ip.com

2.0B none

Stand-alone CAN Controller, SPI

Interface, PDIP/SOIC18,

TSSOP20

PIC18C658

Microchip

www.microch

ip.com

2.0B 8-bit

RISC MCU with 32K-byte Pro-

gram Memory, 1.5K-bytes of

SRAM, CAN 2.0B, 10bit-ADC, 9-

bit Addressable USART, SPI,

I2C,2xPWM's, in a 68L PLCC,

64L TQFP

PIC18C858

Microchip

www.microch

ip.com

2.0B 8-bit

RISC MCU with 32K-byte Pro-

gram Memory, 1.5K-bytes of

SRAM, CAN 2.0B, 10bit-ADC, 9-

bit Addressable USART, SPI, I2C,

2xPWM's, in a 80L TQFP, 84L

PLCC

CDC0806E

Micronas

www.micronas.

com

1 x 2.0B 8-bit Flash 56k Byte Flash, 16 time-stamps

CDC1607F

Micronas

www.micronas.

com

3 x 2.0B 16-bit Flash

256k Byte Flash, 3 independent

CAN-Modules, 16 time-stamps

173

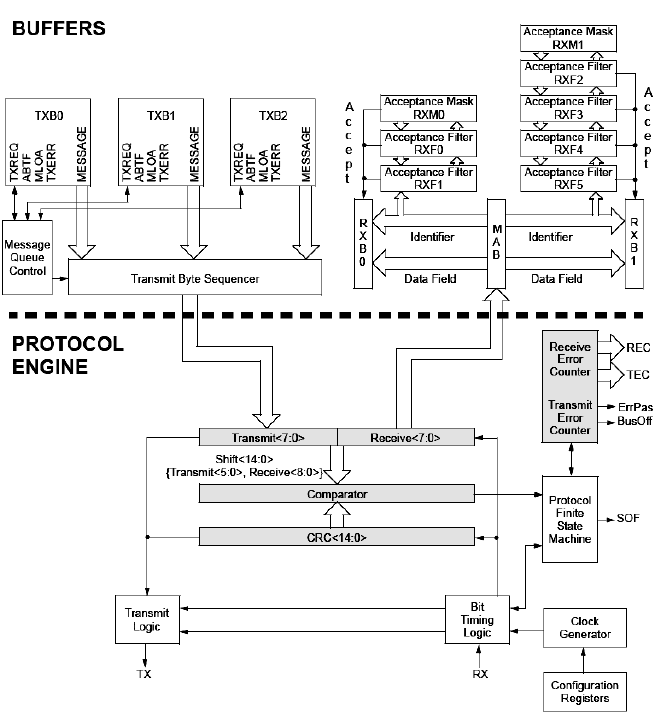

CAN-модуль состоит из двух основных узлов: буфера сообщений и кон-

троллера протокола (рис. 4.8). Буферы сообщений обеспечивают хранение

данных, обычно эти буферы раздельные для приема и передачи сообщений.

Буфер приема производит хранение принятых сообщений до начала их обра-

ботки. Буфер передачи должен сохранять, по крайней мере, одно передавае-

мое сообщение, так

как передача может начинаться только при незанятой

шине, и, кроме того, не каждая начатая передача может завершиться успеш-

но.

Рис. 4.8. Функциональные узлы CAN-модуля

174

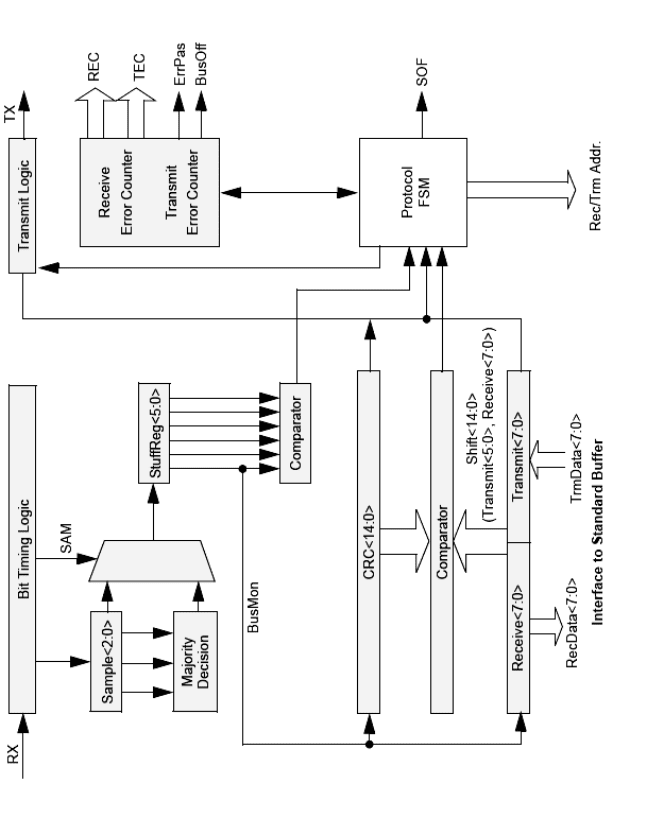

В свою очередь контроллер протокола состоит из нескольких блоков, по-

казанных на рис. 4.9. Основной частью контроллера является управляющий

блок – FSM. Это последовательный конечный автомат с изменением управ-

ляющих сигналов при различных типах сообщений и различных состояниях

передачи/приема данных.

FSM выполняет следующие функции:

• управление последовательным потоком данных между TX/RX и

сдвиговым регистром

;

• вычисление и контроль CRC;

• обработка ошибок;

• управление параллельным потоком данных между сдвиговым реги-

стром и буфером;

• выполнение арбитража;

• сигнализация об ошибках согласно CAN протоколу;

• автоматическая повторная передача сообщений.

Интерфейс передачи данных от контроллера к буферу – параллельный 8-

разрядный. Сообщение разбивается на байты для побайтового обмена дан-

ными

между буфером и сдвиговым регистром. FSM контролирует последова-

тельность байтов от начала сообщения до его завершения.

Регистр циклического контроля избыточности (CRC) формирует CRC код,

который побайтно будет передан при передаче данных, и проверяет код CRC

при получении сообщения.

Логика управления обработкой ошибок (EML) формирует сигнал о неис-

правности CAN-модуля. Состояния счетчиков ошибок передачи и

приема

увеличиваются или уменьшаются сигналами процессора потока. Согласно

значениям счетчиков ошибок CAN модуль может находиться в состоянии:

• активной ошибки;

• пассивной ошибки;

• отключен от шины.

С помощью BTL осуществляется контроль линейного входа шины: обра-

батывается состояние шины и выполняется синхронизация бита с коррекцией

временных интервалов согласно CAN-протоколу. BTL синхронизируется при

переходе

от “recessive” к “dominant” биту. Синхронизация производится из-

менением программируемых временных сегментов битового интервала для

компенсации изменений времени распространения и смещения фазы приня-

того сигнала. Программирование BTL зависит от скорости передачи данных

и физического времени запаздывания сигналов в канале связи.

175

Рис. 4.9. Контроллер протокола

176

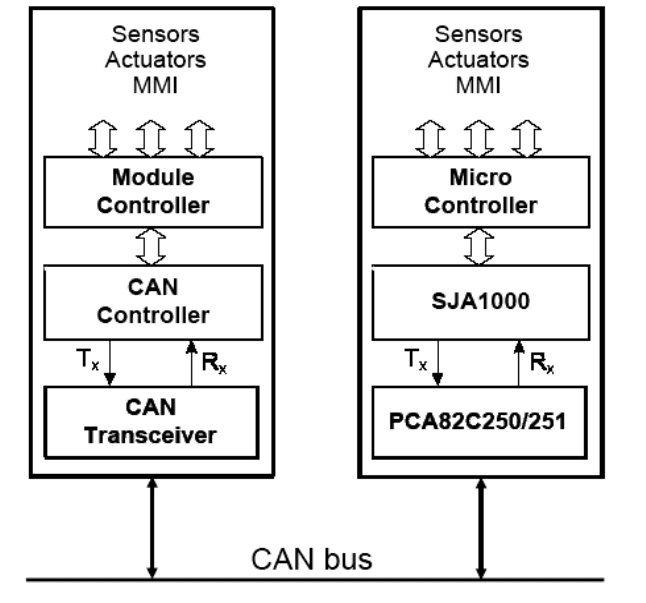

Рассмотрим построение CAN-сети на основе микроконтроллера, CAN-

контроллера и CAN-трансивера. Структурная схема сети на основе микро-

схем фирмы Philips показана на рис. 4.10.

Рис. 4.10. Схема CAN-сети на основе изделий фирмы Philips

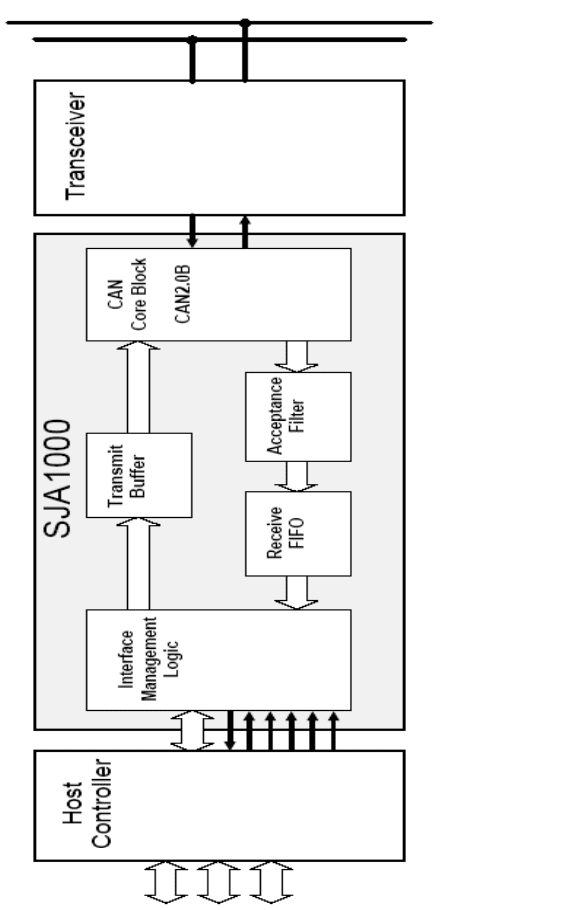

Связь микроконтроллера с CAN-контроллером SJA1000 Philips осущест-

вляется с помощью параллельного интерфейса (рис. 4.11). Стандартная схема

подключения CAN-контроллера SJA1000 к микроконтроллеру и трансиверу

показана на

рис. 4.12. Параллельный интерфейс с использованием запросов

прерываний необходим для обработки поступающих сообщений в реальном

масштабе времени. Взаимодействие CAN-контроллера с трансивером обес-

печивается сигналами T

X

, R

X

в полнодуплексном режиме,

177

Рис. 4.11. Функциональная схема CAN-контроллера SJA1000

178

Рис. 4.12. Схема внешних соединений CAN-контроллера SJA1000

179

так как алгоритмы контроля и арбитража требуют одновременной обработки

передаваемых сигналов и сигналов, реально присутствующих в CAN шине.

Все основные функции протокола по управлению обменом данными CAN-

контроллер выполняет самостоятельно и полностью обеспечивает прием и

передачу сообщений по коммуникационной сети со всеми необходимыми

процедурами контроля. Ресурсы основного микроконтроллера (Host

controller) освобождаются и должны использоваться

только для обработки

сообщений.

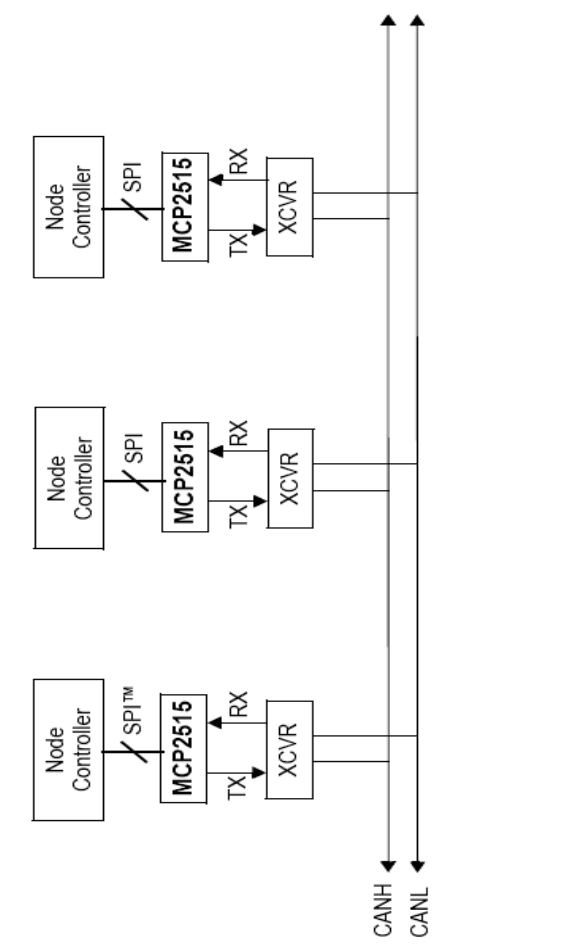

Автономный CAN-контроллер MCP2515 с SPI-интерфейсом выпускает

фирма Microchip. Организация микроконтроллерной сети на основе этой

микросхемы показана на рис. 4.13, а функциональная схема MCP2515 – на

рис. 4.14. SPI-интерфейс в сочетании с дополнительными сигналами преры-

ваний позволяет реализовать эффективные процедуры обмена данными с ми-

нимальным числом линий связи и необходимым временем реакции для

CAN-

контроллера.

Из приведенных примеров средств для построения CAN-сети видно, что

изделия многих фирм обладают сходными характеристиками, в полной мере

позволяют реализовать необходимые процедуры протокола. При проектиро-

вании средств автоматизации весьма широкая номенклатура изделий предос-

тавляет возможность выбора необходимых компонентов с учетом многих до-

полнительных факторов.

180

Рис. 4.13. CAN-сеть на основе контроллера MCP2515