Гордеев А.В. Операционные системы

Подождите немного. Документ загружается.

Защита адресного пространства задач

121

Изложенный вкратце аппаратный механизм защиты по привилегиям оказывается

довольно сложным и жестким. Однако поскольку все практические ситуации учесть

в схемах микропроцессора невозможно, то при разработке процедур операцион-

ных систем и иного привилегированного кода следует придерживаться приведен-

ных ниже рекомендаций, заимствованных из [8].

Основной риск связан с передачей управления через шлюз вызова более привиле-

гированной процедуре. Нельзя предоставлять вызывающей программе никаких

преимуществ, вытекающих из-за временного повышения привилегий. Это особенно

важно для процедур нулевого уровня привилегий (PLO-процедур).

Вызывающая программа может нарушить работу процедуры, передавая ей «пло-

хие» параметры. Поэтому целесообразно как можно раньше проконтролировать

передаваемые процедуре параметры. Шлюз вызова сам по себе не проверяет зна-

чений параметров, которые копируются в новый стек, поэтому достоверность каж-

дого передаваемого параметра должна контролировать вызванная процедура. Ниже

перечислены некоторые рекомендации по контролю передаваемых параметров.

• Следует проверять счетчики циклов и повторений на минимальные и макси-

мальные значения.

• Необходимо проверить 8- и 16-разрядные параметры, передаваемые в 32-раз-

рядных регистрах. Когда процедуре передается короткий параметр, его следует

расширить знаковым разрядом или нулем для заполнения всего 32-разрядного

регистра.

• Следует стремиться свести к минимуму время работы процессора с запрещен-

ными прерываниями. Если процедуре требуется запрещать прерывания, необ-

ходимо, чтобы вызывающая программа не могла влиять на время нахождения

процессора с запрещенными прерываниями (флаг IF = 0).

• Процедура никогда не должна воспринимать как параметр код или указатель

на код.

• В операциях процессора следует явно задавать состояние флага направления

DF для цепочечных команд.

Q Заключительная команда RET или RET n в процедуре должна точно соответ-

ствовать полю WC (Word Counter — счетчик слов) шлюза вызова; при этом

п = 4 х WC, так как счетчик задает число двойных слов, а п соответствует байтам.

а

Не следует применять шлюзы вызовов для функций, которым передается пере-

менное число параметров (см. предыдущую рекомендацию). При необходимо-

сти нужно воспользоваться счетчиком и указателем параметров.

Q

Функции не могут возвращать значения в стеке (см. предыдущую рекоменда-

цию), так как после возврата стеки процедуры и вызывающей программы нахо-

дятся точно в таком состоянии, в каком они были до вызова.

u

В Процедуре следует сохранять и восстанавливать все сегментные регистры. Без

этого, если какой-либо сегментный регистр привлекался для адресации дан-

ных, недоступных вызывающей программе, процессор автоматически загрузит

в

него пустой селектор.

122 Глава 4. Особенности архитектуры микропроцессоров i80x86

Рекомендуется контролировать все обращения к памяти. Нетрудно представить себе

ситуацию, когда РЬЗ-программа' передает PLO-процедуре указатель селектор -.сме-

щение и запрашивает считать или записать несколько байтов по этому адресу. Ти-

пичным примером может служить процедура дискового ввода-вывода, которая вос-

принимает как параметр системный номер файла, счетчик байтов и адрес, по которому

записываются данные с диска. Хотя PLO-процедура имеет привилегии для произ-

водства такой операции, у РЬЗ-программы разрешения на это может не быть.

Система прерываний 32-разрядных

микропроцессоров i80x86

В микропроцессорах семейства i80x86 система прерываний построена таким обра-

зом, чтобы, с одной стороны, обеспечить возможность создавать эффективные и на-

дежные мультипрограммные и мультизадачные операционные системы, которые

должны функционировать в защищенном режиме, а с другой стороны, обеспечить

возможность выполнять программы, разработанные для реального режима. Рас-

смотрим вкратце оба режима.

Работа системы прерываний в реальном режиме

В реальном режиме работы в системе прерываний используется понятие вектора

прерывания, поскольку для указания адреса программы обработки прерывания

здесь требуется не одно значение, а два (значение для сегментного регистра кода

и значение для указателя команд), то есть мы имеем дело не со скалярной величи-

ной, а с «векторной», состоящей из двух скалярных.

Итак, каждый вектор прерывания состоит из четырех байтов, или двух слов: пер-

вые два содержат новое значение для регистра IP, а следующие два — новое значе-

ние для регистра CS. Таблица векторов прерывания занимает 1024 байт. Таким об-

разом, в ней может быть задано 256 векторов прерываний. В процессоре i8086 эта

таблица располагается на адресах 00000H-003FFH. Расположение этой таблицы

в процессорах i80286 и в более поздних определяется значением регистра IDTR

(Interrupt Descriptor Table Register — регистр таблицы дескрипторов прерываний).

При включении или сбросе процессора i80x86 этот регистр обнуляется. Однако

при необходимости можно в регистре IDTR указать смещение и таким образом

перейти на новую таблицу векторов прерываний.

Таблица векторов прерываний заполняется (инициализируется) при запуске сис-

темы, но, в принципе, может быть изменена или перемещена.

Каждый вектор прерывания имеет свой номер, называемый номером прерывания,

который указывает его место в таблице. Этот номер, помноженный на четыре (сдвиг

на два разряда влево и заполнение освободившихся битов нулями) и сложенный

с содержимым регистра IDTR, дает абсолютный адрес первого байта вектора пре-

рываний в оперативной памяти.

Программа, имеющая уровень привилегий 3. Иначе говоря, работающая в кольце защиты с номером

система прерываний 32-разрядных микропроцессоров J80x86 1 23

Подобно вызову процедуры прерывание заставляет микропроцессор сохранить в

стеке информацию для последующего возврата, а затем перейти к группе команд,

адрес которых определяется вектором прерывания. Таким образом, прерывание

вызывает косвенный переход к своей подпрограмме обработки за счет получения

ее адреса из вектора прерывания.

В IBM PC, как и в других вычислительных системах, прерывания бывают двух

видов: внутренние и внешние.

Внутренние прерывания, как мы уже знаем, возникают в результате работы про-

цессора в ситуациях, которые нуждаются в специальном обслуживании, или при

выполнении специальных команд (INT, INTO). Это следующие прерывания:

О прерывание при делении на ноль (номер прерывания 0);

• прерывание по флагу TF (Trap Flag — флаг трассировки)

1

обычно исполь-

зуется специальными программами отладки типа DEBUG (номер прерыва-

ния 1);

Q прерывания, возникающие при выполнении команд INT (Interrupt — прерыва-

ние) и INTO (Interrupt if Overflow — прерывание по переполнению), называют-

ся программными.

В качестве операнда команды INT указывается номер прерывания, которое нужно

выполнить, например INT 10H. Программные прерывания как средство перехода

на соответствующую процедуру были введены для того, чтобы выполнение этой

процедуры осуществлялось в привилегированном режиме, а не в обычном пользо-

вательском.

Внешние прерывания возникают по сигналу какого-нибудь внешнего устройства.

Существует два специальных внешних сигнала среди входных сигналов процессо-

ра, при помощи которых можно прервать выполнение текущей программы и тем

самым переключить работу центрального процессора. Это сигналы NMI (No Mask

Interrupt — немаскируемое прерывание) и INTR (Interrupt Request — запрос на

прерывание). Соответственно, внешние прерывания подразделяются на немаски-

руемые и маскируемые.

Маскируемые прерывания генерируются контроллером прерываний по заявке оп-

ределенных периферийных устройств

2

. Контроллер прерываний (его обозначение

18259А) поддерживает восемь уровней (линий) приоритета; к каждому уровню

«привязано» одно периферийное устройство

3

. Маскируемые прерывания часто

называют аппаратными прерываниями.

Флаг трассировки — специальный бит в регистре PSW (Program Status Word — слово состояния

программы), который в случае равенства единице вызывает приостанов после каждой команды и

генерирует прерывание для организации режима отладки с пошаговым выполнением программы.

2

Чаще всего регистр PSW в микропроцессорах Intel 80x86 называют регистром ([шагов.

Сигнал запроса на прерывание чаще всего является сигналом готовности внешнего устройства (со-

ответствующего контроллера внешнего устройства) па выполнение следующей команды, связанной

3

с

Управлением операциями ввода-вывода.

качестве внешнего периферийного устройства, занимающего одну линию запроса на прерывание,

Может быть использовано специальное управляющее устройство, которое позволяет разделять эту

самую линию запроса между несколькими внешними устройствами.

124

Глава 4. Особенности архитектуры микропроцессоров J80x86

Как известно, прерывания могут быть инициированы внешним устройством ПЭВМ

или специальной командой прерывания из программы. В любом случае если пре-

рывания разрешены, то выполняется следующая процедура.

1. В стек помещается регистр флагов PSW.

2. Флаг включения-выключения прерываний IF и флаг трассировки TF, находя-

щиеся в регистре PSW, обнуляются для блокировки других маскируемых пре-

рываний и исключения пошагового режима исполнения команд.

3. Значения регистров CS и IP сохраняются в стеке вслед за PSW.

4. Вычисляется адрес вектора прерывания и из вектора, соответствующего номе-

ру прерывания, загружаются новые значения IP и CS.

Когда системная подпрограмма принимает управление, она может разрешить сно-

ва маскируемые прерывания командой STI (Set Interrupt Flag — установить флаг

прерываний), которая переводит флаг IF в состояние 1, что разрешает микропро-

цессору вновь реагировать на прерывания, инициируемые внешними устройства-

ми, поскольку стековая организация допускает вложение прерываний друг в друга.

Закончив работу, подпрограмма обработки прерывания должна выполнить команду

IRET (Interrupt Return), которая извлекает из стека три 16-разрядных значения и

загружает их в указатель команд IP, регистр сегмента команд CS и регистр PSW

соответственно. Таким образом, процессор сможет продолжить работу с того мес-

та, где он был прерван.

В случае внешних прерываний процедура перехода на подпрограмму обработки

прерывания дополняется следующими шагами.

1. Контроллер прерываний получает заявку от определенного периферийного

устройства и, соблюдая схему приоритетов, генерирует сигнал INTR (запрос на

прерывание), который является входным для микропроцессора.

2. Микропроцессор проверяет флаг IF в регистре PSW. Если он установлен в 1, то

переходим к шагу 3. В противном случае работа процессора не прерывается.

Часто говорят, что прерывания замаскированы, хотя правильнее говорить, что

они отключены. Маскируются (запрещаются) отдельные линии запроса на пре-

рывания посредством программирования контроллера прерываний.

3. Микропроцессор генерирует сигнал INTA (подтверждение прерывания). В от-

вет на этот сигнал контроллер прерываний посылает по шипе данных номер

прерывания. После этого выполняется описанная ранее процедура передачи

управления соответствующей программе обработки прерывания.

Номер прерывания и его приоритет устанавливаются на этапе инициализации си-

стемы. После запуска ОС пользователь, как мы уже отмечали, может изменить

таблицу векторов прерываний, поскольку она ему доступна.

Работа системы прерываний

в защищенном режиме

В защищенном режиме работы система прерываний микропроцессора i80x86 ра-

ботает совершенно иначе. Прежде всего, вместо таблицы векторов, о которой МЫ

Пистема прерываний 32-разрядных микропроцессоров J80x86 125

говорили выше, она имеет дело с таблицей дескрипторов прерываний (Interrupt

Descriptor Table, IDT). Дело здесь не столько в названии таблицы, сколько в том,

что таблица ЮТ представляет собой не таблицу с адресами обработчиков преры-

ваний, а таблицу со специальными системными структурами данных (дескриптора-

ми), доступ к которой со стороны пользовательских (прикладных) программ невоз-

можен. Только сам микропроцессор (его система прерываний) и код операционной

системы могут получить доступ к этой таблице, представляющей собой специаль-

ный сегмент, адрес и длина которого содержатся в регистре IDTR (см. рис. 4.2).

Этот регистр аналогичен регистру GDTR в том отношении, что он инициализиру-

ется один раз при загрузке системы. Интересно заметить, что в реальном режиме

работы регистр IDTR также указывает на адрес таблицы прерываний, но при этом,

как и в процессоре i8086, каждый элемент таблицы прерываний (вектор) занимает

всего 4 байт и содержит 32-разрядный адрес в формате селектор -.смещение (CS:IP).

Начальное значение этого регистра равно нулю, но в него можно занести и другое

значение. В этом случае таблица векторов прерываний будет находиться в другом

месте оперативной памяти. Естественно, что перед тем, как занести в регистр IDTR

новое значение, необходимо подготовить саму таблицу векторов. В защищенном

режиме работы загрузку регистра IDTR может произвести только код с максималь-

ным уровнем привилегий.

Каждый элемент в таблице дескрипторов прерываний, о которой мы говорим уже

в защищенном режиме, представляет собой 8-байтовую структуру, более похожую

на дескриптор шлюза, нежели на дескриптор сегмента.

Как мы уже знаем, в зависимости от причины прерывания процессор автомати-

чески индексирует таблицу прерываний и выбирает соответствующий элемент,

с помощью которого и осуществляется перенаправление в исполнении кода, то есть

передача управления на обработчик прерывания. Однако таблица IDT содержит

только дескрипторы шлюзов, а не дескрипторы сегментов кода, поэтому факти-

чески получается что-то типа косвенной адресации, но с рассмотренным ранее

механизмом защиты с помощью уровней привилегий. Благодаря этому пользова-

тели уже не могут сами изменить обработку прерываний, которая предопределя-

ется системным программным обеспечением.

Дескриптор прерываний может относиться к одному из трех типов:

Q коммутатор прерывания (interrupt gate);

Q коммутатор перехвата (trap gate);

Q коммутатор задачи (t,ask gate).

Нри обнаружении запроса на прерывание и при условии, что прерывания разрешены,

процессор действует в зависимости от типа дескриптора (коммутатора), соответству-

ю

Щего номеру прерывания. Первые два'типа дескрипторов прерываний вызывают

Пе

реход на соответствующие сегменты кода, принадлежащие виртуальному адресно-

М

У пространству текущего вычислительного процесса. Поэтому про них говорят, что

°работка прерываний по этим дескрипторам осуществляется под контролем (в кон-

е

ксте) текущей задачи. Последний тип дескриптора (коммутатор задачи) вызывает

°лное переключение процессора на новую задачу со сменой всего контекста в соответ-

вии с сегментом состояния задачи (TSS). Рассмотрим оба варианта.

126

Глава 4. Особенности архитектуры микропроцессоров i80x86

Обработка прерываний в контексте текущей задачи

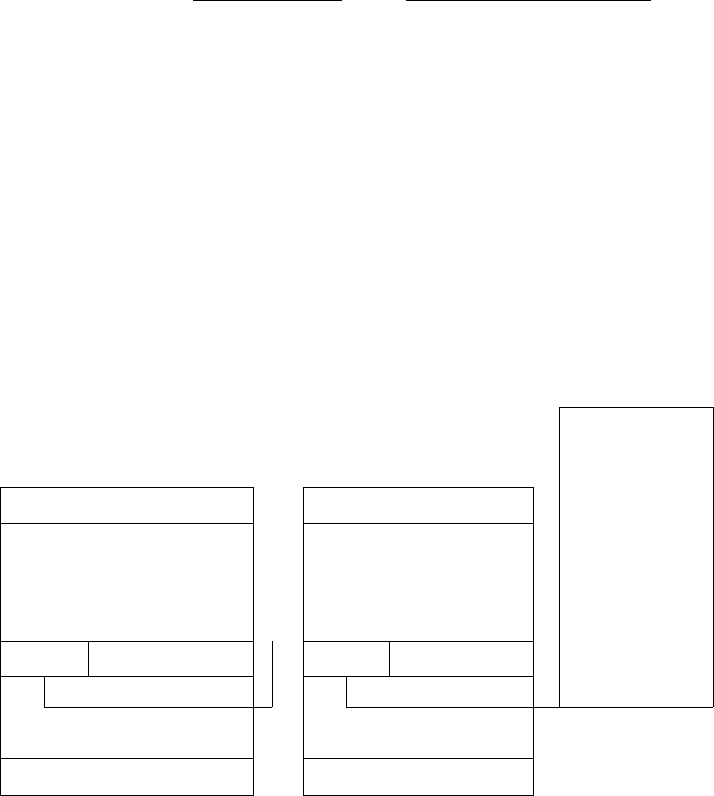

Обработку прерывания в контексте текущей задачи поясняет рис. 4.12.

Прерывание (исключение)

1

Регистр EIP

Регистр CS

Регистр дескриптора

сегмента

ТаблицаIDT

Дескриптор 225

Дескриптор j

Дескриптор 1

Дескриптор О

Регистр EFLAGS

Стек

2.1

Индекс i

2.3

RPL

2.2

4

Ti=0

—•

•

Ti

-

1

Таблица GDT

Дескриптор М

Дескриптор i

Дескриптор 0

Таблица LDT

Дескриптор М

Дескриптор i

Дескриптор 0

Рис. 4.12. Схема передачи управления при прерывании в контексте текущей задачи

При возникновении прерывания процессор по номеру прерывания индексирует

таблицу IDT, то есть адрес соответствующего коммутатора определяется путем

сложения содержимого поля адреса в регистре IDTR и номера прерывания, умно-

женного на 8 (справа к номеру прерывания добавляется три нуля). Полученный

дескриптор анализируется, и если его тип соответствует коммутатору перехвата

или коммутатору прерывания, то выполняются следующие действия.

1. В стек на уровне привилегий текущего сегмента кода помещаются:

• значения SS и SP, если уровень привилегий в коммутаторе выше уровня

привилегий ранее исполнявшегося кода;

Q регистр флагов EFLAGS;

• регистры CS и IP.

2. Если рассматриваемому прерыванию соответствовал коммутатор прерывания,

то запрещаются прерывания (устанавливается флаг IF = 0 в регистре EFLAGS)-

В случае коммутатора перехвата флаг прерываний не сбрасывается, и обработ-

ка новых прерываний на период обработки текущего прерывания тем самым не

запрещается.

рлгугема прерываний 32-разрядных микропроцессоров J80x86

127

Я Поле селектора из дескриптора прерывания используется для индексирования

таблицы дескрипторов задачи. Дескриптор сегмента заносится в теневой ре-

гистр, а смещение относительно начала нового сегмента кода определяется по-

лем смещения из дескриптора прерывания.

Таким образом, в случае обработки прерываний, когда дескриптором прерывания яв-

ляется коммутатор перехвата или коммутатор прерывания, мы остаемся в том же вир-

туальном адресном пространстве, и полной смены контекста текущей задачи не про-

исходит. Просто мы переключаемся на исполнение другого (как правило, более

привилегированного) кода, доступного исполняемой задаче. Этот код создается сис-

темными программистами, и прикладные программисты его просто используют. В то

же время механизмы защиты микропроцессора позволяют обеспечить недоступность

этого кода для его исправления (со стороны приложений, его вызывающих) и недо-

ступность самой таблицы дескрипторов прерываний. Удобнее всего код обработчи-

ков прерываний располагать в общем адресном пространстве, то есть селекторы, ука-

зывающие на такой код, должны располагаться в глобальной таблице дескрипторов.

Обработка прерываний с переключением на новую задачу

Совершенно иначе осуществляется обработка прерываний в случае, если дескрип-

тором прерываний является коммутатор задачи. Формат коммутатора задачи от-

личается от формата коммутаторов перехвата и прерывания прежде всего тем, что

в нем вместо селектора сегмента кода, на который передается управление, указы-

вается селектор сегмента состояния задачи (рис. 4.13). В результате осуществля-

ется процедура перехода на новую задачу с полной сменой контекста, ибо сегмент

состояния задачи полностью определяет новое виртуальное пространство и адрес

начала программы, а текущее состояние прерываемой задачи аппаратно (по мик-

ропрограмме микропроцессора) сохраняется в ее собственном сегменте TSS.

При этом происходит полное переключение на новую задачу с вложением, то есть

выполняются следующие действия.

1. Сохраняются все рабочие регистры процессора в текущем сегменте TSS, базовый

адрес этого сегмента берется в регистре TR (см. раздел «Адресация в 32-раз-

рядных микропроцессорах i80x86 при работе в защищенном режиме»).

2. Текущая задача отмечается как занятая.

3. По селектору из коммутатора задачи выбирается новый сегмент TSS (поле се-

лектора помещается в регистр TR) и загружается состояние новой задачи. На-

помним, что загружаются значения регистров LDTR, EFLAGS, восьми регист-

ров общего назначения, регистра EIP и шести сегментных регистров.

4

- Устанавливается бит NT (Next Task),.

* В поле обратной связи TSS помещается селектор прерванной задачи.

"• С помощью значений CS:IP, взятых из нового сегмента TSS, обнаруживается

11

выполняется первая команда обработчика прерывания.

а

ким образом, коммутатор задачи дает указание процессору произвести переклю-

н

ие задачи, и обработка прерывания осуществляется под контролем отдельной

1е

шней задачи. В каждом сегменте TSS имеется селектор локальной таблицы деск-

128

Глава 4. Особенности архитектуры микропроцессоров JSOXRR

рипторов (LDT), поэтому при переключении задачи процессор загружает в регистп

LDTR новое значение. Это позволяет обратиться к сегментам кода, которые абсо-

лютно не пересекаются с сегментами кода любых других задач, поскольку именно

локальные таблицы дескрипторов обеспечивают эффективную изоляцию вирту-

альных адресных пространств. Новая задача начинает свое выполнение на уровне

привилегий, определяемом полем RPL нового содержимого регистра CS, которое

загружается из сегмента TSS. Достоинством этого коммутатора является то, что

он позволяет сохранить все регистры процессора с помощью механизма переклю-

чения задач, тогда как коммутаторы перехвата и прерываний сохраняют только

содержимое регистров IFLAGS, CS и IP, а сохранение других регистров возлагает-

ся на программиста, разрабатывающего соответствующую программу обработки

прерывания.

I—

Номер прерывания

IDT

Дескриптор коммутатора задачи

Селектор

—•

GDT

Дескриптор сегмента TSS

Адрес

-ЭР

Сегмент TSS

Рис. 4.13. Схема передачи управления при прерывании с переключением на новую задачу

Справедливости ради следует признать, что несмотря на возможности коммутатора

задачи, разработчики современных операционных систем достаточно редко его ис-

пользуют, поскольку переключение на другую задачу требует существен но больших

затрат времени, а полное сохранение всех рабочих регистров часто не требуется. В ос-

новном обработку прерываний осуществляют в контексте текущей задачи, так как

это приводит к меньшим накладным расходам и повышает быстродействие системы-

Контрольные вопросы и задачи

1. Как в реальном режиме работы микропроцессоров i80x86 осуществляется пре

образование виртуального адреса в физический?

т-рппьные вопросы и задачи 1 29

Какие механизмы виртуальной памяти используются в защищенном режиме

работы микропроцессоров i80x86?

Для чего в микропроцессоры i80x86 введен регистр-указатель задачи TR? Ка-

кой он разрядности?

л Как в микропроцессорах i80x86 реализована поддержка сегментного способа

организации виртуальной памяти?

5 Что понимается под термином «линейный адрес»? Как осуществляется пре-

образование линейного адреса в физический? Может ли линейный адрес быть

равным физическому?

6 Что дало введение двухэтапной страничной трансляции в механизме странич-

ного способа реализации виртуальной памяти? Как разработчики микропро-

цессора i80386 решили проблему замедления доступа к памяти, которое при

двухэтапном преобразовании адресов очень существенно?

7. Что означает термин «плоская модель памяти»? В чем заключаются достоин-

ства (и недостатки, если они есть) этой модели?

8. Что дало введение виртуального режима? Как в этом режиме осуществляется

вычисление физического адреса?

9. Что имеется в микропроцессорах i80x86 для обеспечения защиты адресного

пространства задач?

10. Что такое «уровень привилегий»? Сколько уровней привилегий в микропро-

цессорах i80x86? Для каких целей введено такое количество уровней привиле-

гий?

И. Что такое текущий уровень привилегий? Как узнать, чему он равен? Что та-

кое эффективный уровень привилегий?

12. Объясните правила работы с уровнями привилегий для различных типов сег-

ментов.

13. Поясните работу механизма шлюзов. Для чего он предназначен, как осуществ-

ляется передача управления на сегменты кода с другими уровнями привиле-

гий?

14. Опишите работу системы прерываний микропроцессоров i80x86 в реальном

режиме.

15. В чем заключаются принципиальные отличия работы системы прерываний

микропроцессоров i80x86 в защищенном режиме по сравнению с реальным

режимом?

"• Как осуществляется переход на программу обработки прерываний, если де-

скриптор прерываний является коммутатором прерываний?

• Как осуществляется переход на программу обработки прерываний, если де-

скриптор прерываний является коммутатором перехвата?

• Как осуществляется переход на программу обработки прерываний, если дес-

криптор прерываний является коммутатором задачи?

Глава 5. Управление

вводом-выводом

в операционных системах

Побудительной причиной, в конечном итоге приведшей разработчиков к созда-

нию системного программного обеспечения, в том числе операционных систем,

стала необходимость предоставить программам средства обмена данными с внеш-

ними устройствами, которые бы не требовали непосредственного включения в каж-

дую программу двоичного кода, управляющего устройствами ввода-вывода. На-

помним, что программирование ввода-вывода является наиболее сложным

и трудоемким, требующим очень высокой квалификации. Поэтому код, реализу-

ющий операции ввода-вывода, сначала стали оформлять в виде системных биб-

лиотечных процедур, а потом и вовсе вывели из систем программирования, включив

в операционную систему. Это позволило не писать такой код в каждой программе,

а только обращаться к нему — системы программирования стали генерировать об-

ращения к системному коду ввода-вывода. Таким образом, управление вводом-

выводом — это одна из основных функций любой операционной системы.

С одной стороны, организация ввода-вывода в различных операционных системах

имеет много общего. С другой стороны, реализация ввода-вывода в ОС так сильно

отличается от системы к системе, что очень нелегко выделить и описать именно

основные принципы реализации этих функций. Проблема усугубляется еще и тем,

что в большинстве ныне используемых систем эти моменты вообще, как правило,

подробно не описаны (исключением являются только системы Linux и FreeBSD,

для которых имеются комментированные исходные тексты), а детально описыва-

ются только функции API, реализующие ввод-вывод. Другими словами, для тех

же систем Windows от компании Microsoft мы воспринимаем подсистему ввода-

вывода как «черный ящик». Известно, как можно и нужно использовать эту под-

систему, но детали ее внутреннего устройства остаются неизвестными. Поэтому

в данной главе мы рассмотрим только основные идеи и концепции. Наконец, по

скольку такой важный ресурс, как внешняя память, в основном реализуется н

устройствах ввода-вывода с прямым доступом, а к ним, прежде всего, относите

накопители на магнитных дисках, мы также рассмотрим логическую структуру Д

и