Гордеев А.В. Операционные системы

Подождите немного. Документ загружается.

Глава 4- Особенности

архитектуры

микропроцессоров i80x86

для организации

мультипрограммных

операционных систем

В рамках данной книги мы, естественно, не будем рассматривать все многообразие

современных 32-разрядных микропроцессоров, используемых в персональных

компьютерах и иных вычислительных системах, а ограничимся рассмотрением

только архитектурных, а не технических характеристик микропроцессоров, и под

обозначением i80x86 будем понимать любые 32-разрядные микропроцессоры, име-

ющие основной набор команд такой же, как и в первом 32-разрядном микропро-

цессоре Intel 80386, и те же архитектурные решения, что и в микропроцессорах

фирмы Intel. Нас не будут интересовать новые наборы команд типа ММХ или SSE,

не будем мы касаться и архитектурных особенностей микропроцессоров, повыша-

ющих их производительность. Мы опишем только те механизмы, которые позво-

ляют организовать мультипрограммный и мультизадачный режимы, виртуальную

память, обеспечить надежные вычисления.

Реальный и защищенный режимы

работы процессора

Широко известно, что первым микропроцессором, на базе которого был создан

персональный компьютер IBM PC, был Intel 8088. Этот микропроцессор отличал-

ся от первого 16-разрядного микропроцессора фирмы Intel (микропроцессора

"°6), прежде всего, тем, что у него была 8-разрядная шина данных, а не 16-разряд-

Ная

(как у 8086). Оба этих микропроцессора предназначались для создания вы-

102 Глава 4. Особенности архитектуры микропроцессоров i80x86

числительных устройств, работающих в однозадачном режиме, то есть специаль-

ных аппаратных средств для поддержки надежных и эффективных мультипрог-

раммных операционных систем в них не было.

Однако к тому времени, когда разработчики осознали необходимость включения

специальной аппаратной поддержки мультипрограммных вычислений, уже было

создано очень много программных продуктов. Поэтому для совместимости с пер-

выми компьютерами в последующих версиях микропроцессоров была реализова-

на возможность использовать их в двух режимах: реальном (real mode) — так на-

звали режим работы первых 16-разрядных микропроцессоров — и защищенном

(protected mode), означающем, что параллельные вычисления могут быть защи-

щены аппаратно-программными механизмами.

Подробно рассматривать архитектуру первых 16-разрядных микропроцессоров

i8086/i8088 мы не будем, поскольку этот материал должен изучаться в других

дисциплинах. Итак, мы исходим из того, что читатель знаком с архитектурой про-

цессора i8086/i8088 и с программированием на ассемблере для этих 16-разряд-

ных процессоров Intel. Для тех же, кто с ней незнаком, можно рекомендовать,

например, такие книги, как [12, 24, 40] и многие другие. Однако мы напомним,

что в этих микропроцессорах (а значит, и в остальных микропроцессорах семей-

ства i80x86 при работе их в реальном режиме) обращение к памяти с возможным

адресным пространством в 1 Мбайт осуществляется посредством механизма сег-

ментной адресации (рис. 4.1). Этот механизм был использован для того, чтобы

увеличить с 16 до 20 количество разрядов, участвующих в формировании адреса

ячейки памяти, по которому идет обращение, и тем самым увеличить доступный

объем памяти.

Значение регистра CS

0 0 0 0

15 0

Регистр IP

15 0

Физический адрес | | |

19 0

Рис. 4.1. Схема определения физического адреса для процессора 8086

Для конкретности будем рассматривать определение адреса команд, хотя для ад-

ресации операндов используется аналогичный механизм, только участвуют в этом

случае другие сегментные регистры. Напомним, что для определения физическо-

го адреса команды содержимое регистра сегмента кода (Code Segment, CS) умно-

жается на 16 за счет добавления справа (к младшим битам) четырех нулей, после

чего к полученному значению прибавляется содержимое регистра указателя ко-

Новые системные регистры микропроцессоров J80x86

103

манд (Instruction Pointer, IP). Получается 20-разрядное значение

1

, которое и по-

зволяет указать любой байт из 20

20

.

В защищенном режиме работы определение физического адреса осуществля-

ется совершенно иначе. Прежде всего, используется сегментный механизм для

организации виртуальной памяти. При этом адреса задаются 32-разрядными

значениями. Кроме этого, возможна страничная трансляция адресов, также с

32-разрядными значениями. Наконец, при работе в защищенном режиме, ко-

торый по умолчанию предполагает 32-разрядный код, возможно исполнение

двоичных программ, созданных для работы микропроцессора в 16-разрядном

режиме. Для этого введен режим виртуальной 16-разрядной машины, и 20-раз-

рядные адреса реального режима транслируются с помощью страничного ме-

ханизма в 32-разрядные значения защищенного режима. Наконец, есть еще один

режим — 16-разрядный защищенный, позволяющий 32-разрядным микропро-

цессорам выполнять защищенный 16-разрядный код, который был характерен

для микропроцессора 80286. Правда, следует отметить, что этот последний ре-

жим практически не используется, поскольку программ, созданных для него,

не так уж и много.

Для изучения этих возможностей рассмотрим сначала новые архитектурные воз-

можности микропроцессоров i80x86.

Новые системные регистры

микропроцессоров i80x86

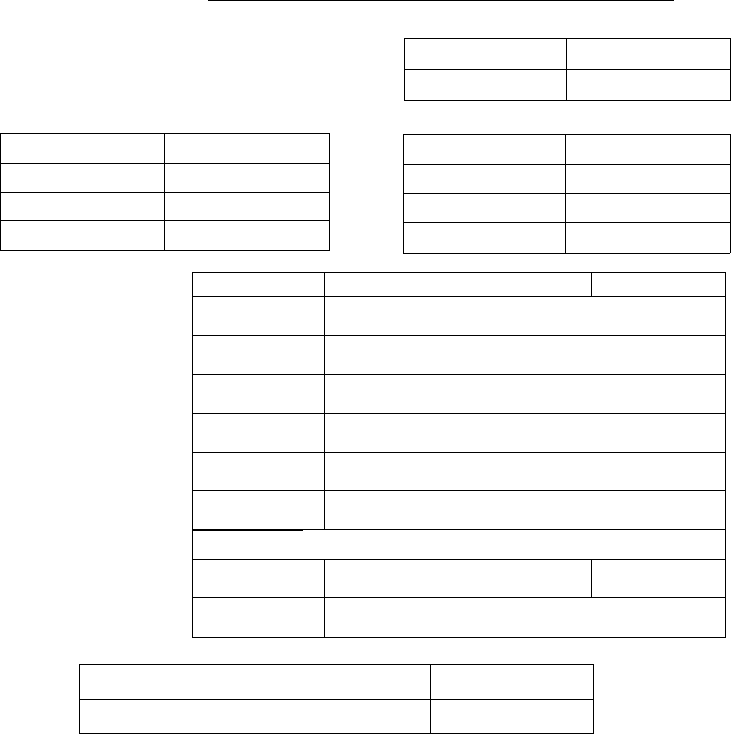

Основные регистры микропроцессора i80x86, знание которых необходимо для по-

нимания защищенного режима работы, приведены на рис. 4.2. На этом рисунке

следует обратить внимание на следующее:

• указатель команды (EIP) — это 32-разрядный регистр, младшие 16 разрядов

которого представляют регистр IP;

• регистр флагов (EFLAGS) — это 32-разрядный регистр, младшие 16 разрядов

которого представляют регистр FLAGS;

Q регистры общего назначения ЕАХ, ЕВХ, ЕСХ, EDX, а также регистры ESP, EBP,

ESI, EDI 32-разрядные, однако их младшие 16 разрядов представляют собой

известные регистры АХ, ВХ, CX.DX, SP, BP, SI, DI;

Q сегментные регистры CS, SS, DS, ES, FS, GS 16-разрядные, при каждом из них

пунктиром изображены скрытые от программистов (недоступные никому, кроме

собственно микропроцессора) 64-разрядные регистры, в которые загружаются

Дескрипторы соответствующих сегментов;

На самом деле, поскольку происходит именно сложение и каждое из слагаемых может иметь значе-

ние в интервале от нуля до 2'

с

' - 1 = 65 535 = 64 Кбайт, мы можем указать адрес начала сегмента, рав-

нин FFFFFFFF00H, и к нему прибавить смещение FFFFFFFFH. В этом случае мы получим пере-

полнение разрядной сетки, но для современных 32-разрядных процессоров (и для уже забытого

1о0286) имеется возможность указать первые 64 Кбайт выше первого мегабайта.

104

Глава 4. Особенности архитектуры микропроцессоров i80x86

31

15

EIP

EFLAGS

IP

FLAGS

15

31

16

ЕАХ

ЕВХ

ЕСХ

EDX

АХ

ВХ

СХ

DX

CS

SS

DS

ES

FS

GS

LDTR

TR

ESP

ЕВР

ESI

EDI

SP

ВР

SI

DI

63

Права доступа

48,

47

15

Базовый адрес ; Длина сегмента

16* 0

GDTR

IDTR

Базовый адрес

47 16

Длина сегмента

0

CR3

CR2

CR1

CR0

Рис. 4.2. Основные системные регистры микропроцессоров i80x86

при 16-разрядном регистре-указателе на локальную таблицу дескрипторов (Lo-

cal Descriptor Table Register, LDTR) также имеется «теневой» (скрытый от про-

граммиста) 64-разрядный регистр, в который микропроцессор заносит дескрип-

тор, указывающий на таблицу дескрипторов сегментов задачи, описывающих

ее локальное виртуальное адресное пространство;

16-разрядный регистр задачи (Task Register, TR) указывает на дескриптор в гло-

бальной таблице дескрипторов, который позволяет получить доступ к дескрип-

Адресация в 32-разрядных микропроцессорах i80x86

105

тору сегмента состояния задачи (Task State Segment, TSS) — информацион-

ной структуре, которую поддерживает микропроцессор для управления зада-

чами;

р 48-разрядный регистр GDTR (Global Descriptor Table Register) глобальной таб-

лицы дескрипторов (Global Descriptor Table, GDT) содержит как дескрипторы

общих сегментов, так и специальные системные дескрипторы, в частности,

в GDT находятся дескрипторы, с помощью которых можно получить доступ

к сегментам TSS;

• 48-разрядный регистр таблицы дескрипторов прерываний (IDTR) содержит

информацию, необходимую для доступа к таблице прерываний (IDT);

О 32-разрядные регистры CR0-CR3 являются управляющими.

Помимо перечисленных имеются и некоторые другие регистры.

Управляющий регистр CRO содержит целый ряд флагов, которые определяют ре-

жимы работы микропроцессора. Подробности об этих флагах можно найти, на-

пример, в [1, 8, 20]. Мы же просто ограничимся тем фактом, что самый младший

бит РЕ (Protect Enable) этого регистра определяет режим работы процессора. При

РЕ = О процессор функционирует в реальном режиме работы, а при единичном

значении микропроцессор переключается в защищенный режим. Самый старший

бит регистра CR0 — бит PG (PaGing) — определяет, включен (PG =1) или нет

(PG = 0) режим страничного преобразования адресов.

Регистр CR2 предназначен для размещения в нем адреса подпрограммы обработ-

ки страничного исключения, то есть в случае страничного механизма отображения

памяти обращение к отсутствующей странице будет вызывать переход на соот-

ветствующую подпрограмму диспетчера памяти, и для определения этой подпро-

граммы потребуется регистр CR2.

Регистр CR3 содержит номер физической страницы, в которой располагается таб-

лица каталога таблиц страниц текущей задачи. Очевидно, что, приписав к этому

номеру нули, мы попадем на начало этой страницы.

Адресация в 32-разрядных

микропроцессорах i80x86 при работе

в защищенном режиме

Поддержка сегментного способа организации

виртуальной памяти

Как мы уже знаем, для организации эффективной и надежной работы вычис-

лительной системы в мультипрограммном режиме необходимо иметь соответ-

ствующие аппаратные механизмы, поддерживающие независимость адресных

пространств каждой задачи и в то же время позволяющие организовать обмен

Данными и разделение кода. Для этого желательно выполнить следующие два

требования:

106 Глава 4, Особенности архитектуры микропроцессоров J80x86

• чтобы у каждого вычислительного процесса было собственное (личное, локаль-

ное) адресное пространство, никак не пересекающееся с адресными простран-

ствами других процессов;

• чтобы существовало общее (разделяемое) адресное пространство.

Для удовлетворения этих требований в микропроцессорах i80x86 реализован сегмен-

тный способ распределения памяти. Помимо того в этих микропроцессорах может

быть задействована и страничная трансляция. Поскольку для каждого сегмента ну-

жен дескриптор, устройство управления памятью поддерживает соответствующую

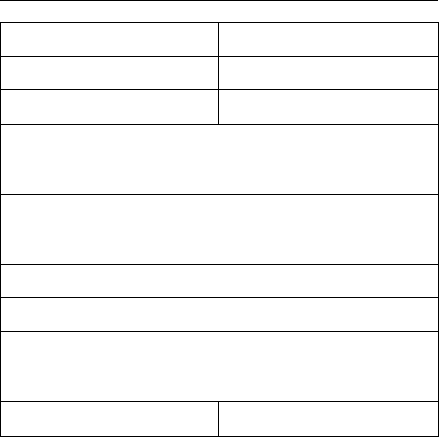

информационную структуру. Формат дескриптора сегмента приведен на рис. 4.3.

Старшее двойное слово дескриптора

31 23 19 15 11 7

База сегмента

(биты 31-24)

G D

0

0

Биты 19-16

поля Limit

Базовый адрес сегмента (биты 15-0)

Р

DPL S

Туре

А

Байт прав доступа

Биты 23-16

базы сегмента

Размер (предел - limit) сегмента

(биты 15-0)

31 15 О

Первое (младшее) двойное слово дескриптора

Рис. 4.3. Дескриптор сегмента

Поля дескриптора (базовый адрес, поле предела) размещены в дескрипторе не не-

прерывно, а в разбивку, потому что, во-первых, разработчики постарались мини-

мизировать количество перекрестных соединений в полупроводниковой структуре

микропроцессора, а во-вторых, чтобы обеспечить полную совместимость

1

микро-

процессоров (предыдущий микропроцессор i80286 работал с 16-разрядным кодом

и тоже поддерживал сегментный механизм реализации виртуальной памяти). Не-

обходимо заметить, что формат дескриптора сегмента, изображенный на рис. 4.3,

справедлив только для случая нахождения соответствующего сегмента в опера-

тивной памяти. Если же бит присутствия в поле прав доступа равен нулю (сегмент

отсутствует в памяти), то все биты, за исключением поля прав доступа, считаются

неопределенными и могут использоваться системными программистами (для ука-

зания адреса сегмента во внешней памяти) произвольным образом.

Локальное адресное пространство задачи определяется через таблицу LDT (Local

Descriptor Table). У каждой задачи может быть свое локальное адресное простран-

ство. Общее, или глобальное, адресное пространство определяется через таблицу GDT

(Global Descriptor Table). Само собой, что работу с этими таблицами (их заполнение

и последующую модификацию) должна осуществлять операционная система. Дос-

туп к таблицам LDT и GDT со стороны прикладных задач должен быть исключен.

При переключении микропроцессора в защищенный режим он начинает совершен-

но другим образом, чем в реальном режиме, вычислять физические адреса команд и

' Естественно, совместимость обеспечена только «снизу вверх», то есть программы, разработанные

для предыдущих версий микропроцессора, должны выполняться на последующих без какой-либо

переделки.

Адресация в 32-разрядных микропроцессорах J80x86 107

перандов. Прежде всего, содержимое сегментных регистров начинает интерпрети-

роваться иначе: считается, что там содержится не адрес начала, а номер соответству-

ющего сегмента. Для того чтобы подчеркнуть этот факт, сегментные регистры CS,

с$ DS, ES, FS, GS начинают даже называть иначе — селекторами сегментов. При

этом каждый селекторный регистр разбивается на три поля (рис. 4.4).

р Поле индекса (Index) — старшие 13 битов (3-15) определяет собственно номер

сегмента (его индекс в соответствующей таблице дескрипторов).

• Поле индикатора таблицы сегментов (Table Index, TI) — бит с номером 2 опре-

деляет часть виртуального адресного пространства (общее или принадлежащее

только данной задаче). Если TI = 0, то поле индекса указывает на элемент в

глобальной таблице дескрипторов (GDT), то есть идет обращение к общей па-

мяти. Если TI = 1, то идет обращение к локальной области памяти текущей за-

дачи; это пространство описывается локальной таблицей дескрипторов (LDT).

• Поле уровня привилегий идентифицирует запрашиваемый уровень привилегий

(Requested Privilege Level, RPL).

15 !

Поле индекса (номер дескриптора)

TI RPL

Рис. 4.4. Селектор сегмента

Операционная система в процессе своего запуска инициализирует многие регист-

ры, и прежде всего GDTR. Этот регистр содержит начальный адрес глобальной

таблицы дескрипторов (GDT) и ее размер. Как мы уже знаем, в GDT содержатся

дескрипторы глобальных сегментов и системные дескрипторы.

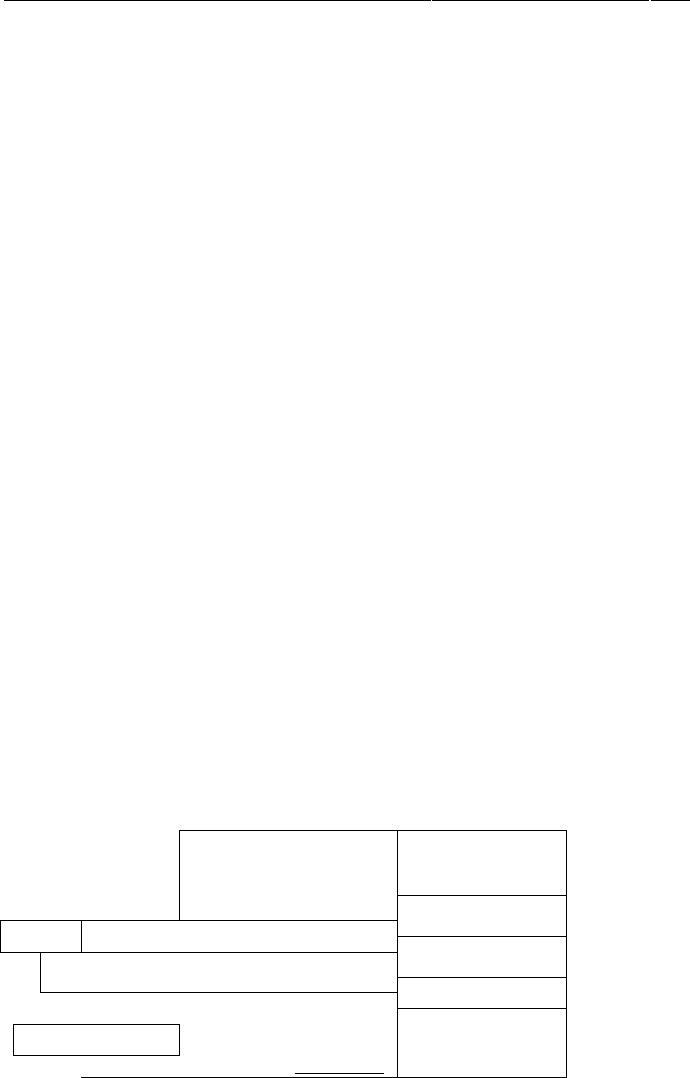

Для манипулирования задачами операционные системы поддерживают информаци-

онную структуру, которую мы уже раньше называли как дескриптор задачи (см. гла-

ву 1). Микропроцессоры с архитектурой IA32 поддерживают работу с наиболее важной

частью дескриптора задачи, которая меньше всего зависит от операционной системы.

Эта инвариантная часть дескриптора, с которой и работает микропроцессор, названа

сегментом, состояния задачи (Task State Segment, TSS). Перечень полей TSS показан

на рис. 4.5. Видно, что этот сегмент содержит в основном контекст задачи. Процессор

получает доступ к этой структуре с помощью регистра задачи (Task Register, TR).

Регистр TR содержит индекс (селектор) элемента в GDT. Этот элемент представ-

ляет собой дескриптор сегмента TSS. Дескриптор заносится в теневую часть реги-

стра (см. рис. 4.2). К рассмотрению TSS мы еще вернемся, а сейчас заметим, что

в одном из полей TSS содержится указатель (селектор) на локальную таблицу де-

скрипторов данной задачи. При переходе процессора с одной задачи на другую

содержимое поля LDTR заносится микропроцессором в одноименный регистр.

Инициализировать регистр TR можно и явным образом.

Итак, регистр LDTR содержит селектор, указывающий на один из дескрипторов

таблицы GDT. Этот дескриптор заносится микропроцессором в теневую часть ре-

гистра LDTR и описывает таблицу LDT для текущей задачи. Теперь, когда у нас

108

Глава 4. Особенности архитектуры микропроцессоров J80x86

определены как глобальная, так и локальная таблица дескрипторов, можно рас-

смотреть процесс определения линейного адреса

1

. Для примера рассмотрим про-

цесс получения адреса команды. Адреса операндов определяются по аналогии, но

задействованы будут другие регистры.

Поля, определяемые ОС

(их количество и состав

может быть любым)

31 16

Адрес карты ввода/вывода

15 0

LTDR

Сегментные регистры ES, CS, SS, DS, FS, GS

(на каждый регистр отведено по 4 байт,

из которых используется только 2 младших)

Общие регистры (ЕАХ, ЕСХ, EDX, EBX, ESX,

EBP, ESI, EDI)

Регистр флагов EFLAGS

Указатель команд (регистр EIP)

Привилегированные указатели стеков

Link

Л

68п

60h

48h

28h

24h

20h

4

0

Рис. 4.5. Сегмент состояния задачи

Собственно TSS

(108 байт)

J

Микропроцессор анализирует бит TI селектора кода и, в зависимости от его значе-

ния, извлекает из таблицы GDT или LDT дескриптор сегмента кода с номером

(индексом), который равен полю индекса (биты 3-15 селектора на рис. 4.4). Этот

дескриптор заносится в теневую (скрытую) часть регистра CS. Далее микропро-

цессор сравнивает значение регистра EIP (Extended Instruction Pointer — расши-

ренный указатель команды) с полем размера сегмента, содержащегося в извлечен-

ном дескрипторе, и если смещение относительно начала сегмента не превышает

размера предела, то значение EIP прибавляется к значению поля начала сегмента,

и мы получаем искомый линейный адрес команды. Линейный адрес — это одна из

форм виртуального адреса. Исходный двоичный виртуальный адрес, вычисляе-

В микропроцессорах 180x86 линейным называется адрес, полученный в результате преобразования

виртуального адреса формата (S, d) в 32-разрядный адрес.

Адресация в 32-разрядных микропроцессорах i80x86 109

мый в соответствии с используемой схемой адресации, преобразуется в линейный.

В свою очередь, линейный адрес будет либо равен физическому (если страничное

преобразование отключено), либо путем страничной трансляции преобразуется

физический адрес. Если же смещение из регистра EIP превышает размер сегмен-

та кода, то эта аварийная ситуация вызывает прерывание, и управление должно

передаваться супервизору операционной системы.

Регистр EIP

CS

Искомая команда

Сегмент

кода

Адрес сегмента

!<•

Дескриптор

> LDT

LTDR

Адрес LDT |

i

GDTR (адрес GDT)

1

К-

1 '

•

Дескриптор

GDT

Рис. 4.6. Процесс получения линейного адреса команды

110 Глава 4, Особенности архитектуры микропроцессоров J80x86

Рассмотренный нами процесс получения линейного адреса иллюстрирует рис. 4.6.

Стоит отметить, что поскольку межсегментные переходы происходят нечасто,

то, как правило, определение линейного адреса заключается только в сравнении

значения EIP с полем предела сегмента и в прибавлении смещения к началу сег-

мента. Все необходимые данные уже находятся в микропроцессоре, и операция

получения линейного адреса происходит очень быстро.

Итак, линейный адрес может считаться физическим адресом, если не включен ре-

жим страничной трансляции адресов. К сожалению, аппаратных средств микро-

процессора для поддержки рассмотренного способа двойной трансляции виртуаль-

ных адресов в физические явно недостаточно. При наличии большого количества

небольших сегментов, из которых состоят программы, это приводит к заметному

замедлению в работе процессора. В самом деле, теневой регистр при каждом се-

лекторе имеется в единственном экземпляре, и при переходе на другой сегмент

требуется вновь находить и извлекать соответствующий дескриптор сегмента, а. это

отнимает время. Страничный же способ трансляции виртуальных адресов, как мы

знаем, имеет немало достоинств. Поэтому в защищенном режиме работы, при ко-

тором всегда действует описанный выше механизм определения линейных адре-

сов, может быть включен еще и страничный механизм.

Поддержка страничного способа организации

виртуальной памяти

При создании микропроцессора i80386 разработчики столкнулись с очень серьез-

ной проблемой в реализации страничного механизма. Дело в том, что микропро-

цессор имел широкую шину адреса (32 бит), и возник вопрос о разбиении всего

адреса на поле страницы и поле индекса. Если большое количество битов адреса

отвести под индекс, то страницы станут очень большими, что повлечет значитель-

ные потери и на фрагментацию, и на операции ввода-вывода, связанные с замеще-

нием страниц. Хотя количество страниц стало бы при этом меньше, и накладные

расходы на их поддержание тоже уменьшились бы. Если же размер страницы умень-

шить, то большое поле номера страницы привело бы к потенциально громадному

количеству страниц, и пришлось бы либо вводить какие-то механизмы контроля

за номерами страниц (с тем, чтобы они не выходили за размеры таблицы страниц),

либо создавать эти таблицы максимального размера. Разработчики пошли по пути,

при котором размер страницы выбран небольшим (2

12

= 4096 = 4 Кбайт), а поле

номера страницы величиной в 20 бит, в свою очередь, разбивается на два поля и

осуществляется двухэтапная страничная трансляция.

Для описания каждой страницы создается соответствующий дескриптор. Длина

дескриптора выбрана равной 32 бит: 20 бит линейного адреса определяют номер

страницы (по существу — ее адрес, поскольку добавление к нему 12 нулей при-

водит к определению начального адреса страницы), а остальные биты разбиты

на поля, показанные на рис. 4.7. Как видно, три бита дескриптора зарезервирова-

но для использования системными программистами при разработке подсистемы

организации виртуальной памяти. С этими битами микропроцессор сам не рабо-

тает.