Ситкевич Т.А., Сюрин В.Н. Параллельные вычислительные среды

Подождите немного. Документ загружается.

61

ва ться для обработки процессором или для выборки на как ое-

либо устройство (рис. 3.9). В структ урах третьего типа («к анал –

системный к онтроллер») предусма тривается центральный узел

коммутации: все передачи данных к периферийным устройст-

вам, центральным процессорам и главной памяти, а также все

передачи данных от них осуществляются через и по д управле-

нием системног о контроллера (рис. 3.10).

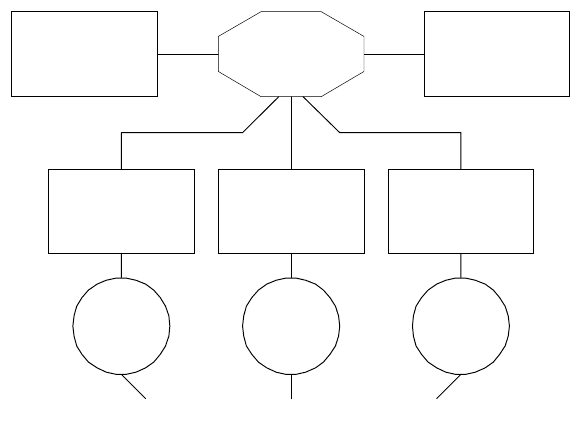

Рис. 3.8. Структура межпроцессорной связи

«Канал – центральный процессор»

В конкретных вычислительных системах устройства, име-

ющие одинаковые ф ункции, могут от лича ться с то чки зрения

деталей их функционирования, а также в названиях. На рис. 3.8-

3.10 изображены основные типы структур без каких-либо их

деталей. В большинстве традиционных систем, в особенности

однопроце ссорных, каналы ввода-вывода подключены

непосредственно к центральному процессору, при этом основ-

ная память часто конструктивно совмещается с процессором.

На рис унке 3.8 представлена струк т ура с непосредственным

Основная память

Центральный

процессор

Контроллер

ввода-вывода

Контроллер

ввода-вывода

Контроллер

ввода-вывода

Периферийные устро йства

Системный

контроллер

62

по дключением трех независимых каналов к центрально му про-

цессору, с ко т орым констр уктивно совмещена основная память.

Основным достоинство м та кого типа структ уры является то, чт о

требу ется наименьшее количество оборудования, и что стоимость

оказыв ается также наименьшей. Системы со структ урой «канал

– центральный процессор» наиболее целесообразно применять

в тех случаях, когда требов ания к ресурсам систем до лжны или

могут быть определены заранее и когда они не меняются в дина-

мик е работы. Эт о определяется тем обстоятельств о м, что все

функции по управлению сосредот о чены в процессоре (данные

поступают в основную память и из основной памяти под управ-

лением программы, выполняемой центральным процессором).

Основной об ластью применения систем, в которых каналы под-

клю чены к центральному процессору, является пакетная обра-

ботк а, ко т орая в насто ящее время занимает главное место при

использовании вычислительных машин.

Основным недоста тком струк т уры «канал – центральный

процессор» является требование повышенной производитель-

ности цент рального проце ссора, которое вытекает из

необходимости быстрой обработки случайного поток а преры-

ваний. Этот не достаток вле чет неско лько др угих недостатков.

Имеет место жестк ое ограничение на число по дключаемых ка-

налов с точки зрения их эффективног о использов ания, особен-

но при одновременной работе, так как при большом числе к ана-

лов процессор большую часть времени затрачив ает на обслужи-

вание прерываний, связанных с вводо м и выводо м. Кроме это-

го, при обработк е со сложным взаимодействием процессов и

при работе систем с вирту альной памятью типичным является

поло ж ение, когда возник ает большое число непланируемых за п-

росов на вво д-выво д. В этих условиях при использов ании сис-

тем с по дключением каналов к центральному процессору необ-

ходим а такая операционная система, к о т орая бы к о мпенси-ро-

вала недостатки струк туры. Наконец, ограничение на число ка-

налов приво дит, естественно, к ограничению числа обслу жив а-

емых периферийных устройств. Проблем а ограничений на чис-

ло каналов и на число периферийных устройств может быть

решена во многих случаях путем введения под к аналов или пу-

тем совместного использования каналов. Для повышения ск о-

63

рости обработки и пропускной способности системы требу ется

более тща тельное и квалифицированное программирование и

обоснованное распре деление приоритетов между периферий-

ными устройствами.

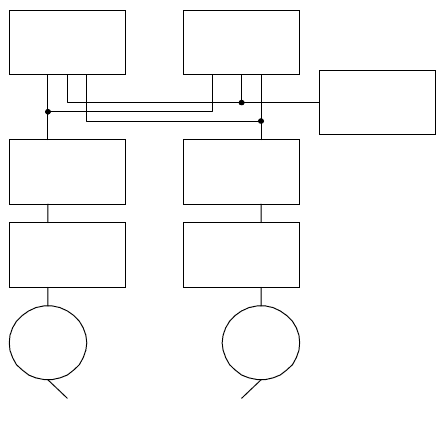

Рассмотрим структуру типа «канал – основная память» (рис.

3.9). В этом случае имеется прямой независимый доступ к ос-

новной памяти, которая реализуетс я конструктивно как от-

дельное устройство в виде дв ух или бо лее компонент вычисли-

тельной системы. За пись данных в основную память и с читыв а-

ние их из нее осуществляю тся, логически и физически, без не-

посредственног о в мешательств а центральног о процессора. Все

основные части системы, осуществляющие обработку и пере-

да чу информации (центральные процессоры, процессоры вво-

да-вывода и к онтроллеры вво да-выв ода), представляют собой

устройства, подключенные к соответств ующим вх одам моду лей

основной памяти. Они рабо тают независимо друг от др уга. Эти

устройства, с одной стороны, имеют дело с о тдельными вх ода-

ми основной памяти, а с друг ой стороны, – с периферийными

устройствами.

Модуль основной

памяти

Модуль основной

памяти

Центральный

процессор

Процессор

ввода-вывода

Процессор

ввода-вывода

Контроллер

ввода-вывода

Контроллер

ввода-вывода

Периферийные устройства

Рис. 3.9. Структура связи «Канал – основная память»

64

Главным достоинство м данной структ уры является о дновре-

менность операций вво да-выво да и вычислений благодаря неза-

висимому доступу к основной памяти. Разделение ввода-выво-

да и вычислений позв оляет не только ув еличить число каналов,

с которыми мо жет работа ть система, но и разгру жает централь-

ный процессор от большог о числа прерываний. Вследствие та-

кой независимости операций вво да-вывода и вычислений рас-

сматриваемая струк т ура наилучшим образо м о тве чает требов а-

ниям обработки со сложным взаимо действием процессов.

Системы со структ урой «канал – основная память» об лада-

ют гораз до боль-шей гибкостью по сравнению с системами со

структурой «канал – центральный процессор». Наращивание

первых для уве-личения их мощ-ности достигается простым до-

бавлением ком-понент ов систем, при это м отпадает необ х о ди-

мость в сложных завязках. На при-мер, для увеличения вычисли-

тельной мощности обычно добавляется центральный процес-

сор, к о торый по дклю чается к одному из входов основной памя-

ти. В таких случаях ограничения могут быть вызваны только

возможностями операционной системы по управлению

получаемыми двух- или мног опроцессорными системами.

Т аким образ о м, структура типа «канал — основная память»

позволяет иметь большое число дополнительных вх о дов памя-

ти, независимых контроллеров ввода-вывода, процессоров вво-

да-выво да и других устройств. Все эти устройства, расширяя воз-

можности системы, и, в частности, увеличивая ее гибкость, зна-

чительно увеличивают ст оимость системы. Так, например, каж-

дый вх о д памяти должен иметь свой собственный интерфейс и

управляющую логику, а процессор или контроллер вво да-выво -

да — иметь интерфейс для обеспе чения работы канала. Поэто-

му дополнительные каналы повышают гибк ость системы, но и

приво дят к высок ой стоимости системы. Число входов памяти

мож ет быть достаточно большим, о днако сле ду ет учитыва ть, что

центральный процессор полностью занимает вход памяти или

разделяет его с ограниченным числом периферийных устройств.

Например, если к аждый модуль памяти в системе имеет четыре

вх о да, то о дин из входов закрепляется за центральным процес-

соро м. Три оставших ся входа обычно предостав ляю тся для ра-

боты с дисками, лентами и низкоскоростными устройствами

65

соответственно. В многопроцессорной системе, в которой каж-

дый мо дуль памяти имеет, например, четыре входа, два входа

выделяются центральным процессорам, а периферийные уст-

ройства должны совместно разделять два оставшихся вх ода.

М о жно сохранить достоинств а стр укт уры с многовхо довой па-

мятью и обеспечить при это м низк ую стоимость системы, если

использов а ть мультиплексор. М уль типлексоры могут быть не-

посредственно подключены ко вход у памяти, чтобы обеспечить

подключение дополнительных процессоров ввода-вывода и

контроллеров вво да-вывода, или же они могут быть по дклю че-

ны к процессорам ввода-вывода и контро ллерам ввода-вывода,

чтобы обеспечить подключение дополнительных каналов вво-

да-выв ода. Имеющиеся большие потенциальные возможности

по организации работы множества каналов вво да-вывода не

могут быть испо льзов аны из-за необ хо димости предоставления

входов памяти в исключительное пользование центральным

процессорам, причем, о чевидно, чем бо льше центральных про-

цессоров в системе, тем большее число вх одов основной памя-

ти они занимают. Поэтому нередко каналам предоставляется

то лько один или дв а остающихся вх о да памяти и, следователь-

но, системы со струк турой «к анал – основная память» в это м

случае обеспечив аю т по существу те же возмо жности по обслу-

живанию каналов, что и системы с традиционной стр уктурой

«канал – центральный процессор». Существую т системы со

структ урой, которая мо жет рассматрива ться как вариант струк-

туры «канал – центральная память». Такие системы имеют дв а

центральных процессора, один из к о торых выполняет все функ-

ции вво да-выво да, а друг ой – все функции по реализации вы-

числений. Ясно, что такой подхо д представляет собой весьма

дорог остоящий путь организации вычислительных систем.

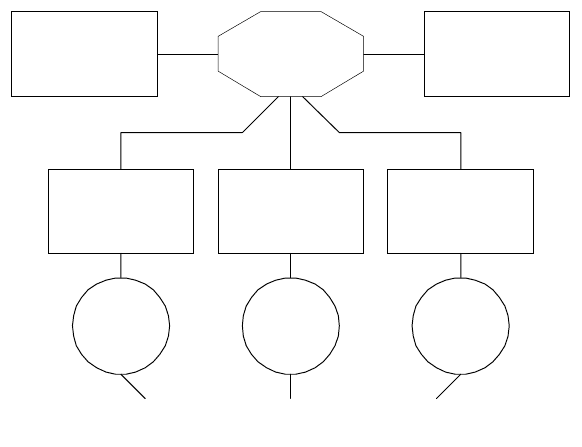

Перейдем к системам со струк-т урой «к анал – системный

контроллер» (рис. 3.10). В систем ах такого типа центральным

вх о до м для каналов вво да-выв о да, центральных процессоров и

мо дулей основной памяти служит системный контроллер, кото-

рый управляет доступо м к основной памяти, как от каналов вво-

да-выв ода, так и от центрального процессора. Этот контроллер

является логическим связывающим звеном между основной

памятью и центральным процессоро м и выполняет ф ункции

66

регулирования пот оков информации в системе. Рассма трив ае-

мая струк тура имеет сходство со структурой «к анал – основная

память» в том смысле, что в обоих случаях доступ к основной

памяти со стороны каналов осуществляется без вмеша тельств а

центральног о процессора. Вместе с тем системный контроллер

обеспечивает доступ к основной памяти подобно тому, как это

делает центральный процессор в системах со структ урой «ка-

нал – центральный процессор», т.е. структура «канал – систем-

ный контро ллер» с этой то чки зрения по добна структуре «канал

– центральный процессор».

Таким образо м, струк тура «канал – системный контроллер»

соединяет в себе особенности структур «канал – центральный

процессор» и «к анал – основная память». При это м, однак о, си-

стемный контроллер пре дставляет собой самосто ятельное фун-

кциональное устройство, к от орое при правильном применении

мож ет обеспечить в системе сочетание достоинств дв ух после-

дних струк т ур.

Рис.3.10. Структура связи “Канал – системный контроллер”.

Основная память

Центральный

процессор

Контроллер

ввода-вывода

Контроллер

ввода-вывода

Контроллер

ввода-вывода

Перифе рийные устройства

Системный

контроллер

67

Основное достоинство струк туры «канал – системный к онт-

роллер» заключается в логическ ой коор динации всех систем-

ных действий. Центральный процессор имеет все возмо жности

для выполнения вычислений, в то время как контроллер осущест-

вляет жесткое управление системой. Одна из проблем, ко т орая

возник ает для струк туры «канал – центральный процессор», со-

стоит в том, что треб уется постоянно взаимодействов а ть с ка-

налами и, как следствие, обслужив а ть с привле чением процес-

сора большое число прерываний. Эти прерывания возникаю т в

произвольные моменты времени, и их влияние на пропускную

способность системы мо жет быть самым различным. С друго й

стороны, в структ уре «канал – основная память» имеются скры-

тые потери, связанные с пост о янным опросом со стороны цент-

рального процессора о то м, что произошло в те чение последне-

го цикла его работы.

Системный контроллер не имеет отмеченных выше

недостатков. Он освобо ждает центральный процессор от дей-

ствий по низкоприоритетным вво дам и выво дам инфор мации и

в то же время обеспечив ает посто янную гот овность централь-

ного процессора к обработке прерываний. Поско льку систем-

ный к онтроллер может устранить недостатки, обсуждавшиеся

выше, струк тура с системным контроллеро м мож ет счита ться

эффективной для выполнения как локальных вычислений, так и

вычислений со сложным взаимо действием. Ввиду того, чт о сто -

имость оборудования, составляющего системный к онтроллер,

б лизк а к стоимости центральног о процессора, то стоимость си-

стемы минимальной конфигурации б лизк а к стоимости дв ух-

процессорной системы. Кро ме этог о, алг оритм, управляющий

работ ой системног о контроллера, мож ет либо давать преиму-

щества вычислениям перед вводом-выводом, либо отнимать,

вследствие чего возникают трудности в балансировке работы

системы. Поэто му применение рассм а триваемой структуры в

ряде случаев мо жет оказа ться нерациональным, а эффективность

– сильно зависящей от характера решаемых зада ч. Существу ет

ряд систем, в к о торых использ ованы варианты структуры с сис-

темными контроллерами. В некоторых из таких систем эти кон-

троллеры выполняют функции общего интерфейса и управле-

ния доступом к памяти. В др угих системах они выполняют тольк о

68

функции ко ммутации и не обеспечив ают приоритетног о досту-

па к памяти, при этом все требования обслужив аются в порядк е

их поступления. Эти системы могут быть настроены как на пер-

воо чередное выпо лнение вычислений, так и на первоо чередное

выполнение ввода-вывода в зависимости от требований конк-

ретной области применения.

В наст о ящее время наметилась тенденция распре деленной

обработки при по мощи групп микропроцессоров. Микропро-

цессорные к о мпоненты системы, вероятно, не б удут крупными

фиксиров анными функциональными устройствами, явно отде-

лёнными друг от друга, такими как традиционные устройства

управления, арифметико-логические устройства и б локи ввода-

выво да. Вместо этог о они будут, по-видимо му, динамически пе-

рестраиваемыми элементами в целях решения нек о т орой зада-

чи обработки информации. Например, если данная программа

требует большого объема вычислений, то элементы пере-

страиваются в устройства обработки. Если же, наоборот, тре-

буется бо льшое число операций ввода-вывода, то они перестра-

иваются в устройства для вво да-выв о да. Уже построено неск о ль-

ко микропроцессорных систем с изменяемой стр укт урой. Они

занимают промежуто чное поло ж ение между системами боль-

шой и средней произво дительности. Будущие системы могут

быть построены из элемент ов, имеющих различные возможно-

сти – от ограниченных до самых широких. Распространению

таких систем б удет способствова ть просто та наращивания эле-

ментов, ко личество к о т орых б удет ограничено лишь возможно-

стями операционной системы по управлению этими элемента-

ми.

ПРИНЦИПЫ ПРОГРАММИРОВАНИЯ

В ПАРАЛЛЕЛЬНЫХ ВЫЧИСЛИТЕЛЬНЫХ СРЕДАХ

ПРОГРАММНОЕ ОБЕСПЕЧЕНИЕ ПВС

Программное об еспе чение вычислительной системы делит-

ся на две части: программное обеспе чение базовой машины и

программное обеспе чение системы, кот орая состоит из систе-

мы параллельного программирования (Р-программирования) и

управляющей системы . Программное обеспечение системы ха-

69

рактеризуется независимостью от числа электронных машин

(ЭМ) в системе, ф ункциональной идентичностью при реализа-

ции на любой ЭМ, изменяемостью мо дулей и наращиванием их

состава, возможностью использования вычислительной систе-

мы в режиме ко ллективног о дост упа. Основные зада чи управ-

ляющей системы – обеспе чение связи с внешним миром и раци-

ональное использов ание ресурсов системы. Г ибкость использ о-

вания ресурсов и универсальность применения вычислительных

систем достигаются вве дением режимов параллельной обработ-

ки, ав т оно мной работы машин, режима профилактики и режи-

ма диспетчера; иерархической структурой управляющей про-

граммы, состоящей из главного диспетчера, старших диспетче-

ров режимов ав т оно мной работы и параллельной обработки,

диспетчеров элементарных машин.

На систему Р-программирования возлагается зада ча обес-

пе чения достаточно широких возмо жностей при написании и

от ладке параллельных программ. В состав системы Р-програм-

мирования входят языки для записи параллельных алгоритмов,

получаемые путем расширения соответств ующих язык ов опе-

рат орами системных взаимо действий; трансляторы с языков,

позволяющие при ав тома тизации параллельного программиро-

вания использов а ть трансляторы базовой машины; сре дства от-

ладки Р-программ, анализирующие качество Р-программ и вы-

являющие ошибки взаимодействий Р-ветвей путем моделиро-

вания параллельного процесса на одной ЭМ; а также средства

специальной организации Р-программ, такие как:

сегментиров ание Р-ветвей с целью экономии опера тив-

ной памяти;

подго товк а высок онадежных вычислений, обеспечив а ю-

щих про до лж ение с чета при сбоях и выходе машин из строя;

средств а управ ления заданиями (языки директив), облег-

чающие пользов а телю реализацию различных видов работ: за-

пуск и снятие Р-программ, задание и уничтож ение Р-файлов,

задание графика рабо ты подсистем и т.д.

Особенности рабо ты вычислительной системы и ее про-

граммного об еспе чения в сильной мере опре деляю тся парамет-

рами ЭМ и, в частности, ее стоимостью. По мере удешев ления

ЭМ и в связи с развитием интегральной те хно логии становится

70

все бо лее реальным направление, основанное на построении

вычислительной системы из большог о числа простых и деше-

вых вычислительных мо дулей. Алг оритмы планирования об ес-

печиваю т разбиение системы на по дсистемы в соответствии с

поступающими задачами. Каждая така я подсистем а в течение

определенног о интервала времени работает в монопрограмно м

режиме, обслужив ая зада чи, ко т орые требу ю т для своей реали-

зации как раз ст олько ЭМ, ск о лько их имеется в наличии в по д-

системе. По истечении заданного промежутка времени проис-

ходит новое разбиение системы на подсистемы. Такая органи-

зация работы позво ляет получить э ффект, эквивалентный тому,

что в процессе функционирования основное число ЭМ ведет

непрерывный счет, а одна или неск о лько ЭМ заним аются обме-

ном с внешней памятью.

При работе простых ЭМ про яв ляется тенденция к упроще-

нию операционных систем. В это м случае ЭМ рассма тривается

как единица ресурса системы, которая работает в подсистеме в

монопрограммном режиме. Монопрограммный режим работы

ЭМ позволяет упростить работу операционной системы, не сни-

жая эффективность работы системы в цело м. В основ у постро-

ения простых и эффек тивных операционных систем для вычис-

лительных систем могут быть по ло жены принципы мо дульнос-

ти и иерархичности структуры, мног опрограммности ЭМ и под-

систем, адаптивности к внешним условиям, крупноб ло чности

при распараллеливании алгоритмов.

СТРУКТУРИЗАЦИЯ И ВЫПОЛНЕНИЕ

ПАРАЛЛЕЛЬНЫХ ПРОГРАММ

Все современные языки программиров ания обяза тельно не

то лько отражаю т, но и по дчеркиваю т иерархическ ую струк т уру

алгоритмов. Выделение, подчеркивание уровней иерархии, лек-

сико-графических уровней, реализация б лочного принципа –

така я струк т уризация программы не то лько служит естествен-

ному отражению реальног о процесса, но и по могает разобрать-

ся и проследить правильность выпо лнения алг оритма, упрос-

тить разработку, облегчить мо дифик ацию, обеспечить наг ляд-

ность и в большей мере реализова ть оптимальное планирова-

ние использования всех ресурсов ВС: процессоров, памяти всех