Рудякова А.Н., Липинский А.Ю., Данилов В.В., Рудяков И.Ю. Аппаратно-программные средства встраиваемых компьютерных систем

Подождите немного. Документ загружается.

Последовательные интерфейсы

251

высокий логический уровень, путем изменения уровня на линии SDA с

низкого к высокому уровню.

Если подчиненное устройство не успевает обработать входящие данные

в связи с необходимостью выполнения некоторых других функций, то ему

необходимо удержать линию SCL в низком состоянии для перевода ведущего

устройства в состояние ожидания.

Все пакеты данных, передаваемые по шине TWI, имеют

9-битный

формат: один байт данных и бит подтверждения. В процессе передачи

данных ведущее устройство генерирует синхроимпульсы и условия СТАРТ и

СТОП, а приемник отвечает за подтверждение принимаемых данных.

Подтверждение (ПОДТВ) выполняется приемником путем установления

низкого уровня на линии SDA во время 9-го периода синхронизации на

линии SCL. Если приемник оставляет линию SDA в

высоком состоянии, то

этим сигнализируется НЕТ ПОДТВ (нет подтверждения).

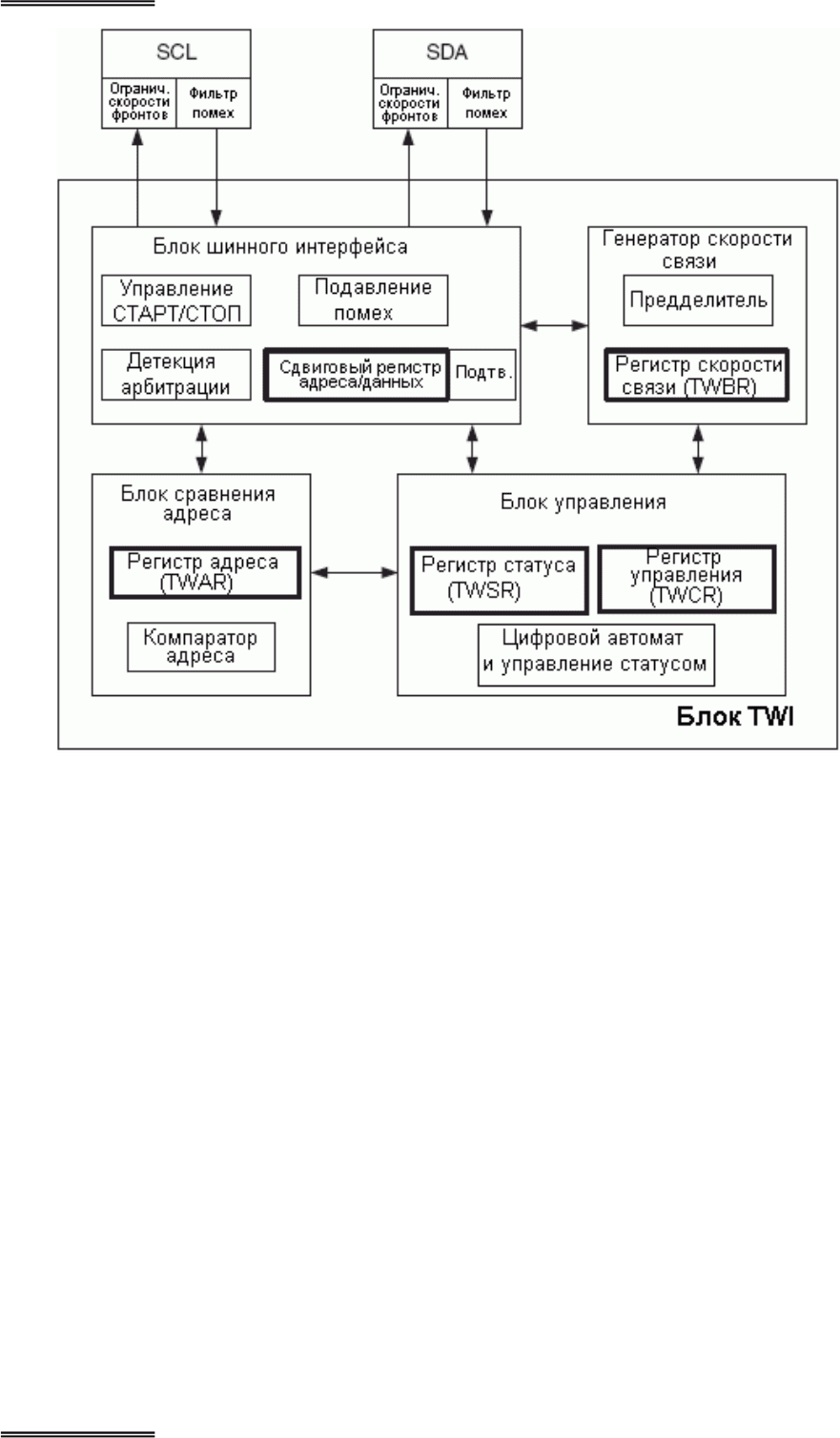

Модуль TWI микроконтроллера AVR состоит из нескольких подмодулей

(см. рис. 6.10). Все регистры, выделенные толстой линией, подключены к

встроенной шине данных микроконтроллера AVR.

Глава 6

252

Рис. 6.10

Набор предварительно заданных кодов статуса охватывает различные

состояния, в которых может находиться TWI при возникновении событий

TWI. Коды статуса разделяются на коды статуса ведущего устройства и коды

статуса подчиненного устройства, а затем на коды статуса приема и

передачи. Также существуют коды статуса для ошибочных ситуаций и для

состояния незанятости шины

.

Модуль TWI работает как цифровой автомат и управляется по событиям:

если за условием СТАРТ передается адрес, который совпадает с адресом,

хранящимся в регистре адреса подчиненного устройства (TWAR), то

устанавливается флаг TWINT и инициируется выполнение соответствующего

прерывания (при условии, что установлены биты глобального разрешения

Последовательные интерфейсы

253

прерываний и прерываний интерфейса TWI). Флаг TWINT также

устанавливается при возникновении и других событий интерфейса TWINT.

Программа подчиненного устройства реагирует на прерывания интерфейса

TWI путем считывания кода статуса и выполнения соответствующих

действий.

До тех пор, пока флаг TWINT установлен, линия SCL находится в

низком состоянии. Этим обеспечивается возможность прикладной программе

завершить все необходимые задачи перед продолжением

передачи.

Флаг TWINT устанавливается в следующих ситуациях:

- после передачи условия СТАРТ/ПОВТОРНЫЙ СТАРТ;

- после передачи ПОДЧИН_АДР + ЧТ/ЗП (подчиненный адрес и бит

чтения/записи);

- после передачи байта адреса;

- после потери арбитрации;

- после адресации TWI собственным подчиненным адресом или

глобальным вызовом;

- после приема байта данных;

- после приема условия СТОП

или ПОВТОРНЫЙ СТАРТ при

подчиненной адресации;

- при возникновении ошибки (некорректные условия СТАРТ или

СТОП).

Блок генератора скорости связи управляет периодом импульсов на

линии SCL в ведущем режиме работы. Период SCL управляется путем

установки регистра скорости связи TWI (TWBR) и бит предделителя в

регистре статуса TWI (TWSR). Работа подчиненного устройства зависит от

установок регистра скорости связи или

предделителя, однако частота

синхронизации ЦПУ подчиненного устройства должна быть минимум в 16

раз больше частоты SCL. Подчиненные устройства могут продлевать низкое

состояние SCL, тем самым, снижая среднее значение частоты синхронизации

шины TWI. Частота SCL генерируется в соответствии с выражением:

Глава 6

254

F

SCL

= F

ЦПУ

/[16+2(TWBR) · 4

TWPS

],

где TWBR - значение в регистре скорости связи TWI, TWPS - значение бит

предделителя в регистре статуса TWI.

Если TWI работает в ведущем режиме, то значение TWBR должно быть

не менее 10. Если значение TWBR меньше 10, то ведущее устройство шины

может генерировать некорректные сигналы на линиях SDA и SCL во время

передачи байта.

Биты TWPS находятся в регистре статуса TWISR вместе с битами

статуса

. Для простоты обработки бит статуса рекомендуется записывать

нулевые значения в TWPS. В этом случае, желаемая скорость связи

достигается путем варьирования значением в TWBR. В табл. 6.6 приведены

результаты вычислений значений TWBR для некоторых частот ЦПУ и SCL.

Таблица 6.6 –

Частоты ЦПУ и SCL в зависимости от установок регистра скорости связи

Частота ЦПУ,

МГц

TWBR TWPS

Частота SCL,

МГц

16 12 0 400

16 72 0 100

14.4 10 0 400

14.4 64 0 100

12 10 0 ~333

12 52 0 100

8 10 0 ~222

8 32 0 100

4 12 0 100

3.6 10 0 100

Последовательные интерфейсы

255

2 10 0 ~55

1 10 0 ~28

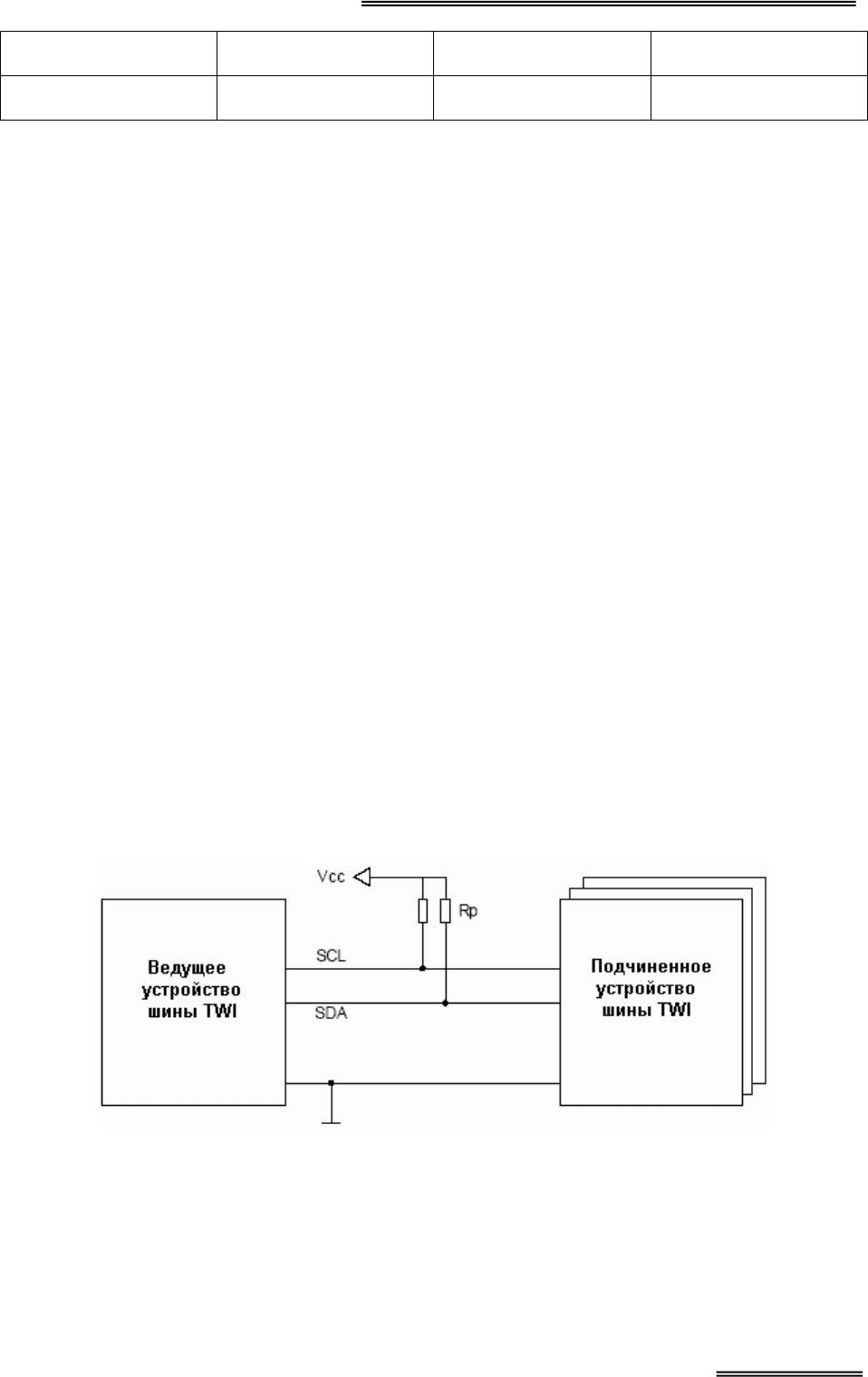

Обе линии TWI (SDA и SCL) являются двунаправленными, все выходы,

подключаемые к линиям шины TWI должны быть либо с открытым стоком,

либо с открытым коллектором. Каждая линия должна быть связана с линий

питания через подтягивающий резистор. В этом случае на линии

присутствует высокий уровень, если выходы всех устройств отключены, и

низкий уровень, если хотя

бы одна микросхема устанавливает низкий

уровень.

В состав драйверов выходов входит ограничитель скорости изменения

фронтов. Во входных каскадах содержится схема подавления импульсов

длительностью менее 50 нс. Обратите внимание, что можно активизировать

внутренние подтягивающие резисторы на выводах микроконтроллера. Это

выполняется путем установки бит регистра PORT, соответствующего

выводам SCL и SDA (см. раздел "Порт ввода-вывода"). Использование

внутренних подтягивающих резисторов в некоторых случаях позволяет

избавиться от внешних. На рис. 6.11 показано, как подключить блоки TWI к

шине TWI. Номинал Rp зависит от VCC и емкости шины (обычно 4.7 кОм).

Рис. 6.11

Блок сравнения адреса используется только в подчиненном режиме и

выполняет поиск совпадения принятого адреса с 7-разрядным адресом в

Глава 6

256

регистре адреса TWI (TWAR). При совпадении адреса в блок управления

подается соответствующий сигнал. TWI может подтвердить или не

подтвердить данный адрес в зависимости от установок регистра TWCR.

Несмотря на то, что во всех режимах сна от блока TWI отключен сигнал

системной синхронизации, интерфейс продолжает подтверждать

собственный подчиненный адрес или адрес общего вызова за счет

использования синхронизации

шины TWI в качестве тактового источника. В

этом случае микроконтроллер возобновляет нормальную работу, а в процессе

возобновления работы и до сброса флага TWINT блок TWI удерживает

низкий уровень на линии SCL.

Блок шинного интерфейса содержит сдвиговый регистр данных и адреса

(TWDR), контроллер управления условиями СТАРТ/СТОП и схему

арбитрации. TWDR содержит передаваемый байт адреса/данных или

принятый байт адреса/данных. Кроме того, в регистре также содержится

передаваемый или принятый бит ПОДТВ или НЕТ ПОДТВ.

Контроллер СТАРТ/СТОП отвечает за генерацию и детектирование

условий СТАРТ, ПОВТОРНЫЙ СТАРТ и СТОП. Контроллер СТАРТ/СТОП

позволяет определить условия СТАРТ и СТОП даже при нахождении

микроконтроллера в одном из режимов сна,

позволяя возобновить

нормальную работу микроконтроллера при адресации со стороны ведущего

устройства. Если TWI инициирует передачу в качестве ведущего устройства,

то схема арбитрации непрерывно следит за передачей, пытаясь определить,

находится ли арбитрирование в процессе. Если TWI потерял арбитраж, то

блок управления информируется об этом. В этом случае выполняются

требуемые действия и генерируются соответствующие коды

статуса.

6.3. Универсальный асинхронный (синхронно-асинхронный)

приемопередатчик UART(USART)

Последовательные интерфейсы

257

Универсальный синхронный и асинхронный последовательный

приемопередатчик USART предназначен для организации гибкой

последовательной связи. Отличительными особенностями реализации этого

интерфейса в микроконтроллерах семейства AVR являются:

- полнодуплексная работа (раздельные регистры последовательного

приема и передачи);

- асинхронная или синхронная работа;

- ведущее или подчиненное тактирование связи в синхронном режиме

работы;

- высокая разрешающая способность генератора скорости связи;

-

поддержка формата передаваемых данных с 5, 6, 7, 8 или 9 битами

данных и 1 или 2 стоп-битами;

- аппаратная генерация и проверка бита четности;

- определение переполнения данных;

- определение ошибки в структуре посылки;

- фильтрация шума с определением ложного старт-бита и цифровым

ФНЧ;

- три раздельных прерывания по завершении передачи, освобождении

регистра передаваемых данных и завершении

приема;

- режим многопроцессорной связи;

- режим удвоения скорости связи в асинхронном режиме.

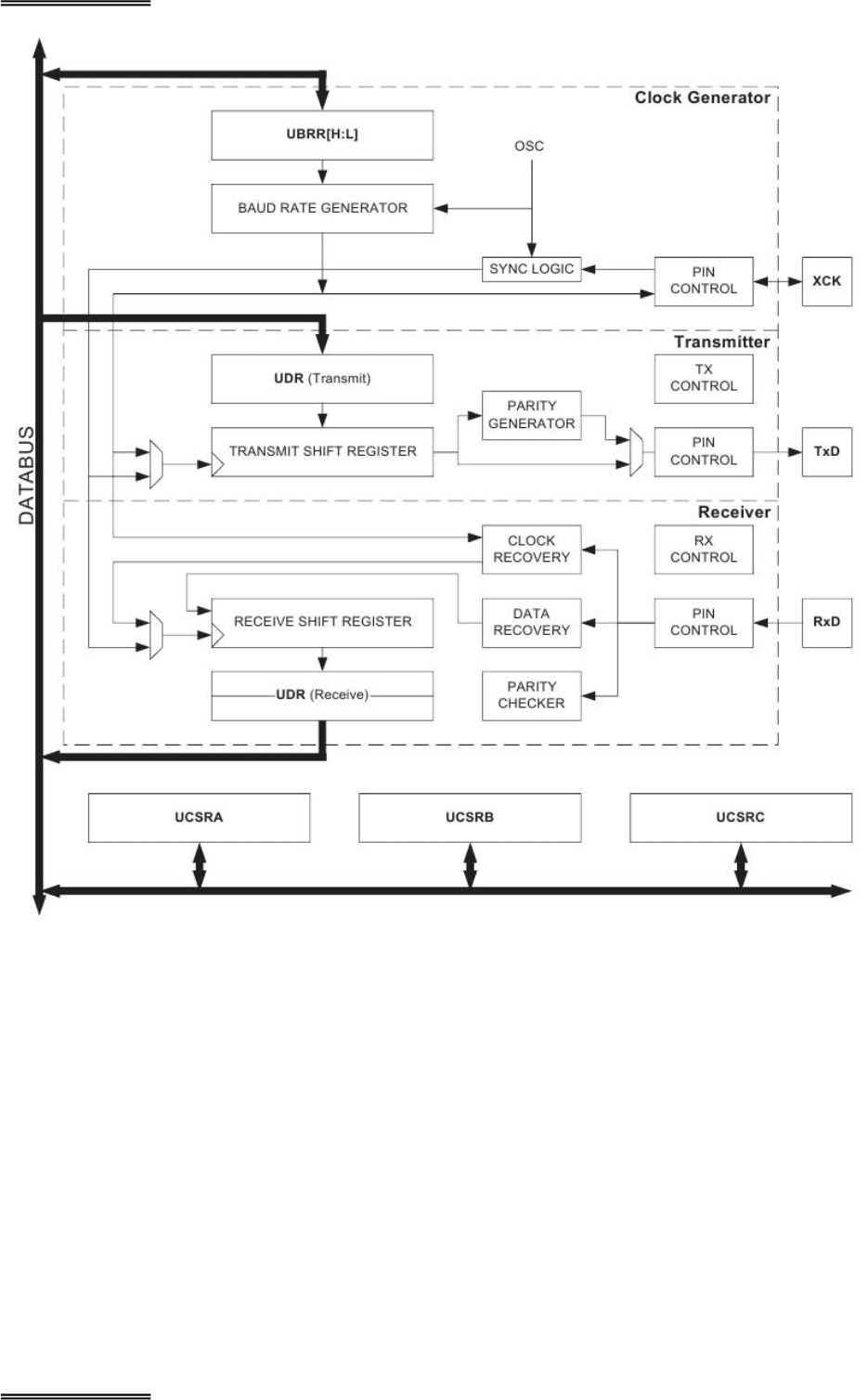

На рис. 6.12 представлена упрощенная функциональная схема USART,

жирным шрифтом выделены регистры и выводы USART.

Глава 6

258

Рис. 6.12

На рис. 6.12 пунктирной линией выделены три основных блока USART:

тактовый генератор, передатчик и приемник. Регистры управления

используются всеми блоками. Логика тактового генератора состоит из

логики синхронизации, связанной с внешним тактовым входом (используется

в подчиненном режиме) и генератора скорости связи. Вывод XCK

(синхронизация передачи) используется только в режиме синхронной

передачи. Передатчик

состоит из одного буфера записи, последовательного

Последовательные интерфейсы

259

сдвигового регистра, генератора паритета и управляющей логики, которая

поддерживает различные форматы последовательной посылки. Буфер записи

позволяет непрерывно передавать данные без каких-либо задержек между

передачей посылок. Приемник является более сложным блоком USART, т.к.

в его состав входят модули обнаружения данных и синхронизации. Модули

обнаружения необходимы для асинхронного приема данных. Помимо

модулей

обнаружения в приемник входит устройство проверки паритета,

сдвиговый регистр, и двухуровневый приемный буфер (UDR). Приемник

поддерживает те же последовательные форматы, что и передатчик, и может

определить ошибку в посылке (кадре), переполнение данных и ошибку

паритета.

Логика генерации тактовых импульсов формирует основную

синхронизацию приемника и передатчика. USART поддерживает четыре

режима работы синхронизации: нормальная

асинхронная, асинхронная с

удвоением скорости, ведущая синхронная и подчиненная синхронная. Бит

UMSEL в регистре С управления и статуса (UCSRC) позволяют выбрать

асинхронную или синхронную работу. Удвоение скорости (только в

асинхронном режиме) управляется битом U2X в регистре UCSRA. При

использовании синхронного режима (UMSEL = 1) соответствующий бит в

регистре направления данных для вывода XCK (DDR_XCK) задает будет ли

синхронизация внутренней (

ведущий режим) или внешней (подчиненный

режим). Вывод XCK активен только при использовании синхронного

режима.

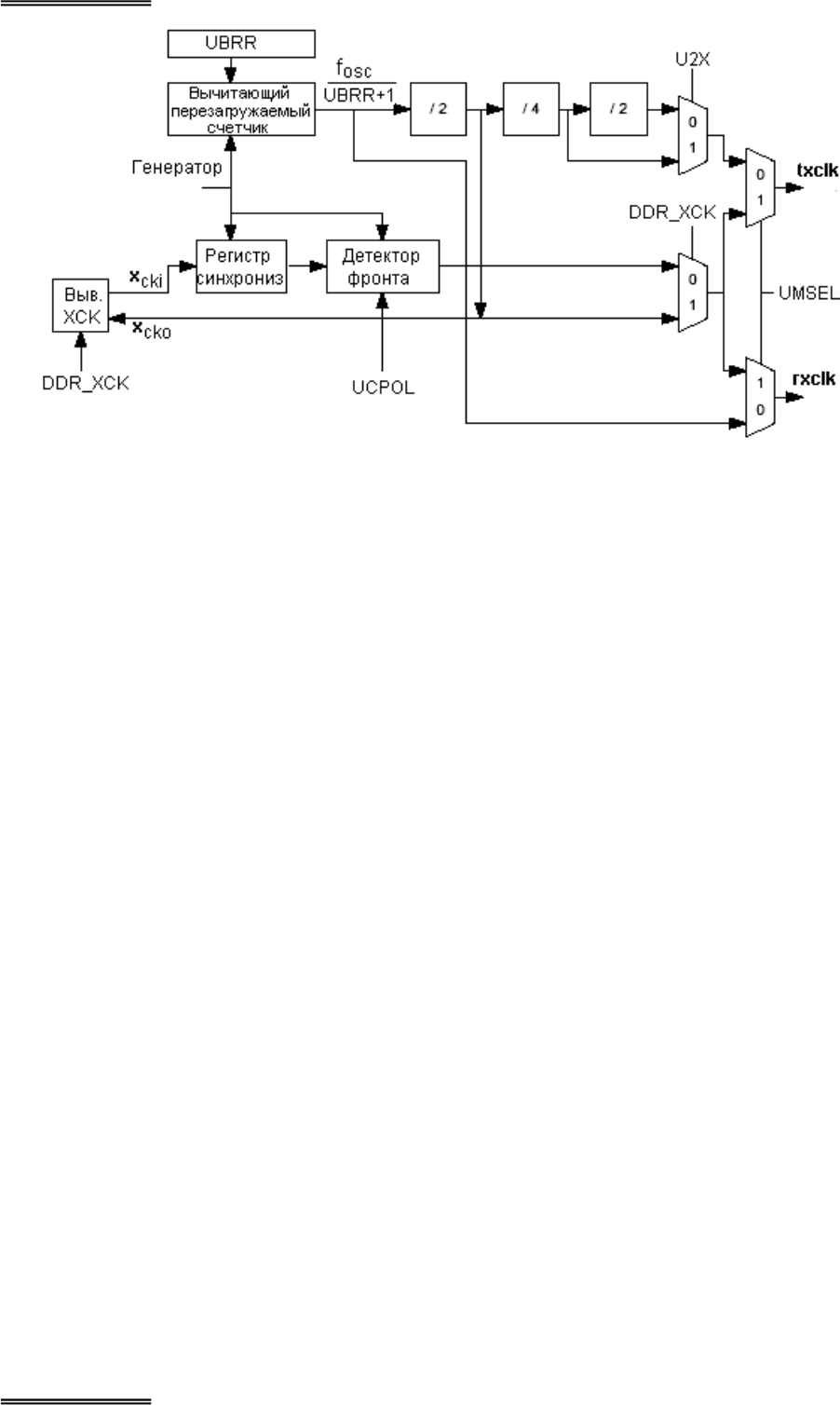

На рисунке 6.13 показана функциональная схема логики синхронизации.

Глава 6

260

Рис. 6.13

Описание сигналов:

- txclk - синхронизация передатчика (внутренний сигнал);

- rxclk - основная синхронизация приемника (внутренний сигнал);

- xcki - вход от вывода XCK (внутренний сигнал), используется для

синхронной подчиненной работы;

- xcko - выход синхронизации к выводу XCK (внутренний сигнал),

используется в ведущем синхронном режиме;

- fosc - вывод частоты XTAL (системная синхронизация).

Внутренняя синхронизация используется для асинхронного и ведущего

синхронного режимов работы

.

Регистр генератора скорости связи (UBRR) и связанный с ним

вычитающий счетчик функционируют как программируемый предделитель

или генератор скорости связи. Вычитающий счетчик тактируется системной

синхронизацией (f

osc

) и перезагружается значением из регистра UBRR всякий

раз при достижении нулевого значения или после записи регистра UBRRL.

Тактовый сигнал генерируется всякий раз при достижении счетчиком

нулевого значения. Данный тактовый сигнал является тактовым выходом