Рудякова А.Н., Липинский А.Ю., Данилов В.В., Рудяков И.Ю. Аппаратно-программные средства встраиваемых компьютерных систем

Подождите немного. Документ загружается.

Порты ввода-вывода микроконтроллеров

191

соответственно, к битам PORTxn по адресу PORTx, а к битам PINxn по

адресу PINx.

Биты DDxn регистра DDRx определяют направленность линии ввода-

вывода. Если DDxn = 1, то Pxn конфигурируется на вывод. Если DDxn=0, то

Pxn конфигурируется на ввод.

Если PORTxn = 1 при конфигурации линии порта на ввод, то

разрешается подключение подтягивающего резистора. Для выключения

данного резистора необходимо записать в PORTxn «0» или настроить линию

порта

на вывод. Во время сброса все линии портов находятся в третьем

(высокоимпедансном) состоянии, даже если не работает синхронизация.

Если PORTxn = 1 при конфигурации линии порта на вывод, то состояние

выхода будет определяться значением PORTxn.

Поскольку одновременная запись в регистры DDRx и PORTx

невозможна, то при переключении между третьим состоянием ({DDxn,

PORTxn} = 0b00) и выводом «1» ({DDxn, PORTxn} = 0b11) должно

возникнуть промежуточное состояние

или с подключенным подтягивающим

резистором ({DDxn, PORTxn} = 0b01) или с выводом лог. 0 ({DDxn,

PORTxn} = 0b10). Как правило, переход через состояние с подключением

подтягивающего резистора эквивалентно состоянию вывода «1», если вывод

микроконтроллера связан с высокоимпедансным входом. В противном

случае, необходимо установить бит PUD регистра SFIOR для выключения

всех подтягивающих резисторов на всех портах

Переключение между вводом с подтягивающими резисторами и

выводом низкого уровня связано с аналогичной проблемой. Поэтому,

пользователь вынужден использовать или третье состояние ({DDxn,

PORTxn} = 0b00) или вывод лог. 1 ({DDxn, PORTxn} = 0b11) в качестве

промежуточного шага.

В таблице 4.1 приведено описание действия управляющих сигналов на

состояние вывода порта.

Глава 4

192

Таблица 4.1 –

Настройка вывода порта

DDxn PORTxn

PUD

(в SFIOR)

Ввод-

вывод

Подтягивающий

резистор

Комментарий

0 0 X Ввод Нет Третье состояние (Z-состояние)

0 1 0 Ввод Да

Pxn будет источником тока при

подаче внешнего низкого

уровня

0 1 1 Ввод Нет Третье состояние (Z-состояние)

1 0 X Вывод Нет Вывод лог. 0 (втекающий ток)

1 1 X Вывод Нет Вывод лог. 1 (вытекающий ток)

Независимо от значения бита направления данных DDxn состояние

вывода порта может быть опрошено через регистровый бит PINxn. Как

показано на рис. 4.2 регистровый бит PINxn и предшествующая ему

триггерная защелка составляют синхронизатор. Данный подход позволяет

избежать метастабильности, если изменение состояния на выводе произошло

около фронта внутренней синхронизации. Однако такой подход связан с

возникновением задержки.

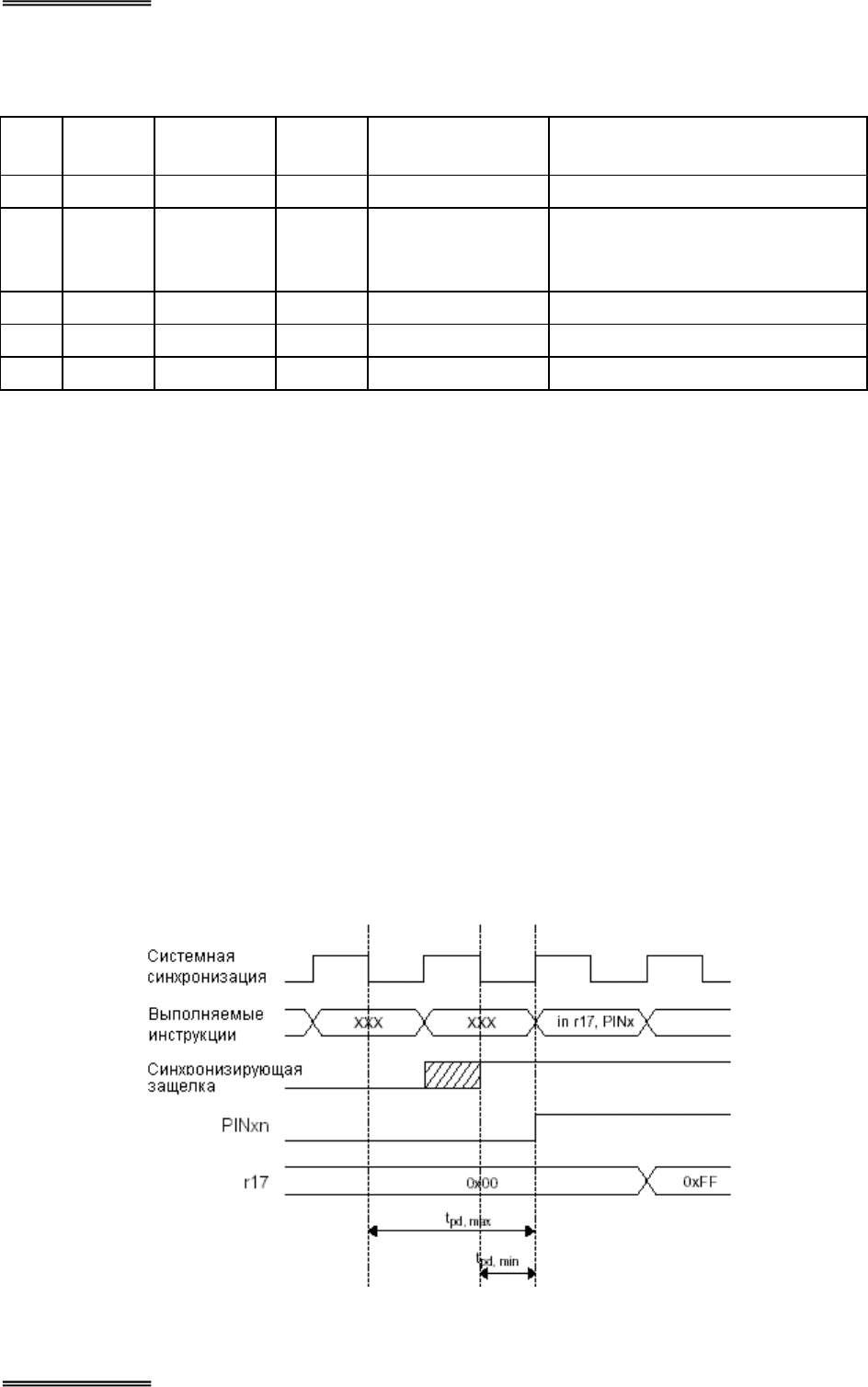

На рис. 4.3 представлена временная диаграмма

синхронизации во время опроса внешне приложенного к выводу уровня.

Длительности минимальной и максимальной задержек на распространение

сигнала обозначены как t

pd,max

и t

pd,min

, соответственно.

Рис. 4.3

Порты ввода-вывода микроконтроллеров

193

В следующем примере показано как установить на линиях 0 и 1 порта В

уровень «1», а на линиях 2 и 3 – «0», а также как настроить линии 4…7 на

ввод с подключением подтягивающих резисторов на линиях 6 и 7.

unsigned char i;

...

/* Разрешается подтягивание, и устанавливаются высокие

выходные уровни */

/* Определяются направления линий портов */

PORTB = (1<<PB7)|(1<<PB6)|(1<<PB1)|(1<<PB0);

DDRB = (1<<DDB3)|(1<<DDB2)|(1<<DDB1)|(1<<DDB0);

...

/* Опрос состояния выводов порта*/

i = PINB;

...

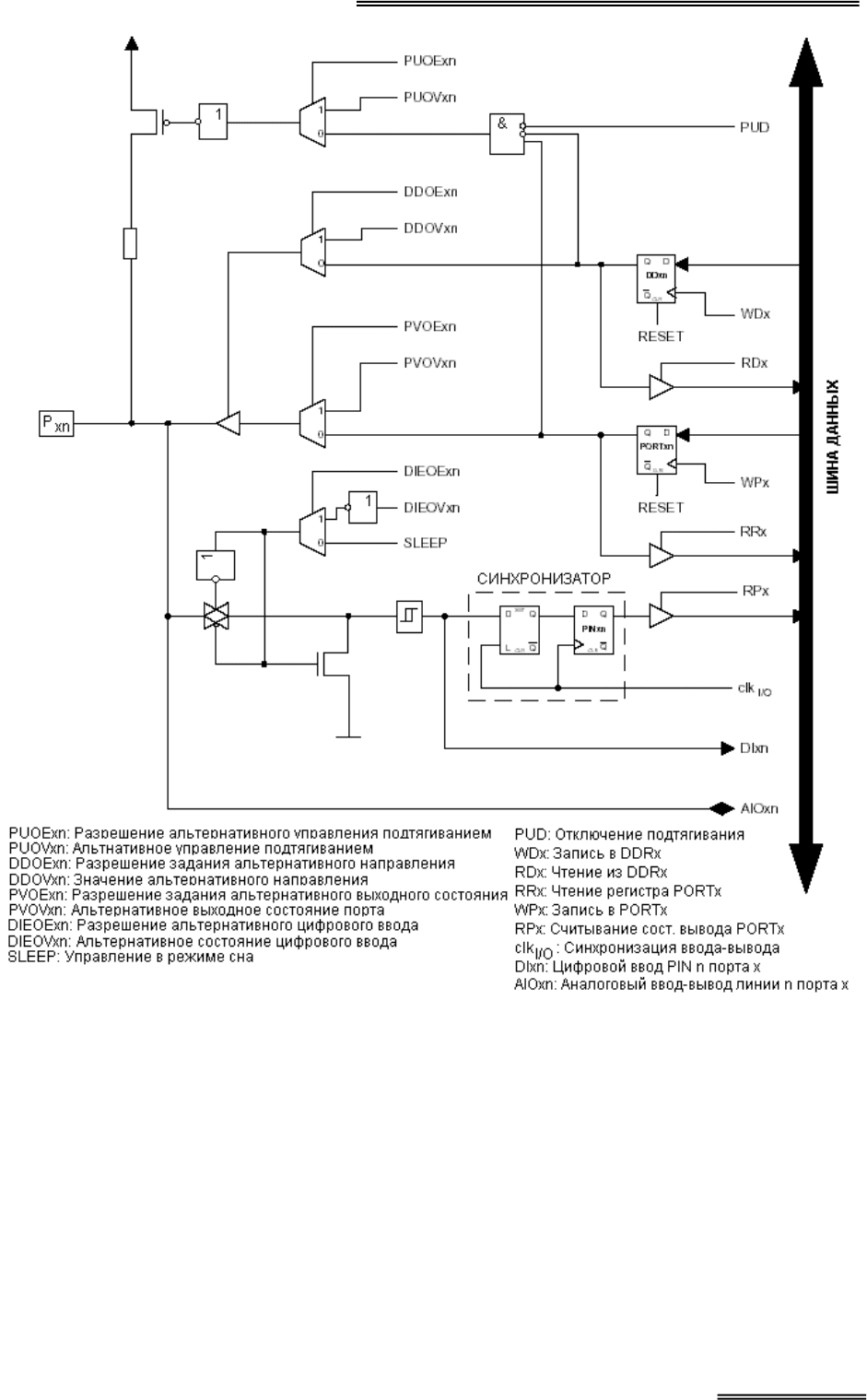

Как показано на рис. 4.2 входной цифровой сигнал может быть

зашунтирован к общему на входе триггера Шмита. Сигнал, обозначенный на

рисунке как SLEEP, устанавливается при переводе микроконтроллера в

режим выключения (Power-down), экономичный режим, дежурный режим и

расширенный дежурный режим. Это позволяет избежать повышения

потребляемого тока в случае, если некоторые входные сигналы окажутся в

плавающем состоянии или уровень входного аналогового сигнала будет

близок к VCC/2.

Сигнал SLEEP игнорируется по входам внешних прерываний. Если

запросы на внешнее прерывание отключены, то SLEEP действует и на эти

выводы. SLEEP также игнорируется на некоторых других входах при

выполнении их альтернативных функций.

Если на выводе внешнего асинхронного прерывания, настроенного на

прерывание по нарастающему фронту

, падающему фронту или на любое

изменение, присутствует уровень «1», и при этом внешнее прерывание не

разрешено, то соответствующий флаг внешнего прерывания будет

установлен при выходе из выше упомянутых режимов сна, т.к. функция

шунтирования на входе в режимах сна приводит возникновению логических

изменений.

Глава 4

194

Если несколько выводов остаются неиспользованными, то

рекомендуется гарантировать на них присутствие определенного логического

уровня. Не смотря на то, что большинство цифровых входов отключены в

режимах глубокого сна, как описано выше, необходимо избежать наличия

плавающих входов во избежание повышенного потребления тока во всех

других режимах работы микроконтроллера, где цифровой ввод разрешен.

Самым

простым методом гарантирования присутствия определенного

уровня на неиспользуемом выводе является разрешение подключения

внутреннего подтягивающего резистора. Однако в этом случае в режиме

сброса подтягивающие резисторы будут отключены. Если требуется малое

потребление и в режиме сброса, то необходимо устанавливать внешний

подтягивающий резистор к плюсу или к минусу питания. Подключение

выводов непосредственно к VCC

или GND не рекомендуется, т.к. может

возникнуть опасный ток при случайной конфигурации такого вывода на

вывод данных.

Большинство выводов поддерживают альтернативные функции в

дополнение к универсальному цифровому вводу-выводу. На рис. 4.4

показано, как управляющие сигналы, представленные на упрощенном рис.

4.2, могут быть отключены альтернативными функциями. Сигналы

отключения могут присутствовать не на

всех выводах, поэтому, данный

рисунок необходимо использовать как общее описание, применимое ко всем

выводам портов семейства AVR-микроконтроллеров.

Сигналы WPx, WDx, RLx, RPx и RDx являются общими в пределах

одного порта. Сигналы clkI/O, SLEEP, и PUD являются общими для всех

портов. Все остальные сигналы индивидуальны для каждого вывода.

Порты ввода-вывода микроконтроллеров

195

Рис. 4.4

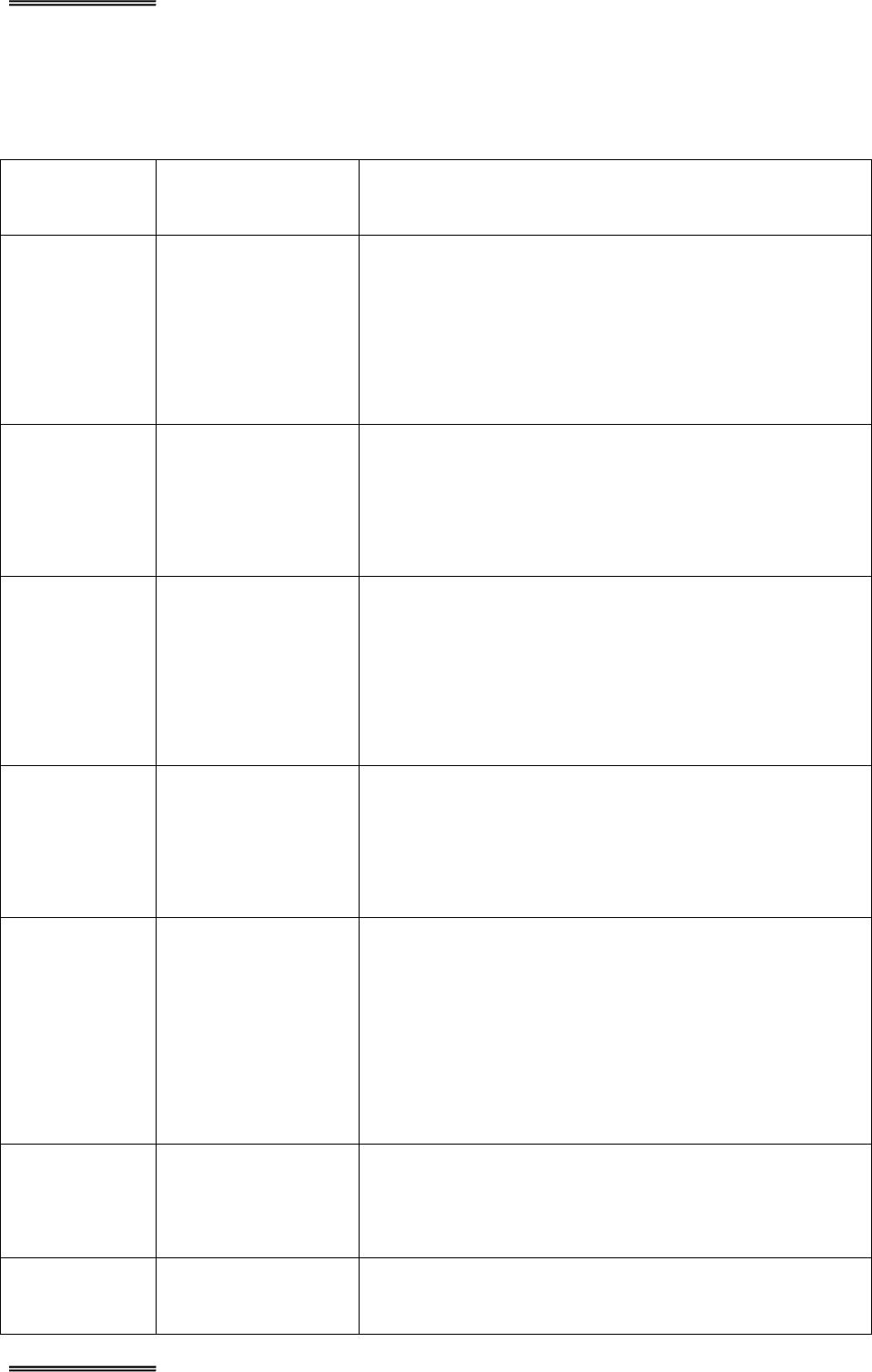

В таблице 4.2 приведены функции отключающих сигналов для

активизации альтернативных функций. Указатели на выводы и порты с рис.

4.4 не показаны в итоговых таблицах. Отключающие сигналы генерируются

внутренне в модулях, поддерживающих альтернативные функции.

Глава 4

196

Таблица 4.2 –

Общее описание отключающих сигналов для активизации альтернативных

функций

Наименование

сигнала

Полное

наименование

Описание

PUOE

Разрешение

альтернативного

управления

подтягиванием

Если данный сигнал установлен, то подключение

подтягивающего резистора определяется значением

сигнала PUOV. Если данный сигнал сброшен, то

подтягивающий резистор подключается, если

{DDxn, PORTxn, PUD} = 0b010.

PUOV

Альтернативное

управление

подтягиванием

Если PUOE установлен, то подтягивающий

резистор подключается/отключается, если PUOV

установлен/сброшен независимо от состояния

регистровых бит DDxn, PORTxn и PUD.

DDOE

Разрешение

задания

альтернативного

направления

Если этот сигнал установлен, то разрешение работы

выходного драйвера определяется значением

сигнала DDOV. Если этот сигнал сброшен, то

работа выходного драйвера разрешается

регистровым битом DDxn.

DDOV

Значение

альтернативного

направления

Если DDOE установлен, то работа выходного

драйвера разрешается/запрещается, когда DDOV

устанавливается/сбрасывается независимо от

состояния регистрового бита DDxn.

PVOE

Разрешение

задания

альтернативного

выходного

состояния порта

Если данный сигнал установлен и разрешена работа

выходного драйвера, то состояние на выходе порта

определяется сигналом PVOV. Если PVOE сброшен

и разрешена работа выходного драйвера, то

состояние на выходе порта определяется

регистровым битом PORTxn.

PVOV

Альтернативное

выходное

состояние порта

Если PVOE установлен, то выход порта принимает

состояние PVOV независимо от установки

регистрового бита PORTxn.

DIEOE

Разрешение

альтернативного

Если данный бит установлен, то функция

разрешения цифрового передается сигналу DIEOV.

Порты ввода-вывода микроконтроллеров

197

цифрового ввода Если данный сигнал сброшен, то разрешение

цифрового ввода определяется состоянием

микроконтроллера (нормальный режим, режимы

сна).

DIEOV

Альтернативное

состояние

цифрового ввода

Если DIEOE установлен, то цифровой ввод

разрешен/запрещен, если DIEOV

установлен/сброшен независимо от состояния

микроконтроллера (нормальный режим, режимы

сна).

DI Цифровой ввод

Сигнал цифрового ввода для альтернативных

функций. На рисунке сигнал подключен к выходу

триггера Шмита перед синхронизатором. Если

цифровой ввод используется как источник

синхронизации, то модуль с альтернативной

функцией будет использовать свой собственный

синхронизатор.

AIO

Аналоговый ввод-

вывод

Сигнал аналогового ввода/вывода

к_модулю/из_модуля с альтернативной функцией.

Сигнал подключается непосредственно к

контактной площадке и может использоваться

двунаправлено.

4.2. Способы устранения дребезга механических контактов при

вводе информации

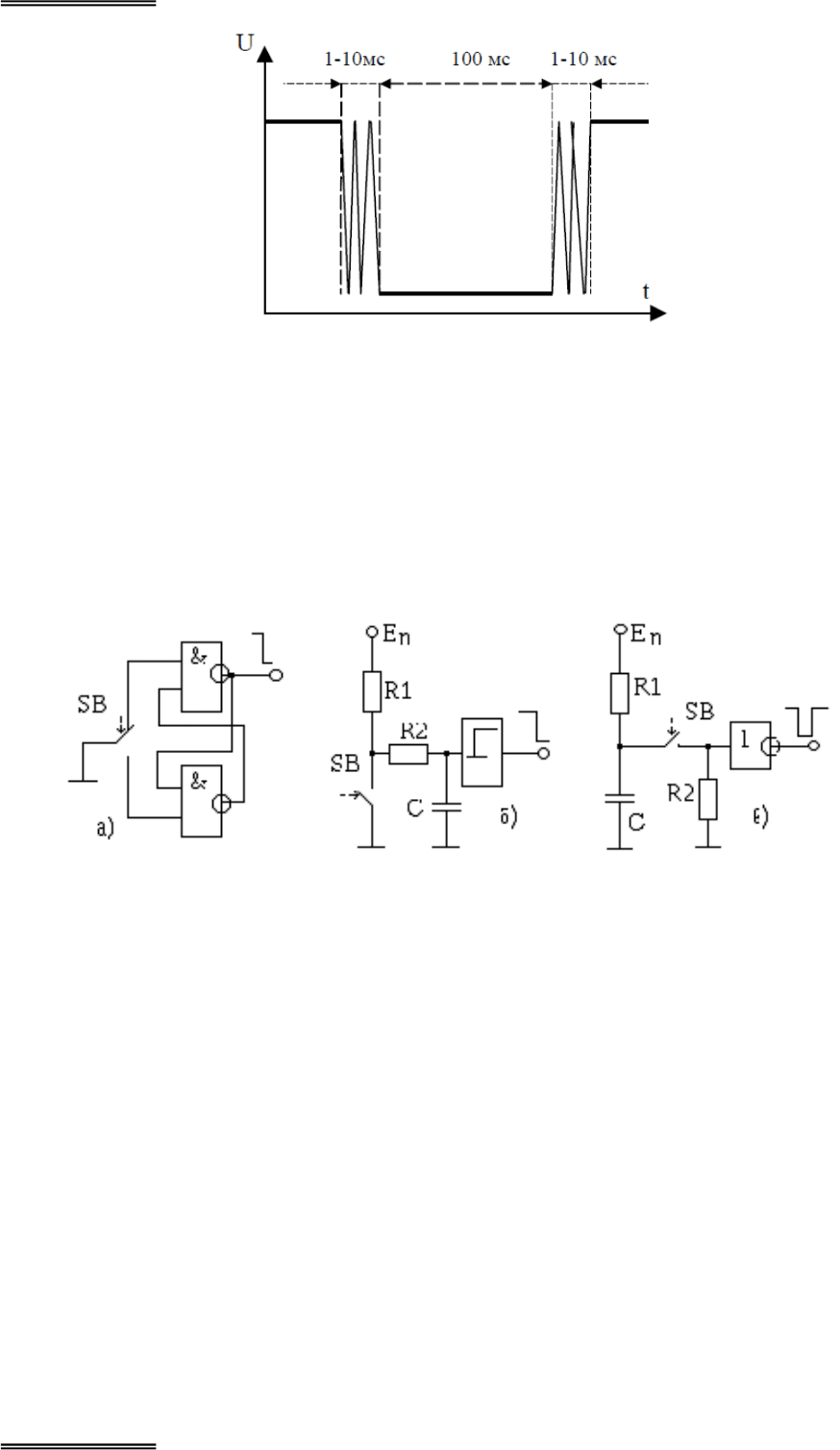

При работе микроконтроллера с датчиками, имеющими механические

или электромеханические контакты (кнопки, клавиши, реле и клавиатуры),

возникает явление, называемое дребезгом (см. рис. 4.5). Это явление

заключается в том, что при замыкании контактов возможно появление

отскока контактов, которое приводит к переходному процессу. При этом

сигнал с контакта может быть прочитан МК как случайная

последовательность нулей и единиц.

Глава 4

198

Рис. 4.5

Подавить это нежелательное явление можно схемотехническими

средствами с использованием буферного триггера, как показано на рис. 4.6.

Рис. 4.6

Наиболее надежной и простой в схемном решении является схема

подавления дребезга на статическом RC - триггере (рис. 4.6-а). Сигнал “0”,

подаваемый с помощью переключателя к одному из входов этого триггера

опрокидывает его. Причем при каждом срабатывании переключателя

(кнопки) триггер реагирует на первое же замыкание соответствующей

контактной пары и последующие замыкания уже

не изменяют его состояние.

Недостатком такой схемы подавления дребезга является необходимость

использования контактов на переключение, что не всегда приемлемо. В тех

случаях, когда кнопка (переключатель) имеет всего одну пару контактов

Порты ввода-вывода микроконтроллеров

199

только на замыкание, применяются схемы, использующие постоянную

времени перезаряда конденсатора.

Формирователь, показанный на рис. 4.6-б лишен этого недостатка. Он

состоит из триггера Шмидта, на входе которого включена интегрирующая

цепь (R2, C). При замыкании контактов кнопки SB напряжение на входе цепи

R2 C падает до нуля. Возникающее в процессе переключения

кратковременные импульсы, вызванные “дребезгом”, сглаживаются

интегрирующей

цепью. Постоянная времени интегрирующей цепи

выбирается так, чтобы амплитуда пульсаций сигнала на её выходе была

меньше порога чувствительности триггера Шмидта.

Рассматриваемый формирователь может работать и без сопротивления

R2 (его включают в качестве токоограничивающего сопротивления через

замкнутые контакты кнопки). Благодаря малому сопротивлению замкнутых

механических контактов первое же их замыкание приводит к полному

разряду конденсатора. Последующие же размыкания контактов, вызванные

дребезгом, практически не увеличивают напряжение на конденсаторе

вследствие относительно большой постоянной времени его заряда.

Формирователь импульсов на одном инверторе (рис. 4.6-в) позволяет

получить относительно большую постоянную времени перезаряда

конденсатора при малой его емкости. При замыкании контактов кнопки

конденсатор С быстро разряжается через R2. В отличие

от рассмотренных

выше формирователей, здесь на выходе вырабатывается импульс,

длительность которого определяется постоянной времени RC цепи.

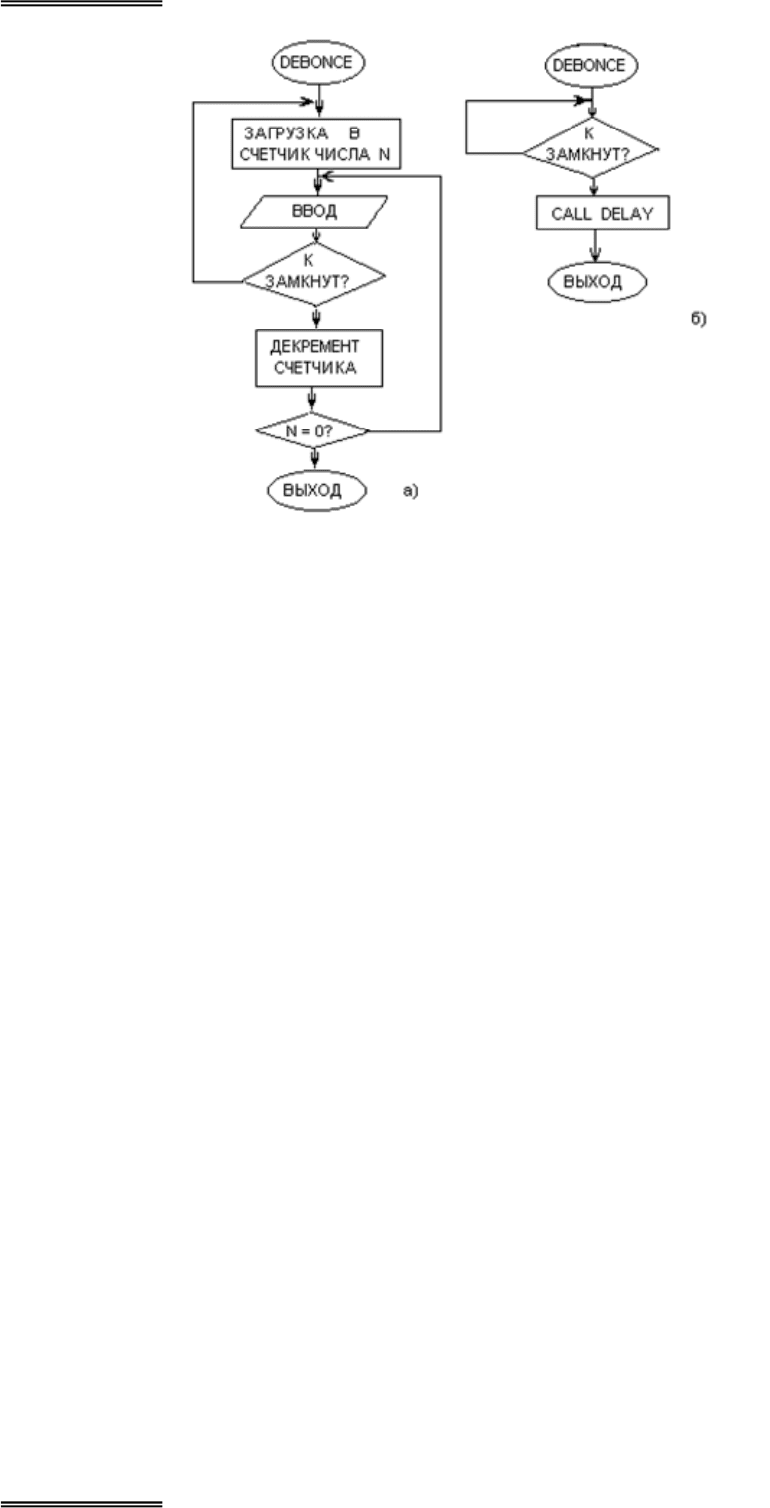

Часто устранение дребезга контактов выполняется программными

способами, наибольшее распространение из которых получили следующие

два: 1) подсчет заданного числа совпадающих значений сигнала; 2)

временная задержка. Блок-схемы алгоритмов реализации этих способов

приведены на рис. 4.7.

Глава 4

200

Рис. 4.7

Суть первого способа состоит в многократном считывании сигнала с

контакта. Подсчет удачных опросов (т.е. опросов, обнаруживших, что

контакт устойчиво замкнут) ведется программным счетчиком. Если после

серии удачных опросов встречается неудачный, то подсчет начинается

сначала. Контакт считается устойчиво замкнутым (дребезг устранен), если

последовало N удачных опросов. Число N подбирается экспериментально

для

каждого типа используемых датчиков и лежит в пределах от 5 до 50.

Устранение дребезга контакта путем введения временной задержки

заключается в следующем. Программа, обнаружив замыкание контакта,

запрещает опрос состояния этого контакта на время, заведомо большее

длительности переходного процесса. Временная задержка (в пределах 1-20

мс) подбирается экспериментально для каждого типа датчиков.