Петросьянц В.В. Измерительно-вычислительные комплексы (канал общего пользования)

Подождите немного. Документ загружается.

100

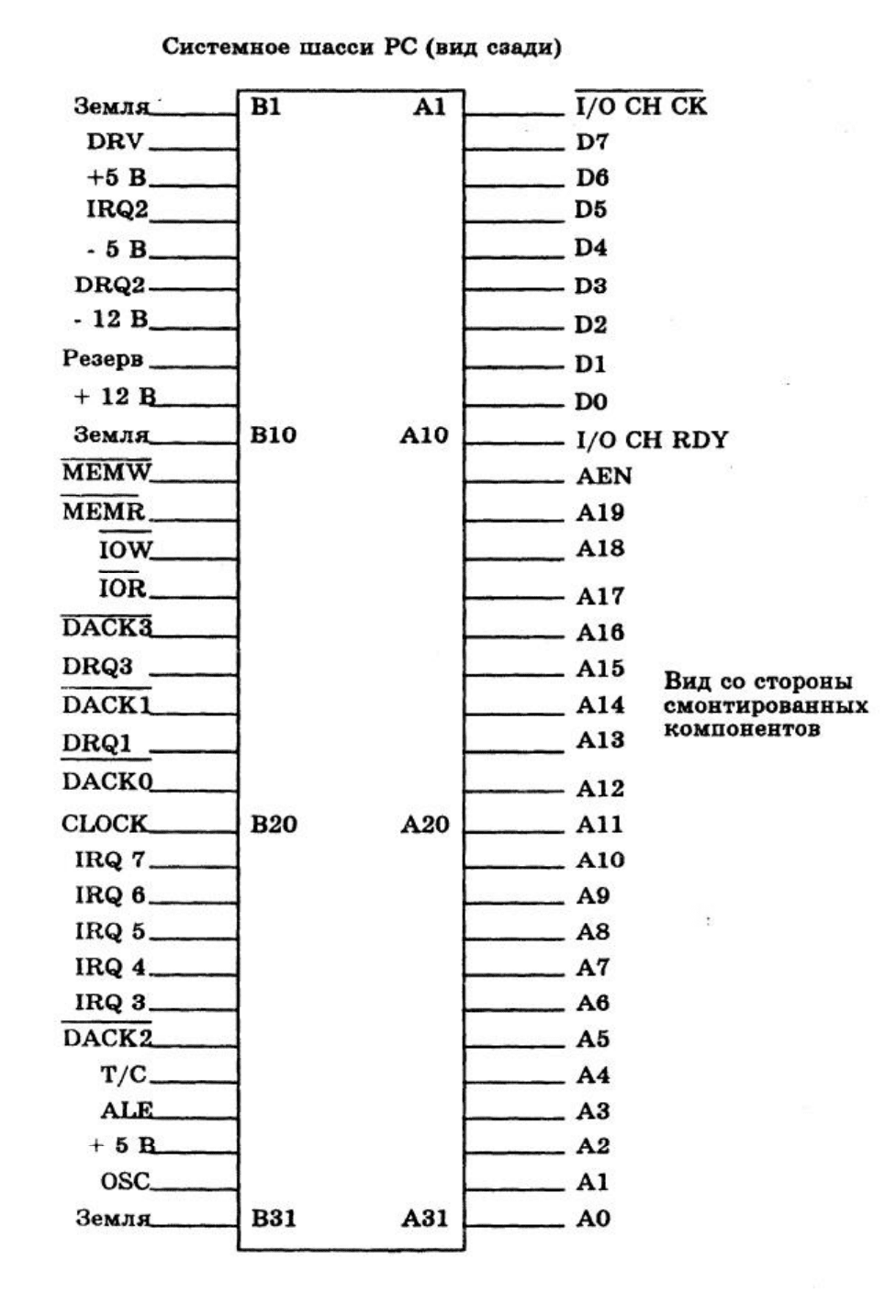

Рис. 42. Разводка вывод системой шиной IBM PC

101

AEN ( разрешение адреса). Этот сигнал выдается контроллером ПДП и

указывает, что идет выполнение цикла прямого доступа к памяти. Обычно он

служит для блокировки логики декодирования порта ВВ во время цикла прямо-

го доступа к памяти. Это необходимо для того, чтобы адрес прямого доступа к

памяти не был случайно использован в качестве адреса ВВ. Такая ситуация, в

принципе, может возникнуть, поскольку управляющие линии IOR и IOW могут

переходить в активное состояние во время цикла ПДП.

OSC (сигналы задающего генератора), CLOCK. OSC - высокочастотный

системный синхросигнал с периодом повторения 70 нс (частота 14,31818 МГц)

и коэффициентом заполнения 0,5. Частота сигнала CLOCK равна 1/3 частоты

задающего генератора (4,77 МГц). Она является рабочей частотой микропро-

цессора Intel 8088. Сигнал CLOCK имеет период повторения 210 нс и коэффи-

циент заполнения 0,33.

IRQ2-IRQ7 ( запросы на прерывание). Устройства ввода-вывода исполь-

зуют шесть линий ввода для генерирования запросов на прерывание, направ-

ляемых процессору 8088. Этим запросам присваиваются определенные приори-

теты (IRQ2 задает высший приоритет). Запрос на прерывание генерируется пу-

тем выдачи высокого логического уровня на линию IRQ и поддержания его до

тех пор, пока прием этого сигнала не будет подтвержден процессором. По-

скольку сигнал подтверждения прерывания (INTA), выдаваемый процессором,

не появляется на системной шине, подтверждение обычно поступает по одной

из линий порта ВВ, для чего используется команда OUT, выдаваемая подпро-

граммой обработки прерываний.

I/O CH RDY (готовность канала ВВ).

Этот входной сигнал используется для инициирования периодов ожидания,

с помощью которого увеличивается длительность шинных циклов микропроцес-

сора при работе с "медленным" запоминающим и внешними устройствами.

CKCHI/O (проверка канала ВВ).

Этот сигнал с активным низким уровнем служит для "информирования"

102

процессора 8088 о том, что в данных, поступивших из памяти или от устройст-

ва ВВ, содержится ошибка, обнаруженная контроллером по четности.

RESET DRY (инициирование сброса).

Этот сигнал служит для сброса или установки в исходное состояние сис-

темной логики либо при включении питания, либо в том случае, когда после

подачи питания обнаружится, что один из уравнений

напряжения питания выходит за допустимые рабочие пределы. Этот сиг-

нал синхронизируется срезом импульса OSC.

DRQ1-DRQ3 (запрос прямого доступа к памяти).

Эти входные сигналы служат для запроса доступа к асинхронным каналам,

которые используются периферийными устройствами, чтобы получить возмож-

ность прямого доступа к памяти. На линии DRQ должен поддерживаться высокий

уровень сигнала до тех пор, пока уровень на соответствующей линии DACK не

станет низким. Обратите внимание на то, что на шине отсутствует линия сигнала

RQ0, который служит для регенерации динамической памяти системы.

DACK3

-

DACK0

(сигналы подтверждения запроса ПДП).

Эти сигналы с активным низким уровнем используются для под-

тверждения приема сигналов запроса ПДП и для регенерации динамической

памяти (DACK0).

Т/С (конец блока данных).

По этой линии выдается импульс, когда достигается конец блока данных,

передаваемых по каналу прямого доступа к памяти.

3.2. Карта распределения и временные диаграммы ввода-вывода IBM PC

Для генерации правильных сигналов выбора функциональных узлов не-

обходимо знать вид адресации портов ввода-вывода и карту их распределения.

При общем числе возможных портов в компьютере PC, равном 1024, для обра-

щения к ним используется 10-разрядный адрес порта - разряды А0-А9. Карта

адресов портов ВВ разделена на две части. 512 адресов с 0000Н по 01FFH (ше-

103

стнадцатеричная запись) выделены для системной объединительной панели.

Адресное пространство с 0200Н по 03FFH, т.е. 512 адресов портов, предостав-

ляется схемным платам, которые вставляются в пять гнезд на шасси ком-

пьютера. Из таблицы 21 видно, что большинство из этих 512 адресов выделено

функциональным платам IBM. Портам макетной платы назначено всего 32 ад-

реса - с 300Н по 031FH.

Таблица 21. Карта распределения адресов ввода-вывода IBM PC

Шестнадца-

тиричный

адрес

Функция Закрепление

000-00F Микросхема ПДП типа 8237А-5

020-021 Контроллер прерываний 8259А

040-043 Таймер 8253-5

060-063

Программируемый периферийный интерфейс

8255А-5

080-083 Страничные регистры ПДП

ОА

х

Регистр маски NMI

ОС

х

Резерв

ОЕ

х

Резерв

100-1FF

Не используется

За компонентами

на системной

плате

200-20F Видеоигры

210-217 Устройство расширения

220-24F Резерв

278-27F Резерв

2F0-2F7

Резерв

2F8-2FF Асинхронная передача (2)

За портами

функциональ-

ных плат

300-31F

Макетная плата

320-32F Накопитель на жестком диске

378-37F Принтер

380-38С Передача по протоколу SDLC

390-399 Двоичная синхронная передача (2)

ЗА0-ЗА9 Двоичная синхронная передача (1)

3B0-3BF

Монохромный дисплей IBM/принтер

3C0-3CF Резерв

BD0-3DF Цветная графика

ЗЕ0-ЗЕ7 Резерв

3F0-3F7 Накопитель на гибком диске

3F8-3FF Асинхронная передача (1)

То же

104

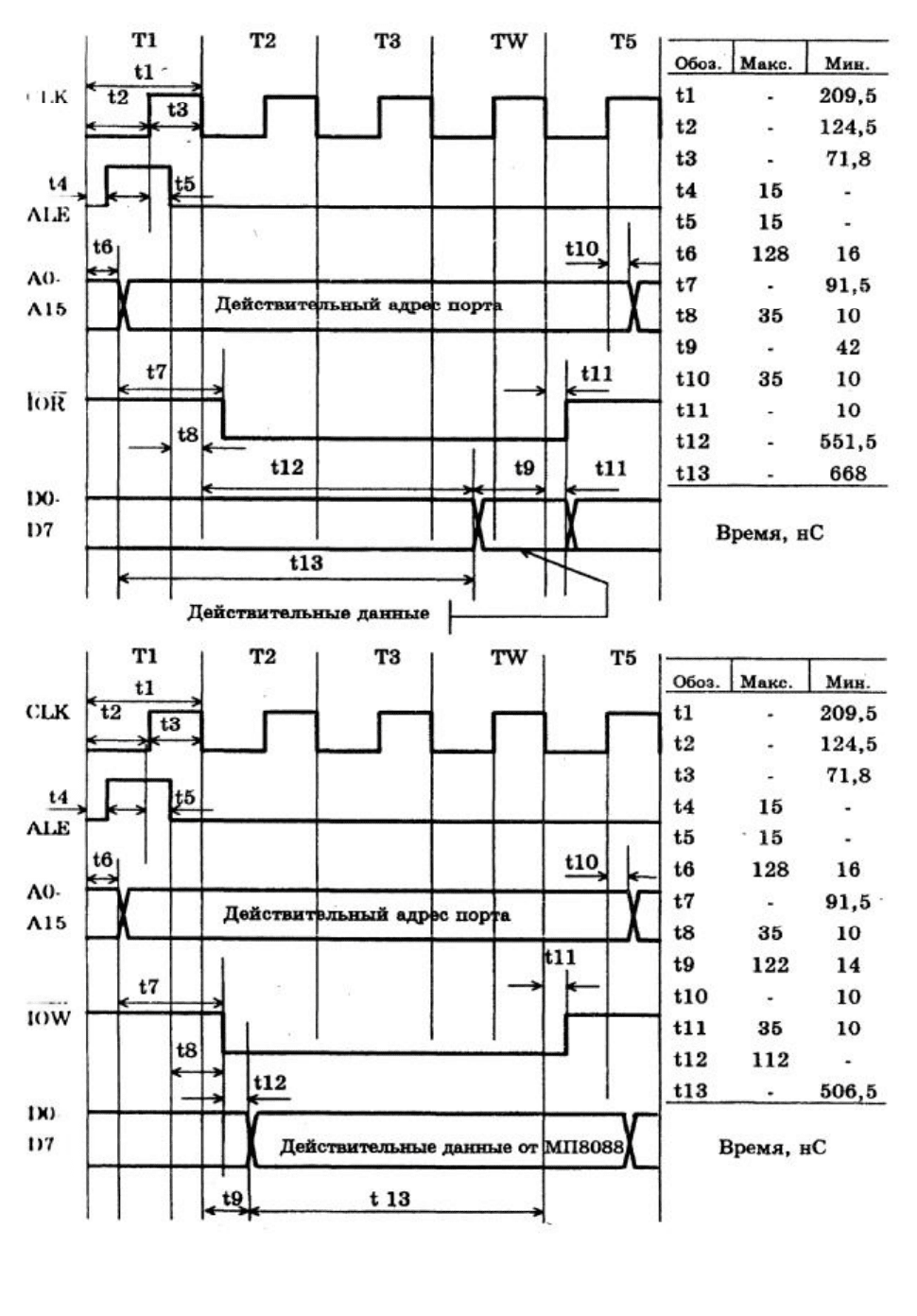

Для правильного взаимодействия любого интерфейса с интерфейсом IBM

PC необходимо обеспечение совместимости временного распределения его ра-

боты с аналогичными параметрами системной шины. Во временных диаграм-

мах и таблицах, приведенных на рисунке 43, представлена детальная информа-

ция о временном распределении шинных циклов записи и чтения ВВ.

Шинный цикл обычно состоит из четырех рабочих периодов дли-

тельностью Т (машинный такт), однако компьютер автоматически вводит в этот

цикл дополнительный период ожидания (TW). Таким образом, в компьютере

весь шинный цикл ВВ содержит как минимум пять периодов Т, т.е. его дли-

тельность равна примерно 1,05 мкс.

Шинный цикл может быть дополнительно увеличен путем регулирования

длительности сигнала готовности (10 СН RDY) на системной шине. Выводы

А16 - А19 адресной шины компьютера не переводятся в активное состояние во

время шинных циклов ВВ

Шинный цикл чтения ВВ инициируется каждый раз, когда мик-

ропроцессор 8088 выполняет команду IN. Во время периода Т1 в активное со-

стояние переключается линия сигнала ALE, по срезу которого выдается при-

знак того, что разряды А0-А15 адресной шины со держат действительный адрес

порта ВВ. Во время периода Т2 в активное состояние переводится сигнал

управления

IOR

, который указывает, что отклик адресуемого входного порта

должен заключаться в выводе им своего содержимого на шину данных. В нача-

ле периода Т4 процессор считывает информацию с шины данных, а затем ли-

ния сигнала

IOR

переводится в неактивное состояние.

Шинный цикл записи ВВ инициируется каждый раз, когда процессор

8088 выполняет команду OUT. Во время периода Т1 в активное состояние пе-

реводится управляющий сигнал ALE, по срезу которого выдается признак того,

что разряды А0-А15 адресной шины содержат действительный адрес порта.

105

Рис.43. Временное распределение шинных циклов записи и чтение ВВ

106

Затем время периода Т2 в активное состояние переключается сигнал

IOW

, ко-

торый указывает выбранному выходному порту, что ему следует считать со-

держимое шины данных. Далее в течение этого же периода процессор 8088 вы-

водит на шину данные, которые должны поступать на выходной порт.

В начале периода Т4 сигнал

IOW

переходит в неактивное состояние и

процессор 8088 удаляет данные с шины.

На рисунке 43 приводится информация о временных соотношениях в ви-

де данных для наихудшего случая по максимуму и минимуму. Следовательно,

эти данные справедливы для всех условий нагрузки шины и всех уровней на-

пряжений питания в пределах заданных данных.

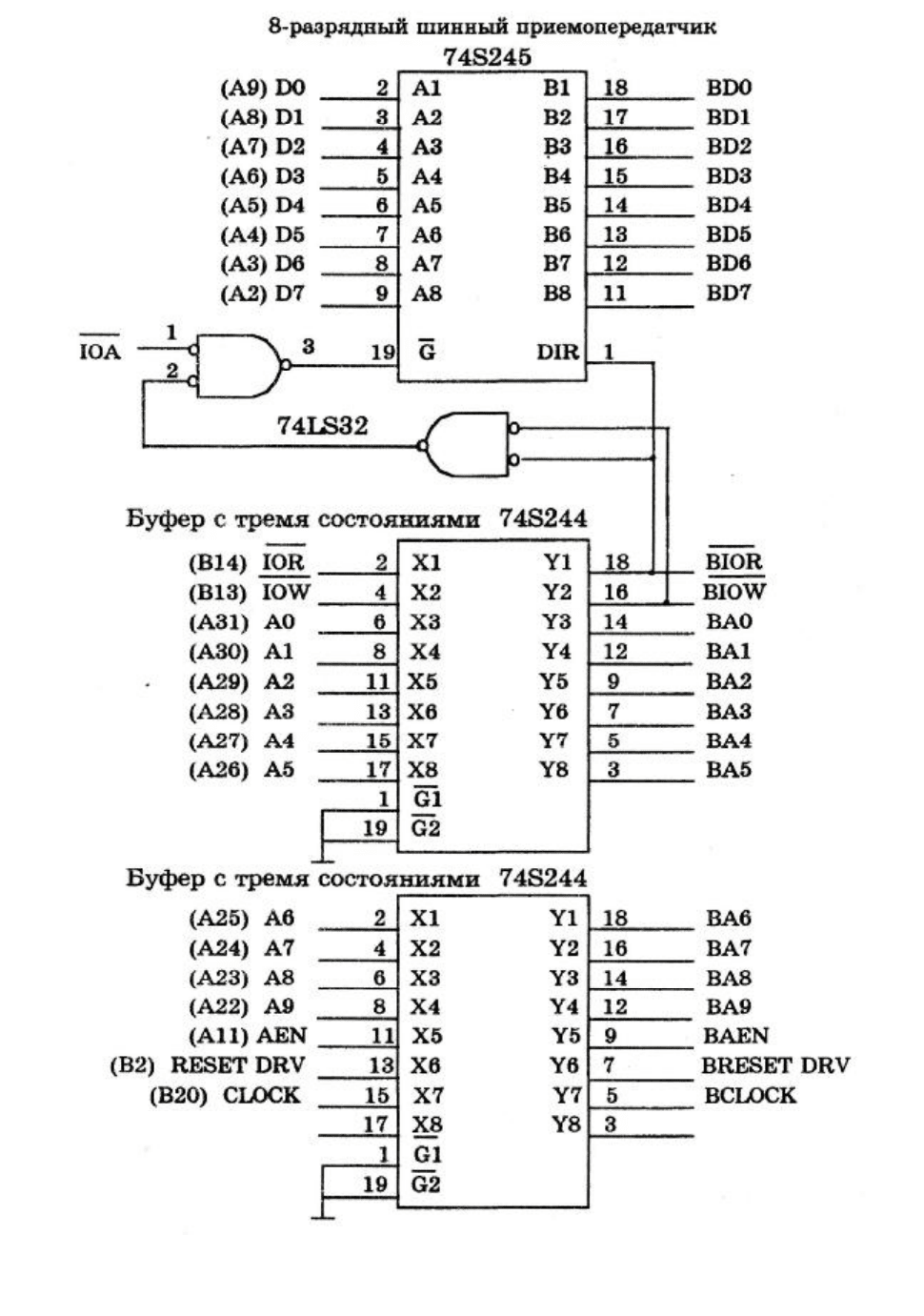

3.3. Буферизация и декодирование содержимого шины

На основе схемы буферизации реализованы шина буферизированных данных,

ВDО-ВВ7, адресная шина, ВА0-ВА9 и ряд линий управляющих сигналов:

BOIR

,

BIOW

, BRESET DRV, BCLOCK (рис. 44). Обозначения всех приведенных на рисун-

ке 44 сигналов начинаются с буквы В, означающей, что сигнал буферизован. Схема

декодирования генерирует 32 сигнала выбора портов, Е0-Е31 (ОЗООН-031FH).

Два буфера с тремя состояниями (74LS244) служат для буферизации разря-

дов А0-А9 адресной шины и требуемых управляющих сигналов. Для отображения

адресов 32 портов на нужную область адресного пространства содержимое адрес-

ных разрядов ВА5-ВА9 сравнивается с фиксированным значением ОЗН (00011) на

компараторе 74LS688, который вырабатывает разрешающий сигнал ВВ (

IOA

) для

микросхем дешифраторов. Сигнал выбора платы отпирает шинный приемопере-

датчик (74LS245), а также разрешает последующее декодирование адресных разря-

дов А0-А4. Это декодирование реализуется путем использования двух декодеров

типа "4 в 16" (74LS154). Сигнал BIOR задает направление передачи данных в шин-

ном приемопередатчике. Как и сигнал разрешения ИС, сигнал разрешения адреса

(AEN) служит для блокировки компаратора, так что во время шинного цикла при

прямом доступе к памяти нельзя обращаться ни к одному порту ВВ.

107

Рис. 44. Схема обеспечения сопряжения с шиной компьютера IBM PC

108

3.4. Сопряжение компьютера IBM PC с микросхемой порта ВВ типа

Intel 8255

Микросхема 8255 фирмы Intel представляет собой однокристальный про-

граммируемый интерфейс периферийных устройств (PPI), в котором реализо-

вано три программируемых порта ввода-вывода.

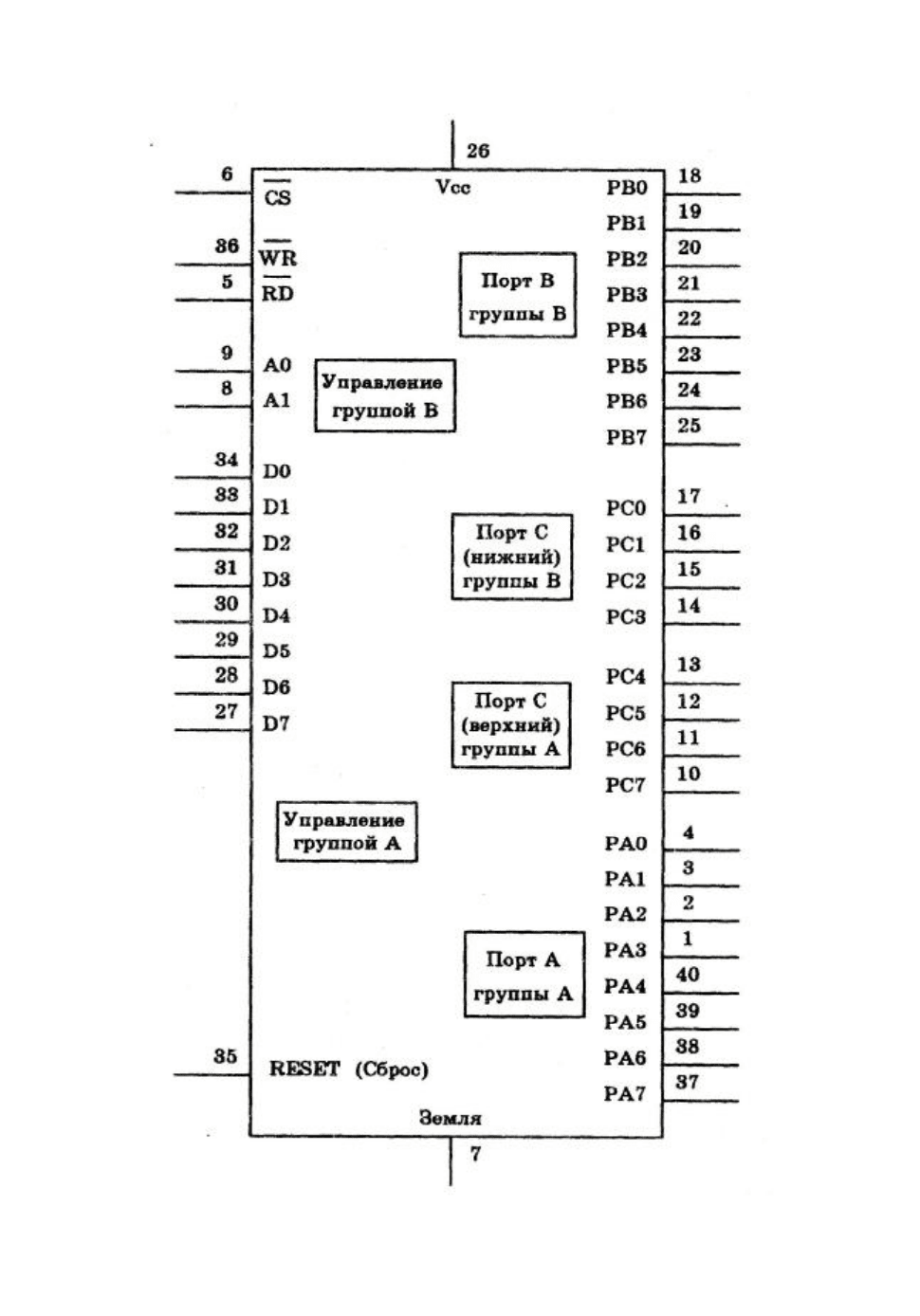

Структурная схема ИС Intel 8255 ( рис. 45) содержит управляющий ре-

гистр и три 8-разрядных порта ввода-вывода, получивших обозначение А, В, С.

Порт С, по существу, представляет собой два отдельных программируемых

порта: С-верхний (РС4-РС7) и С-нижний (РСО-РСЗ). Следует помнить, что у

пользователей есть возможность осуществлять запись информации в управ-

ляющий регистр, однако они не могут ее считывать.

Микросхема 8255 переводится в активное состояние, когда логика деко-

дирования активизирует линию соответствующего сигнала выбора ИС (

CS

)

(табл. 22). Кроме того, по АО и А1 выбираются управляющий регистр и один из

трех портов организации передачи данных. Входы микросхемы

RD

и

WR

предназначены для задания режима чтения или записи информации.

Когда включается питание системы, поданный на ИС 8255 сигнал-сброса

переводит все 24 вывода, связанных с тремя портами ВВ, в третье состояние (с

высоким импедансом). Микросхема остается в этом состоянии до тех пор, пока

прикладная программа не запирает в управляющий регистр слово, определяю-

щее режим работы.

Имеется три возможных режима работы:

1. Режим 0: ввод-вывод общего типа.

2. Режим 1: стробируемый ввод-вывод.

3. Режим 2: двусторонняя шина данных.

Выбор режима 0 ( рис.46) предоставляет в распоряжение системы два 8-

разрядных порта (А и В) и два 4-разрядных порта (С-верхний и С-нижний). Ка-

ждый порт можно запрограммировать на работу в качестве входного или вы-

ходного порта. Выходы портов буферизируются, тогда как на входах буферные

109

регистры не устанавливаются. В этом режиме возможно задание 16 различных

конфигураций ввода-вывода.

Рис. 45. Структурная схема ИС Intel 8255