Новиков А.А., Амелина М.А. Математическое моделирование в электронике. Курс лекций

Подождите немного. Документ загружается.

Современные и перспективные БИС/СБИС со сложными программируемыми и

репрограммируемыми структурами (FPGA, CPLD, FLEX, SOC и др.)

§ 8.1. Общие сведения

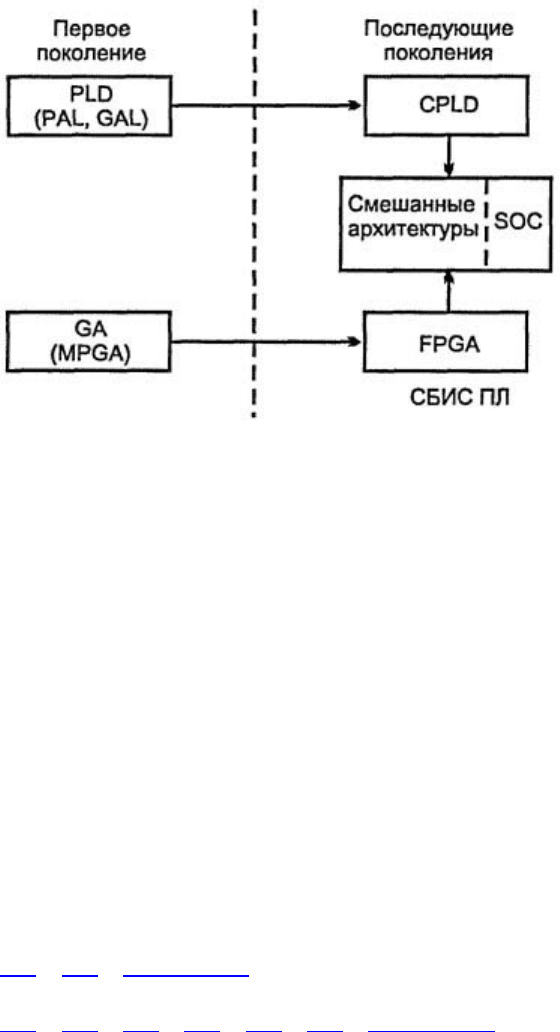

Микросхемы ПЛМ, ПМЛ и БМК, рассмотренные в гл. 7, положили начало двум

основным ветвям дальнейшего развития логических схем с программируемой и

репрограммируемой структурами. Продолжением линии ПМЛ стали БИС/СБИС CPLD

(Complex Programmable Logic Devices), а линии БМК - FPGA (Field Programmable Gate

Arrays). Стремление объединить достоинства обеих линий привело к созданию

БИС/СБИС смешанной (комбинированной) архитектуры, для которых еще не выработано

общепринятое название (фирма Altera пользуется названием FLEX (Flexible Logic Element

MatriX) - гибкие). Рост уровня интеграции дал возможность размещать на кристалле

схемы, сложность которых соответствует целым системам. Эти схемы именуются SOC

(Systems On Chip).

Сказанное иллюстрируется рис. 8.1, где под MPGA понимаются Mask Programmable GAs

(вентильные матрицы с масочным программированием или БМК), а остальные термины

уже объяснены.

Новизна темы, которой посвящена эта глава, сопровождается отсутствием

установившейся терминологии, особенно в русскоязычной литературе, где иногда одни и

те же термины обозначают разные вещи. Для некоторых терминов русские аналоги еще не

определились. Ввиду сказанного ниже используются преимущественно английские

термины и аббревиатуры, что, кстати говоря, характерно также для справочной

литературы и документации САПР.

Общее название, объединяющее совокупность ИС, рассматриваемых в этой главе, т. е.

"БИС/СБИС с программируемой (либо репрограммируемой) структурой" слишком

громоздко, поэтому для краткости будем пользоваться обозначением "СБИС ШГ (СБИС

программируемой логики), в котором не

391

разделяются понятия БИС и СБИС (для нас это разделение несущественно) и не

отражается однократность или многократность программируемости микросхемы.

Рис. 8.1. Взаимосвязь поколений СБИС программируемой логики

В разработке СБИС ПЛ участвуют уже десятки фирм, ведущими среди них являются

Xilinx, Altera, Actel, Atmel, AMD (Vantis), Lattice (все США) и некоторые другие.

Перечисленные фирмы достаточно полно представляют спектр продукции в области

СБИС ПЛ, хотя и не исчерпывают ее. Последующее изложение темы ориентировано в

основном на разработки фирм Xilinx, Altera и Actel.

Сфера применения СБИС ПЛ чрезвычайно широка, на них могут строиться не только

крупные блоки систем, но и системы в целом, включая память и процессоры. Области

применения СБИС ПЛ уточняются в дальнейшем, предварительно отметим важность

таких применений, как отработка прототипов систем при их проектировании, даже

если конечная реализация систем рассчитана на другие средства, и создание

малотиражных изделий быстрыми и эффективными способами.

СБИС ПЛ классифицируются по нескольким признакам.

392

391 :: 392 :: Содержание

392 :: 393 :: 394 :: 395 :: 396 :: 397 :: Содержание

Классификация по конструктивно-технологическому типу программируемых

элементов

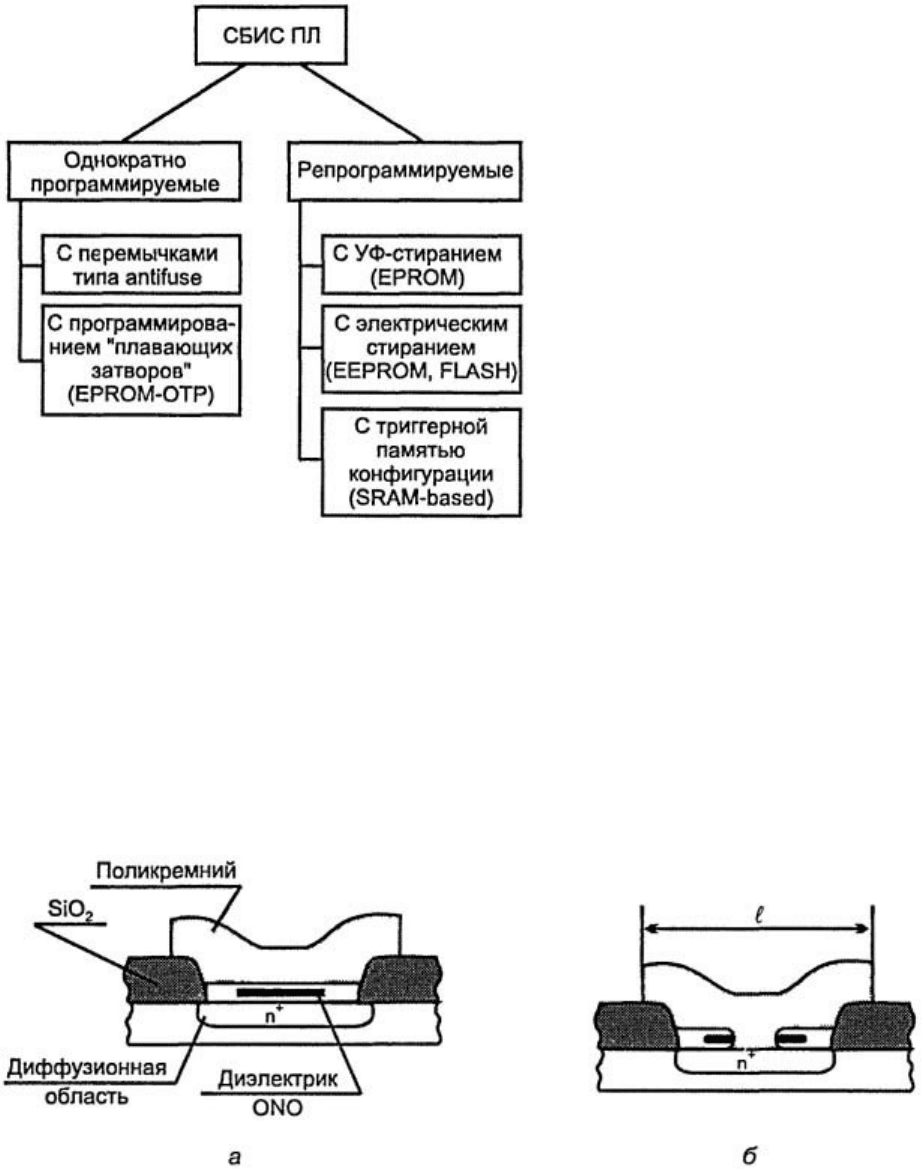

Классификация СБИС ПЛ по конструктивно-технологическому типу показана на рис. 8.2.

Программируемости, т. е. реализуемость конкретного проекта на стандартной СБИС,

обеспечивается наличием в ней множества двухполюсников, проводимость которых

может быть задана пользователем

392

либо очень малой (это соответствует разомкнутому ключу), либо достаточно большой (это

соответствует замкнутому ключу). Состояния ключей задают ту или иную конфигурацию

схеме, формируемой на кристалле. Число программируемых двухполюсников

(программируемых точек связи ПТС) в СБИС ПЛ зависит от ее сложности и может

доходить до нескольких миллионов. Для современных СБИС ПЛ характерны следующие

виды программируемых ключей:

перемычки типа antifuse (русский термин отсутствует);

ЛИЗМОП транзисторы с двойным затвором (см. рис. 4.16, б и текст к нему);

ключевые транзисторы, управляемые триггерами памяти конфигурации ("теневым"

ЗУ).

Рис. 8.2. Классификация СБИС ПЛ по типу программируемых элементов

Программирование с помощью перемычек типа antifuse является однократным.

Высококачественные перемычки фирмы Actel (рис. 8.3) компактны, имеют очень малые

токи в первоначальном (непроводящем) состоянии (около одного фемтоампера, 1 фА = 10

-

15

А).

Программирующий импульс напряжения пробивает перемычку и создает проводящий

канал из поликремния между электродами (один электрод поликремниевый, другой -

диффузионная область n

+

). Параметры обоих состояний перемычки должны сохраняться

около 40 лет.

Рис. 8.3. Программируемые перемычки типа ONO до (а) и после (б) программирования

Элементы EPROM u EEPROM (Flash) на ЛИЗМОП транзисторах с плавающим затвором

используются в схемах программируемой памяти и рассмотрены в гл. 4. Точно так же

используются они и в СБИС ПЛ. Из элементов с УФ-стиранием выделился вариант

вообще без возможности стирания данных - вариант EPROM-OTP (OTP, One Time

Programmable). Если в обычных EPROM стирание данных производится облучением

кристалла через прозрачное окошко в корпусе, то в схемах ОТР дорогостоящий корпус с

окошком заменен на дешевый без окошка, т. е. возможность стирания исключается.

Не повторяя подробностей, напомним основные свойства элементов EPROM и EEPROM.

Репрограммируемые СБИС ПЛ на основе схемотехники EPROM требуют длительного

(около часа) стирания старой конфигурации под воздействием ультрафиолетового

излучения с извлечением СБИС из устройства и ограничением числа программировании

из-за деградации свойств материалов под действием УФ-излучения.

Память конфигурации с EEPROM, стираемая электрическими сигналами, для

обновления не требует извлечения микросхемы из устройства, допускает достаточно

большое число циклов стирания (10

4

...10

6

), стирание старой и запись новой информации

занимают время порядка миллисекунд

394

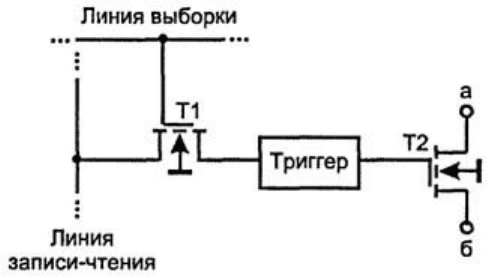

Транзисторный ключ, управляемый триггером памяти конфигурации, показан на рис. 8.4.

Ключевой транзистор Т2 замыкает или размыкает участок ab в зависимости от состояния

триггера, выход которого подключен к затвору транзистора Т2. При программировании на

линию выборки подается высокий потенциал, и транзистор Т1 включается. С линии

записи-чтения подается сигнал, устанавливающий триггер в состояние логической "1" или

"О". В рабочем режиме транзистор Т1 заперт, триггер сохраняет неизменное состояние.

Так как от триггера памяти конфигурации не требуется высокое быстродействие, он

проектируется с оптимизацией по параметрам компактности и максимальной

устойчивости стабильных состояний. Помехи в несколько вольт для такого триггера не

влияют на его состояние. Схемы с триггерной памятью конфигурации (SRAM-based)

впервые разработаны фирмой Xilinx.

Рис. 8.4. Схема ключевого транзистора, управляемого триггером памяти конфигурации

Загрузка соответствующих данных в память конфигурации программирует СБИС ПЛ.

Быстрый процесс оперативного программирования может производиться неограниченное

число раз. В СБИС ПЛ с триггерной памятью конфигурация разрушается при каждом

выключении питания. При включении питания необходим процесс программирования

(инициализации, конфигурирования) схемы - загрузка данных конфигурации из какой-либо

энергонезависимой памяти, что требует времени порядка десятков и даже сотен

миллисекунд, если речь не идет о специальных СБИС ПЛ с так называемым

динамическим оперативным репрограммированием.

Триггеры памяти конфигурации распределены по всему кристаллу СБИС вперемешку с

элементами схемы, которые они конфигурируют.

Репрограммирование СБИС ПЛ с триггерной памятью конфигурации производится в том

же режиме, что и рабочий режим, путем записи кодовой последовательности в цепочку

триггеров. Стирание информации как специфический процесс воздействия на

запоминающие элементы, требующий относительно длительных операций, вообще

устранено. Несмотря на

395

повышенную сложность запоминающего элемента и его энергозависимость в силу

указанных и других (рассматриваемых ниже) достоинств, СБИС ПЛ с триггерной памятью

конфигурации занимают важнейшее место в новых вариантах FPGA и CPLD.

. Параметры и популярные семейства СБИС программируемой логики

СБИС ПЛ характеризуются многими параметрами и их подробная классификация по

разнообразным признакам сложна и громоздка. К важнейшим параметрам относятся:

кратность программирования (однократное, многократное с ограничением числа

циклов, неограниченно многократное), определяемая типом программируемых

элементов;

уровень интеграции (максимальный уровень интеграции определяется

возможностями технологических процессов);

быстродействие (ограничивается возможностями технологических процессов);

структурная организация (FPGA, CPLD, гибкая логика со смешанной

архитектурой, схемы типа "система на одном кристалле"), в частности, наличие

или отсутствие специализированных областей встроенной памяти.

Кроме перечисленных параметров, важную роль играет и ряд других: тип базового

логического элемента, постоянство или непостоянство задержек сигналов в путях их

передачи, наличие или отсутствие интерфейса JTAG и программирования в системе ISP,

совместимости со стандартными интерфейсами (в частности, шиной PCI), уровни

питающих напряжений и режимы пониженной мощности, наличие средств

засекречивания реализованного проекта и др.

Способы оценки таких параметров, как уровень интеграции (Density) и быстродействие

(Performance) требуют пояснений.

Уровень интеграции (сложность)

Уровень интеграции СБИС ПЛ оценивается числом эквивалентных вентилей (обычно это

вентили 2И-НЕ), размещенных на кристалле. Объективная

431

оценка сложности не так проста, как может показаться на первый взгляд. Нельзя просто

подсчитать число эквивалентных вентилей в СБИС ПЛ, поскольку их в ней может даже и

не быть, а имеющиеся блоки могут не разбиваться на такие вентили.

Быстродействие СБИС

Быстродействие СБИС характеризуется либо задержкой распространения сигнала по

указанным путям (pin-to-pin, corner-to-corner, clock-to-output), либо максимально

возможной частотой работы схемы в целом (системная частота) или счетного триггера

(частота счетчика f

CNT

)- Обычно системная частота приблизительно вдвое ниже, чем

частота переключений счетного триггера. При наличии встроенного ОЗУ указывается и

цикл доступа к памяти.

Программирование в системе

Реконфигурация (программирование) в системе - одно из важнейших достоинств СБИС

ПЛ, позволяющее легко производить изменения в логике их работы. Потребности в

изменениях возникают как для устранения не выявленных при первоначальном

тестировании ошибок, так и при модернизации системы (Upgrade). Свойство

программируемости непосредственно в системе обозначается аббревиатурой ISP (In

System Programmable). Следует иметь в виду, что при реконфигурации в системе должно

сохраняться назначение внешних выводов, поскольку иначе потребуется изменить монтаж

печатных плат.

Требования к числу допустимых для микросхемы циклов репрограммирования

Эти требования зависят от решаемых задач. Для отработки прототипа, работа которого в

дальнейшем будет неизменной, достаточным может быть число циклов

репрограммирования порядка нескольких десятков, что обеспечивается даже схемами с

УФ-стиранием данных. Для многих других применений число допустимых циклов

репрограммирования должно быть существенно большим или даже практически

неограниченным.

Настройка микросхем программируемой логики

Настройка на требуемый алгоритм функционирования производится с помощью

программаторов (например, для PLD) либо непосредственно в системе, что рассмотрено

выше. Последнее характерно для СБИС ПЛ с триггерной памятью конфигурации.

Средства конфигурирования СБИС ПЛ с триггерной "теневой" памятью позволяют

загружать ее от внешней памяти различными способами. Данные для конфигурирования

могут поступать от разных источников (компьютера, ПЗУ, других СБИС ПЛ), форма их

представления может быть последовательной или параллельной, роль конфигурируемой

СБИС может быть активной или пассивной. В результате возникают несколько

возможных режимов конфигурирования.

СБИС ПЛ, имеющие интерфейс JTAG, могут конфигурироваться с его использованием

(расширенный интерфейс JTAG).

§ 8.2. Программируемые пользователем вентильные матрицы (FPGA)

Программируемые пользователем вентильные матрицы (ППВМ или FPGA)

топологически сходны с канальными БМК. В их внутренней области размещается

множество регулярно расположенных идентичных конфигурируемых логических блоков

(КЛБ), между которыми проходят трассировочные каналы, а на периферии кристалла

расположены блоки ввода/вывода (БВВ или ЮВ, Input/Output Blocks). Таким образом,

архитектуру ППВМ можно представить рисунком, подобным рис. 7.21, а, д, если вместо

наименования "базовая ячейка" иметь в виду наименование КЛБ, а вместо "периферийной

ячейки" - БВВ.

397

К наиболее известным FPGA относятся БИС/СБИС семейств ХС2000, ХСЗООО, ХС4000,

ХС5000 и Spartan фирмы Хilinх, которая в 1985 г. впервые выпустила FPGA с триггерной

памятью конфигурации. Среди FPGA с перемычками типа antifuse следует отметить

семейства АСТ1, 1200XL, ACTS, 3200DX фирмы Actel, используемые, в частности, в

космической аппаратуре США.

Свойства и возможности FPGA зависят в первую очередь от характера их КЛБ и

системы межсоединений.

Логические блоки FPGA

В качестве КЛБ (далее для краткости просто ЛБ - логические блоки) используются:

транзисторные пары, простые логические вентили И-НЕ, ИЛИ-НЕ и т. п. Такие ЛБ

называют SLC - Simple Logic Cells;

логические модули на основе мультиплексоров;

логические модули на основе программируемых ПЗУ, такие ЛБ называют LUTs -

Look-Up Tables.

Важной характеристикой Л Б является их "зернистость" (Granularity). Другой важной

характеристикой считается "функциональность" (Functionality).

Первое свойство связано с тем, насколько "мелкими" будут те части, из которых можно

"собирать" нужные схемы, второе - с тем, насколько велики логические возможности Л Б.

Мелкозернистость ЛБ ведет к большей гибкости их использования, возможностям

реализовать воспроизводимые функции разными способами, получая разные варианты в

координатах "площадь кристалла - быстродействие". В то же время мелкозернистость ЛБ

усложняет систему межсоединений FPGA в связи с большим числом программируемых

точек связи.

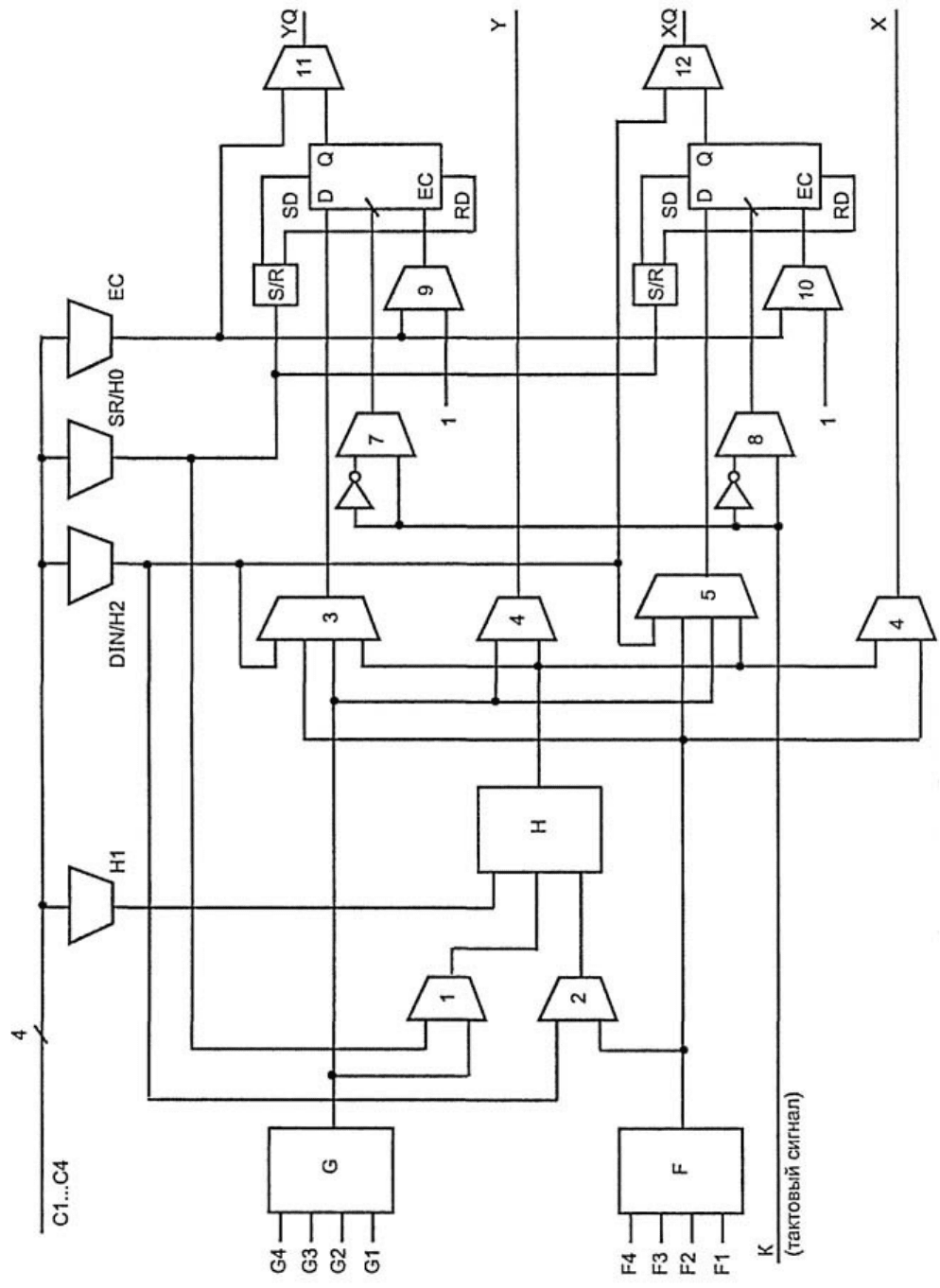

Крупнозернистый блок семейства ХС4000Е (рис. 8.7) в качестве основы имеет три

табличных функциональных логических преобразователя G, F и Н, а также ряд

программируемых мультиплексоров (отмечены номерами 1...12 или надписями у

выходов) и два триггера.

В FPGA с триггерной памятью реконфигурации, как правило, применяют

крупнозернистые блоки. В таких блоках реализуются более сложные функции, что ведет к

упрощению программируемой части межсоединений. В то же время труднее полностью

использовать логические элементы блоков, что ведет к потерям площади кристалла и

быстродействия. Иными словами, меняя зернистость, можно выиграть в одном и

проиграть в другом.

400

Ркс. 8.7. Схема логического блока FPGA XC4000E

401

Табличные преобразователи представляют собой ППЗУ, для которых аргументы

логической функции служат адресом (см. §4.5). Воспроизводятся любые функции числа

аргументов п при организации памяти 2

n

× 1. Число воспроизводимых функций, т. е. число

возможных вариантов программирования ЗУ, составляет 2

2 n

. Логические преобразователи

G и F (блоки памяти с организацией 16 × 1) воспроизводят функции 4-х аргументов. Их

выходные сигналы могут непосредственно передаваться на выходы Y и X при

соответствующем программировании мультиплексоров 4 и 6, либо использоваться иным

образом. Через мультиплексоры 1 и 2 выходы преобразователей G и F могут быть поданы

на входы преобразователя Н, если мультиплексоры запрограммированы на передачу

сигналов от нижних входов. Кроме того, преобразователь Н может использоваться как

третий независимый генератор функций со входами Н0, H1 и Н2, если мультиплексоры 1

и 2 запрограммированы иначе. Входной сигнал H1 может добавляться как

дополнительный аргумент и при подаче на преобразователь Н выходов преобразователей

G и F.

При подаче выходных сигналов преобразователей G и F на вход преобразователя Н он

воспроизводит функции большего, чем 4 числа аргументов (от 5 до 9, причем для 5

аргументов воспроизводятся любые функции, а для 6...9 лишь некоторые).

В зависимости от программирования мультиплексоров 3 и 5, триггеры принимают данные

от логических преобразователей или внешнего входа DIN. Сигналы К тактирования

триггеров поступают от общего входа через мультиплексоры 7 и 8, программирование

которых позволяет индивидуально изменять полярность фронта, тактирующего триггеры.

Сигнал разрешения тактирования ЕС также поступает от общего входа, но, благодаря

мультиплексорам 9 и 10, можно либо использовать сигнал разрешения, либо постоянно

разрешить тактирование. Триггеры имеют асинхронные входы установки и сброса (SD -

Set Direct и RD - Reset Direct), один из которых через программируемый селектор S/R

может быть подключен к выходу коммутатора SR, который, в свою очередь, может

программироваться для подключения к любому из внешних выводов ЛБ С1...С4. Это же

возможно и для других выходов коммутаторов верхней строки рис. 8.7.

В специальных режимах блоки G и F функционируют как обычные ОЗУ, способные

хранить 32 бита данных. Возможна реализация двухпортовых ОЗУ, буферов FIFO и т. д.

Память распределена по всему кристаллу.

Блоки ввода/вывода FPGA

Характерные черты блока ввода/вывода рассмотрим на примере семейств ХС4000,

ХС4000Е (рис. 8.8). Блок имеет два канала - для ввода сигналов и для вывода. В каждом

канале сигналы могут передаваться прямым путем

402

или фиксироваться в триггерах в зависимости от программирования мультиплексоров 7 и

4. При переводе буфера 1 в третье состояние выходной контакт не должен оставаться

разомкнутым, т. к. на "плавающем" высокоомном входе элементов типа КМОП может

накапливаться любой заряд, что может имитировать ввод в схему непредусмотренных

сигналов.