Курсовая работа - Технические средства автоматизации

Подождите немного. Документ загружается.

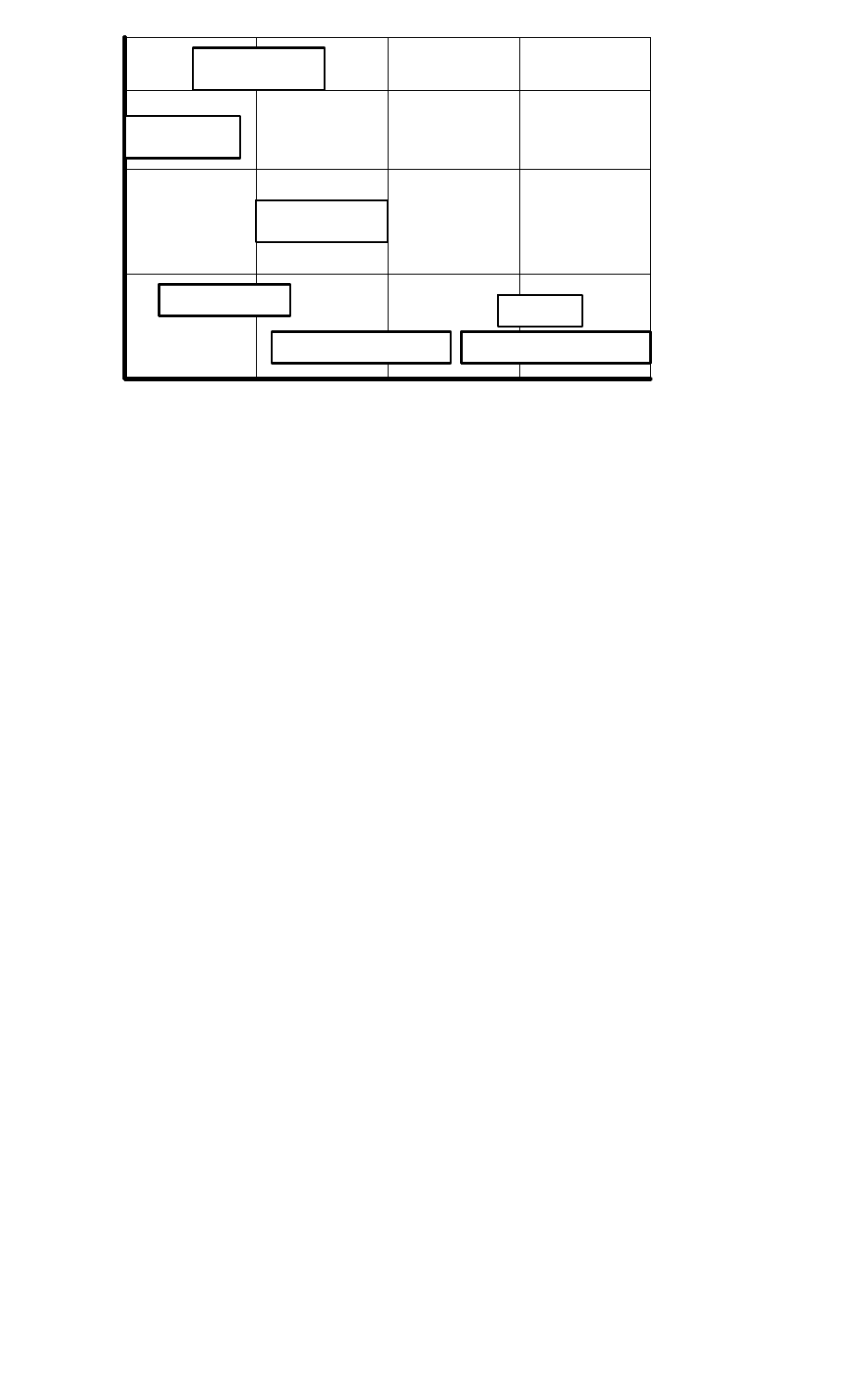

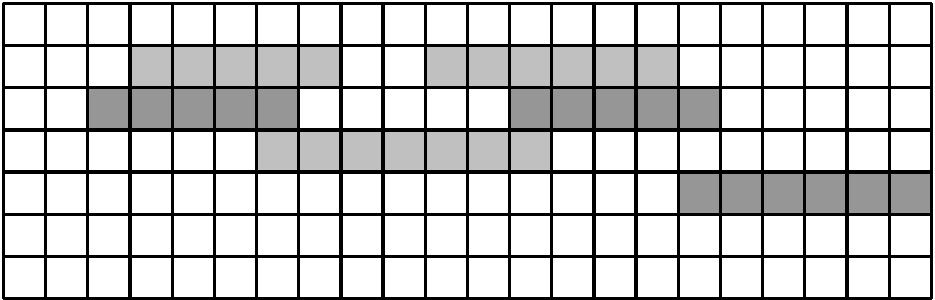

1965 1970 1975 1980 1985

0

40

80

Эпотр.

н Дж

МТТЛ

СТТЛ

ТТЛШ

МмТТЛ

МмТТЛШ FAST, ALS

AS

Рис. 5 Этапы развития ТТЛ. (СТЛ) – среднего быстродействия;

МТТЛ-мощные;

МмТТЛ-маломощные;

ТТЛШ-с переход Шотки;

AS-перспективные сверхскоростые с перехом Шотки;

FAST- компромиссные между AS и ALS

Быстродействие самых разных по схемотехнике цифровых микросхем принято

сравнивать по так называемому времени задержки распространения сигнала

t

ЗД. Р.

т.е. по интервалу времени от подачи входного импульса до появления

выходного.

Если принять во внимание потребляемую элементом мощность P

пот.

, то можно

подсчитать энергию, необходимую этому цифровому элементу для переноса

одного бита информации Э

пот.

=t

зд. р.

* P

пот.

. По диаграмме рис.5 можно

определить, что за двадцатилетие энергия Э

пот.

, затрачиваемая в элементе

ТТЛ, была уменьшена с 120…140 до 5…20мДж, т.е. примерно на полтора

порядка. Основная часть этой экономии получена в результате многократного

уменьшения времени t

зд.р.

. Одновременно путем усовершенствования

технологических методов изготовления полупроводниковых структур удалось

снизить в 2 – 3 раза и потребляемую мощность P

пот.

Интересно, что теоретически наименьшая энергия переноса единицы

информации равна произведению kT. Здесь к - постоянная Больцмана, T -

абсолютная температура. Произведение кТ~ это энергия элементарного шу-

мового выброса. Для T = 300 К Э

пот.

= кТ = 1,38 *10

-23

х 300 = 4 * 10

-9

мДж. Та-

ким образом, современные микросхемы, а следовательно, и ЭВМ, построен-

ные на этой элементной базе, потребляют энергию, на девять порядков

11

большую по сравнению с теоретическим пределом. Эту «энергетическую

пропасть» полезно, однако, сравнить с результатом развития, отображенным

на диаграмме (рис. 5): может быть, к теоретическому пределу Э

пот.

=kT удастся

приблизиться через 120 лет?

Сейчас в блоках аппаратуры можно встретить все перечисленные варианты

микросхем ТТЛ. Напряжение питания у них одинаковые U

и.п.

=5В±10%,

а входные и выходные логические уровни совместимы. Микросхемы ТТЛ

более новых серий имеют улучшенные электрические параметры, но

расположение их выводов (т. е. цоколевка) остается прежним. Полная

электрическая и конструктивная совместимость однотипных микросхем ТТЛ

из разных серий снимает многие проблемы развития и улучшения

параметров аппаратуры и стимулирует наращивание степени внутренней ин-

теграции вновь выпускаемых микросхем, когда на одном кристалле размеща-

ется все большее число функциональных узлов, многие из которых ранее бы-

ли самостоятельными микросхемами.

Основная номенклатура применяемых сейчас микросхем ТТЛ имеет средний

уровень интеграции. Советуем читателям самостоятельно подсчитать

(естественно, приблизительно) число транзисторов в микросхеме, например

регистра. На кристалле микросхемы такой сложности располагается 1000 и

более транзисторов.

Сейчас все более доступными становятся большие интегральные схемы (БИС).

Это микропроцессоры, котроллеры к ним, запоминающие устройства,

программируемые логические матрицы и многое другое. Число транзисторов в

БИС приближается к 100•000. Микропроцессорная сверхбольшая интегральная

микросхема (СБИС) имеет 350•000 транзисторов при числе разрядов

процессора 32. Все же для решения аппаратурных задач небольшого обьема

и для сохранения местных, локальных узлов в так называемой цифровой

среде, состоящей из многих БИС, требуется и простые микросхемы.

Анализируя работу микросхем в цифровой аппаратуре, можно условно

определить, что до 20% из них должны работать с предельными скоростями во

входных устройствах приема данных, а примерно 60% - с умеренными в

обрабатывающей, т.е. процессорной части. Остальные микросхемы могут быть

низкоскоростными, экономичными. Они работают в индикаторных и

регистрирующих устройствах. В общих чертах это отношение существует и

между объемами выпуска быстродействующих, стандартных и

низкоскоростных микросхем ТТЛ.

12

Исходная схема элемента ТТЛ 60-х годов оказалась пригодной для масштабного

моделирования: номиналы резисторов в ней можно было увеличивать или

уменьшать в определенное число раз. Этим приемом пропорционально

изменяют как быстродействие, так и потребляемую мощность для микросхем

разных серий. Существенные изменения в схему логического элемента были

внесены лишь на этапе внедрения структур Шотки. В 80-е годы см. рис. 5

энергию Э

пот.

Старались снизить путем постепенного уменьшения объема

интегрального транзистора.

2.2 РАСЧЕТННАЯ ЧАСТЬ

2.2.1 СОСТАВЛЕНИЕ МИНИМИЗИРОВАННОГО ЛОГИЧЕСКОГО ВЫРАЖЕНИЯ

ДЛЯ ФОРМИРОВАНИЯ ВЫХОДНОГО СИГНАЛА (Е)

13

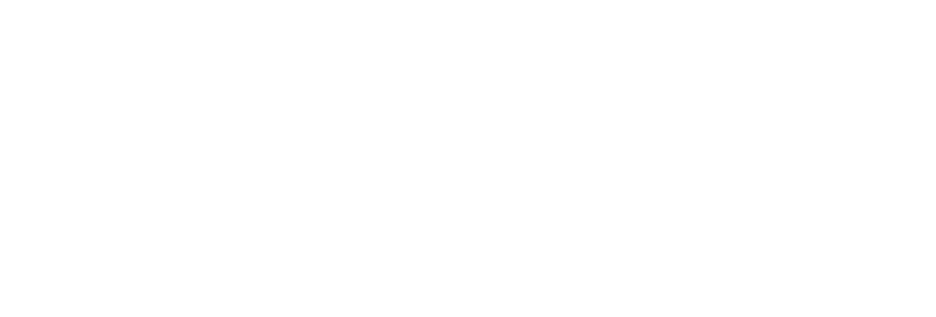

Таблица истинности задания. Таблица 1

а 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

b 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

с 0 0 0 0 1 1

1

1 0 0 0 0 1 1 1 1

d 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

Е

0 0 0 1 1 1 0 1 0 0 0 0 0 1 X 1

а=x

1

; b=x

2

; c=x

3

; d=x

4

;

Запишем функцию в форме СНДФ

4321

43

2

1

4

321

4

3

2

1

4

3

2143

21

43216

43

2

15

4

3214

4

3

2

13

4

3

21

2

43

211

xxxx

xxxxxxxxxxxxxxxxxxxxy

xxxxa

xxxxa

xxxxa

xxxxa

xxxxa

xxxxа

k

k

k

k

k

к

Используем распределительный закон:

cbacbca

xxxxxxx )(

и соотношение:

1 xx

Упростим схему:

431

4

3

24

21

xy xxxxxxxx

dcadcbdbaf

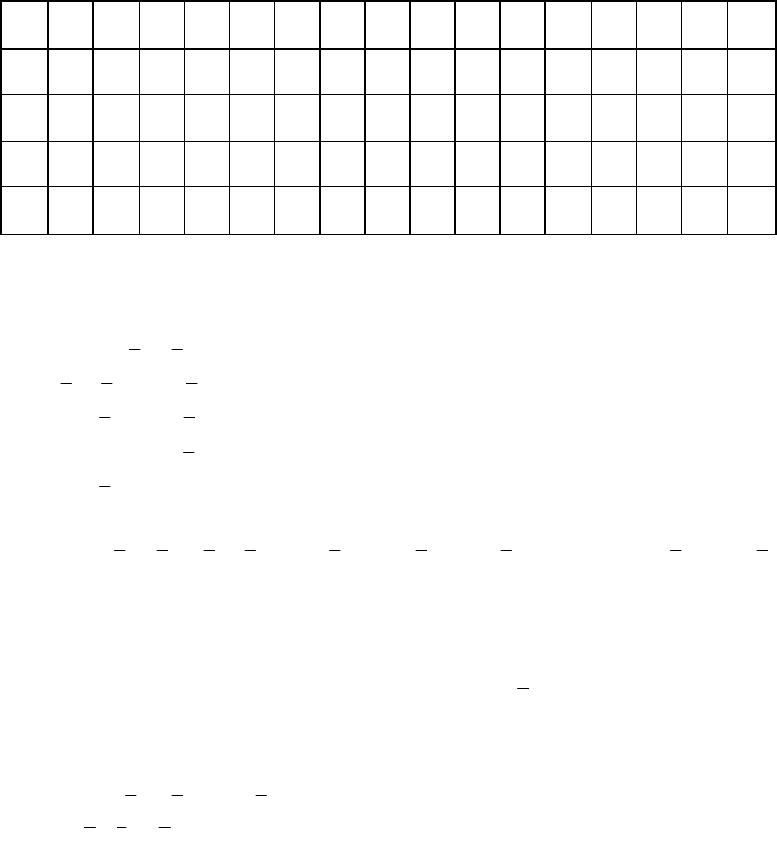

2.2.2.1 РАЗРАБОТКА ФУНКЦИОНАЛЬНОЙ СХЕМЫ ДЛЯ ФОРМИРОВАНИЯ

ВЫХОДНЫХ СИГНАЛОВ (А,В,С,D)

Для разработки принципиальной схемы нам необходимо составить

функциональную схему.

Функциональная схема будет составлять из трех основных блоков:

14

1. генератора импульсов

2. распределитель импульсов

3. кодер сигнала

Генератор

импульсов

Распределитель

импульсов

Кодер

сигнала

Ручное

управление

Исполнительное

устройство А

Исполнительное

устройство В

Исполнительное

устройство С

Исполнительное

устройство D

Рис. 6 Функциональная схема для формирования логических сигналов А,В,С,D

2.2.2.2 РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ ДЛЯ ФОРМИРОВАНИЯ

ВЫХОДНЫХ СИГНАЛОВ А, В, С, D

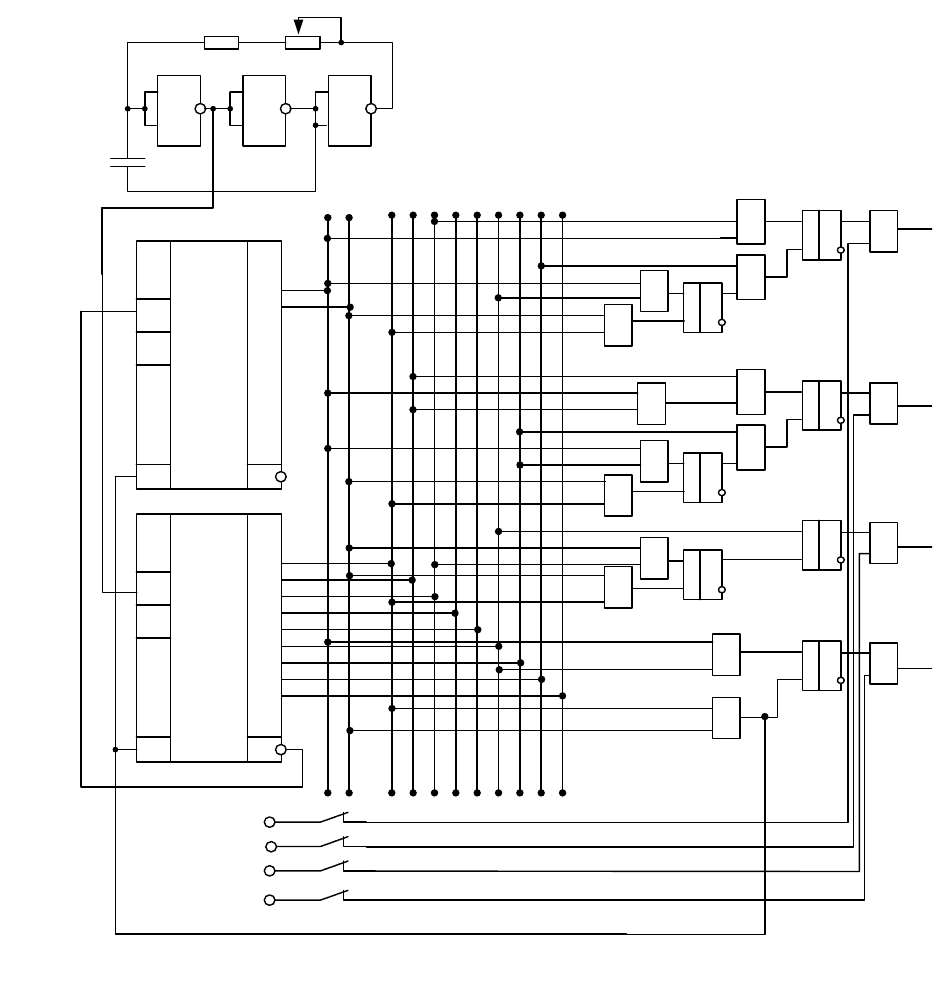

При разработке следует учитывать элементную базу, на которой рекомендовано

построение схемы и особенности входных устройств.

Составим циклограмму заданий:

Таблица 2

15

A

B

C

D

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21

Для составления принципиальной схемы автомата сформируем для каждого

отдельного выходного сигнала свою схему. Затем произведем координацию

взаимосвязанных параметров.

Поскольку время тактового импульса в задании не указано, применим схему

традиционного мультивибратора на трех инверторах. Таковыми могут быть как

простые логические элементы «НЕ» и «И-НЕ». Наибольшей устойчивостью в

работе отличаются элементы «И-НЕ», поэтому применим их в нашей схеме.

Для организации счета циклов можно установить двоичный счетчик, считывающий

импульсы мультивибратора. Для облегчения поиска нужного двоичного кода

можно применить дешифратор двоичного кода в десятичный. Для серии К561

это микросхемы К561ИЕ8 или К1561ИЕ8 – реверсивный счетчик импульсов со

встроенным дешифратором. Применим два счетчика , так как число циклов

превышает декаду. Второй счетчик импульсов применим в качестве счетчика

старших разрядов от 10 до 99. Согласование счетчиков осуществим, используя

выход переполнения младшего разряда DD

3

, соединив его со счетным входом

счетчика старшего разряда DD

2

.

Для синхронного обнуления счетчиков их входы R доедим вместе и подключим к

элементу, имеющему признак окончания последнего цикла задания.

Состояние входов А,В,С,D определяется не просто появление на этих выходах

кратковременной логической единицей. Это состояние следует удерживать

определенное число циклов. Окончание цикла должно бать зафиксировано

появление логического нуля и исключение ложного срабатывания,

вызывающего появления произвольное состояния. Сложность поставленной

задачи заключается еще и в том, что логические состояния должно появляться

еще и при других номерах циклов. Так же в схеме предусмотрен ручной

режим, т.е. имеются кнопки, которые обладают приоритетом. При нормальном

состоянии их выхода активны. Для осуществления данного режима применим

16

RS-триггеры с согласующими входными элементами в виде элементов ИЛИ и

И .

Рис. 7 Принципиальная схема формирования сигналов А,В,С,D

& & &

R1

R2

C

0

1

2

3

4

5

6

7

8

9

P

+1

-1

R

CT

2\

10

DC

1020

1 2

3

4

5

6

7

8

9

0

1

2

3

4

5

6

7

8

9

P

+1

-1

R

CT

2\

10

DC

1

A

B

C

D

A

B

C

D

S

R

T

1

S

R

T

&

&

&

1

S

R

T

1

S

R

T

&

&

&

&

S

R

T

S

R

T

&

&

&

S

R

T

&

&

&

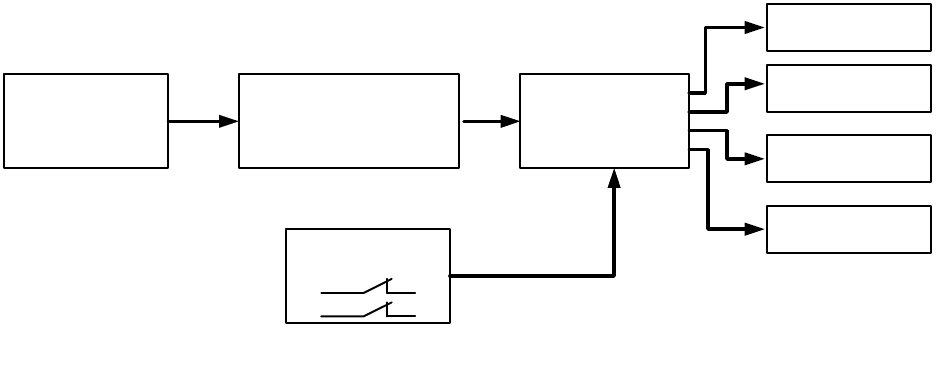

2.2.3 РАЗРАБОТКА ФУНКЦИОНАЛЬНОЙ И ПРИНЦИПИАЛЬНОЙ СХЕМ ДЛЯ

ФОРМИРОВАНИЯ ВЫХОДНОГО СИГНАЛА F НОМЕРА ЗАЧЕТНОЙ КНИЖКИ

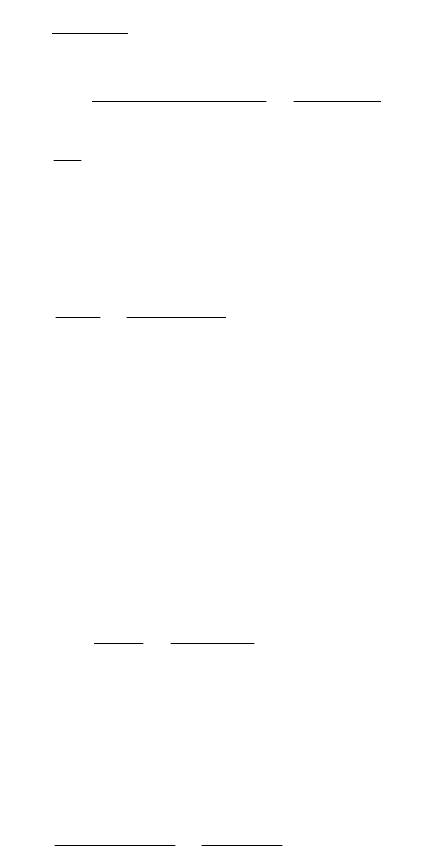

Семисигментный индикатор должен показать последнею цифру номера зачетной

книжки. В моем случае это номер 1.

17

Согласно задания сигнал Fдолжен появиться в момент появления сигнала Е, а

исчезает, если число включений сигнала Е сравнятся с числом 14.

Для решения данной задачи примем схему, состоящею из двух двоично-

десятичных счетчиков со встроенным дешифраторами. На транзистором ключе

соберем схему для высвечивания индикатора без дешифратора. Поскольку

индикатор АЛС333А имеет общий катод, соединим с корпусом схемы, а на

аноды соответствующих сегментов подадим плюс через эмиттер

транзисторного ключа, собранного на транзисторе VT

2.

Для включения

индикатора применим асинхронный RS-триггер. Для выключения индикатора

применим конъюнктор, поскольку номер отключающего импульса –

двухразрядное число.

Произведем расчет транзисторного ключа:

Согласно задания семисегментный индикатор имеет параметры, приведенные в

таблице 3 Таблица 3

Тип индикатора Параметры индикатора (прямое падение напряжения;

постоянный прямой ток через один сигмент)

1. АЛС333А Общий катод; U

прям.

=2.0В; I

прям.

=25мА

Для формирования цифры 1 необходимо включить 2 сегмента из семи.

Определим общий ток индикатора:

I

общ. инд.

= I

к. раб.

= n*I

сег.

=2*25=50мА

Для нормальной работы транзистора в режиме ключа необходим ток в 100мА.

Следовательно, общий ток коллектора транзистора должен быть примерно в

двое больше, чем ток нагрузки.

В справочнике Р. М. Терещук, Н.М. Терещук «Полупроводниковые приемно-

усилительные устройства» Справочник радиолюбителя, выбираем транзистор

КТ633А с параметрами, удовлетворяющими требованиям по току и

напряжению.

Тип транзистора h

21 э. min

– h

21 э. max.

I

к. max.

мA U

кэ. max.

B

КТ633А 40 - 140 200 15

Найдем сопротивление базы транзистора, учитывая его коэффициент усиления.

Известно, что ток коллектора транзистора:

бэ..ср. 21

Ih

к

I

отсюда ток базы транзистора

18

мАI

h

б

э

56.0

90

50

90

2

14040

2

h

h

;

h

I

I

max..2121э1э.min

э.ср. 21

ср. 21э1

нагрузки

б

Для получения такого базового тока при уровне логической единицы на входе

(8.6В) необходим резистор R

2

кОм

U

R

лог

1414057

1056.0

6.8

I

3

б

2

Резистор R

3

можно рассчитать зная полное сопротивление светодиодных

элементов.

В таблице данных светодиода указано, что падение напряжения на элементах

светодиодного сегмента должно быть не больше 1.2 В.

Сопротивление системы сегментов:

ОмR

сегм

24

1050

2.1

I

U

3

сигм.

.

Для сопротивления коллектора, выполняющего роль ограничителя коллекторного

тока, можно найти значение R

3

Ом

E

R

пит

216

1050

2.112

I

U

3

инд. общ.

инд..

3

Выберем из стандартного ряда сопротивлений R

3

= 220Ом

ПРИНЦИПИАЛЬНАЯ СХЕМА ДЛЯ ФОРМИРОВАНИЯ СИГНАЛА F

Согласно задания сигнал F должен появиться в момент появления сигнала Е, а

исчезает, если число включений сигнала Е сравнятся с числом 14.

Можно реализовать эту схему на асинхронном RS-триггере. Поскольку входное

число 1 – одноразрядное, а выключающее 14 – двухразрядное число,

установим на вход R подключенный через два счетчика импульсов сигнала Е,

установленный на выходе дешифратора.

Поскольку интегральные микросхемы одинаковой серии согласованны между

собой, т.е. имеют одинаковые входные и выходные сопротивления, то

необходимость в согласовании элементов отпадает.

Но сложность задания заключается в том, что сигнал F должен запустить

светодиодную сборку AЛС333А, которая имеет общий катод. Поскольку

необходимо высветить последнюю цифру зачетной книжки, соответствующую

19

1, применять дешифратор в нашем случае нет смысла. Поэтому подключим

общую ножку катода на корпус схемы, объедим между собой аноды

светодиодов в одно единое соединение и подключим его к эмиттеру

транзистора.

Рис. 8 Формирование сигнала F

R2

VT3

+12B

F

R3

0

1

2

3

4

5

6

7

8

9

P

+1

-1

R

CT

2\10

DC

0

1

2

3

4

5

6

7

8

9

P

+1

-1

R

CT

2\10

DC

S

R

T

&

1

E

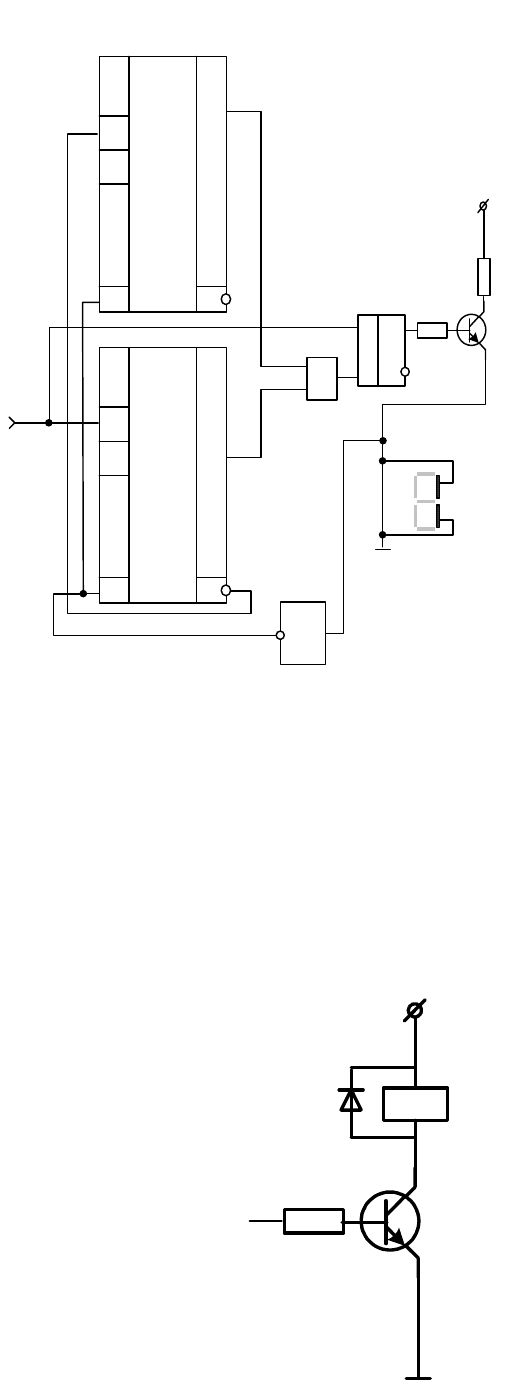

2.2.4 РАСЧЕТ И ВЫБОР ЭЛЕМЕНТОВ

ВЫХОДНЫХ УСО

(устройство

согласования с

объектом) С ВЫХОДНЫМИ

СИГНАЛАМИ

20

Рис.9 Выходное устройство

согласования

R2

+12B

геркон

VT1

VD1