Козвонина Е.Г. Сборник задач. Основы цифровой схемотехники

Подождите немного. Документ загружается.

21

A

B

C

1

1

1

&

&

X

0

F2

1

1

1

&

&

X

1

F3

F1

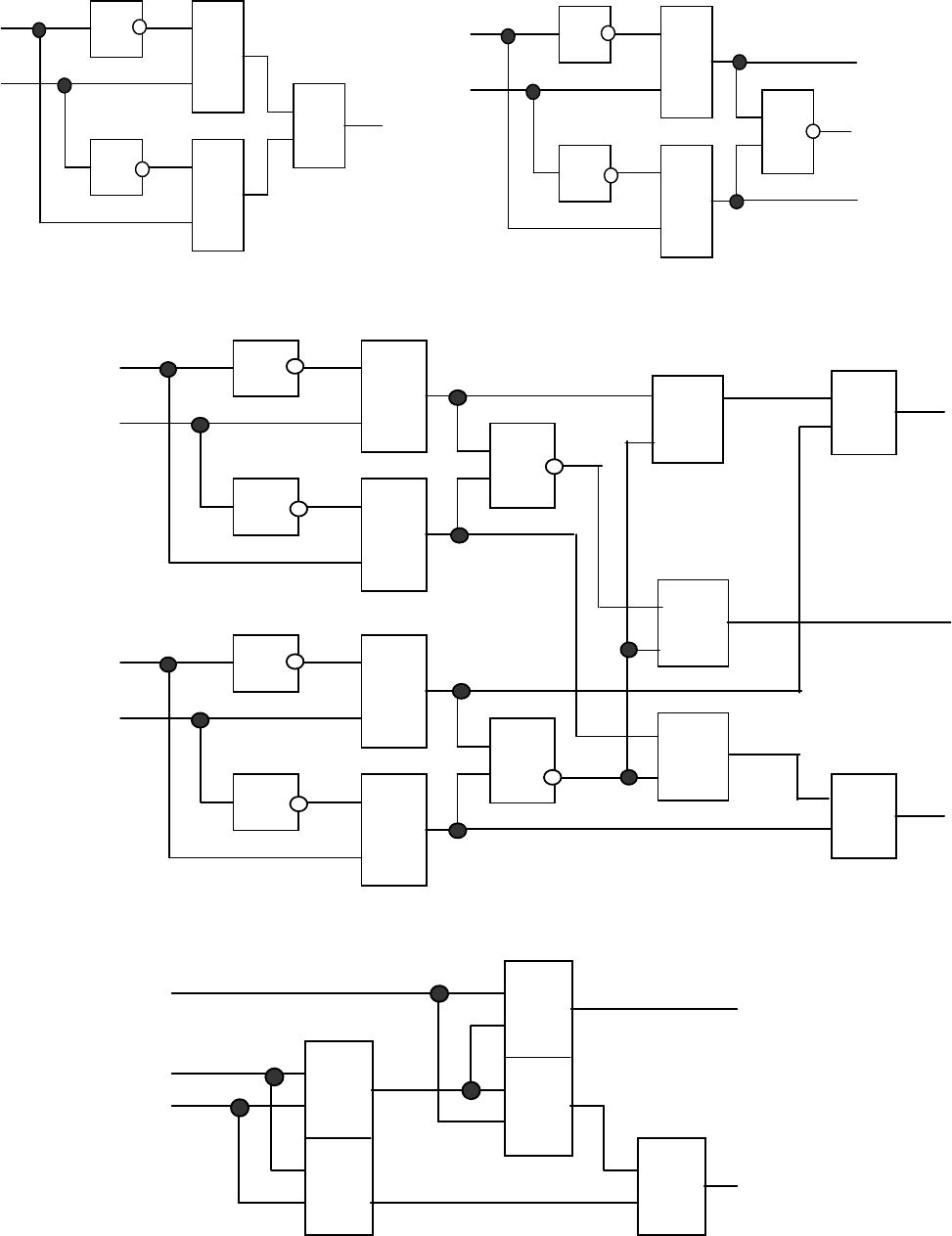

Рис.2.2.13 Рис.2.2.14

1

1

1

&

&

X

X

0

F2

1

1

1

&

&

1

F3

F1

Y

Y

0

1

&

1

&

&

1

Рис.2.2.15

С0

А

В

=1

&

=1

1

&

S

C1

Рис.2.2.16

22

С 0

А 0

В 0

=1

=1

1

&

&

S0

А 1

В 1

=1

=1

1

&

&

S1

C2

Рис.2.2.17

=1

=1

=1 =1

Ри

с.

2

.

2

.

1

8

23

=1

=1

=1

X4

Y4

Y3

Y2

Y1

=1

=1

=1

X3

X2

X1

Y1

Y2

Y3

Y4

X4

Рис.2.2.19 Рис.2.2.20

1

1

Q

Q

R

S

&

R

S Q

Q

&

Рис.2.2.21 Рис.2.2.22

X1

X2

X3

&

&

Q

Q

R

S

&

&

С

&

&

D

Q

Q

&

&

С

1

Рис.2.2.23 Рис.2.2.24

24

3.ТИПОВЫЕ КОМБИНАЦИОННЫЕ УСТРОЙСТВА

3.1. СПРАВОЧНЫЕ СВЕДЕНИЯ ОБ ИС КОМБИНАЦИОННЫХ

УСТРОЙСТВ

Комбинационные устройства (автоматы без памяти) характеризуются

отсутствием в их составе элементов памяти в виде триггеров. Это означает, что

сигналы на выходах этих устройств в любой момент времени однозначно

определяются сочетанием сигналов на входах в этот же момент времени и не

зависят от сигналов, действовавших в предыдущие моменты времени.

Простейшие комбинационные устройства, реализованные на отдельных

логических элементах, рассмотрены в предыдущем разделе. В цифровой

схемотехнике при построении более сложных устройств применяются

комбинационные устройства в виде типовых структур, выполненных как

самостоятельные ИС. Эти ИС образуют следующую функциональную группу ИС

ТТЛ серии К155. В нее входят дешифраторы, шифраторы, мультиплексоры,

сумматоры и другие устройства. Краткое описание некоторых из них приведено

ниже.

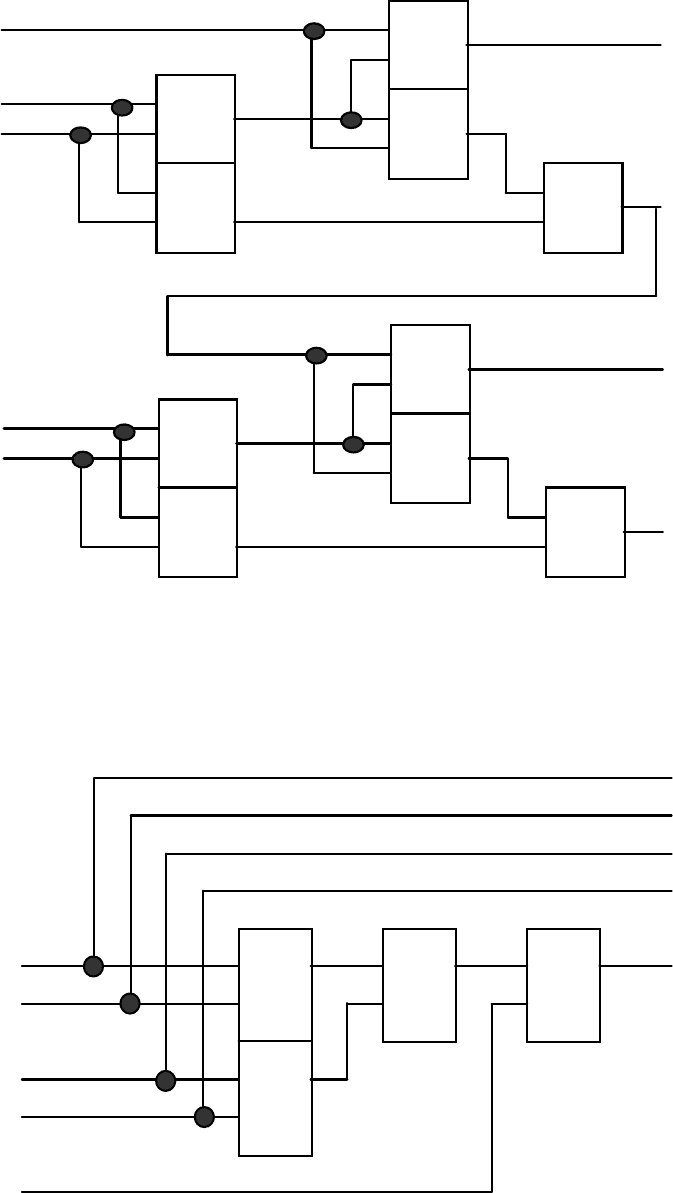

3.1.1.Дешифраторы–демультиплексоры

Дешифраторы, выполненные в виде самостоятельных микросхем, строятся

аналогично схемам, приведенным в предыдущем разделе на рис.2.2.1-2.2.5, и

различаются числом информационных входов и наличием или отсутствием входа

(входов) стробирования. Выходы у большинства ИС дешифраторов выполнятся

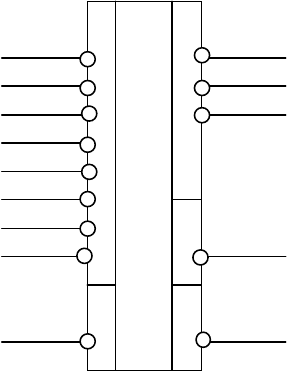

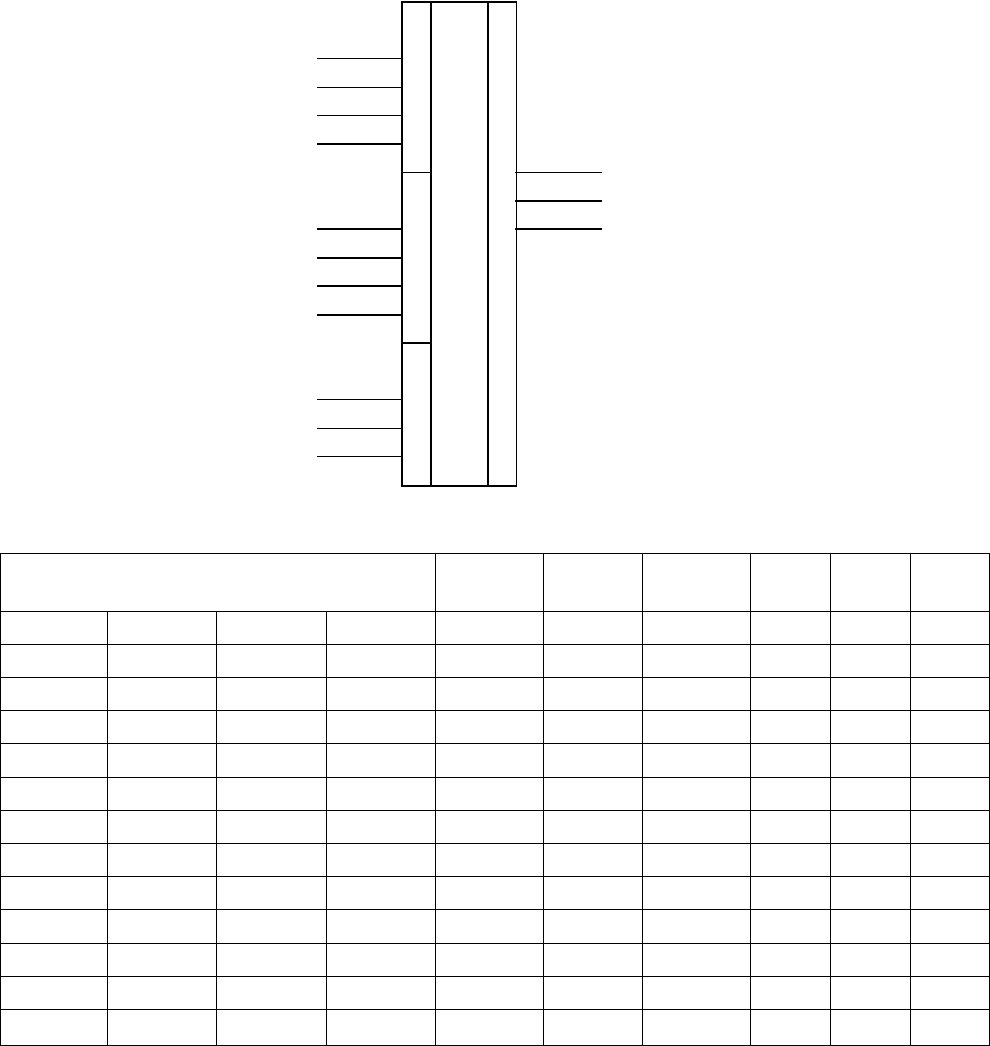

инверсными. Микросхема К155ИД3 (рис.3.1.1) служит для преобразования

четырехразрядного двоичного кода в код «1 из 16», т.е. размерность дешифратора

4*16. Микросхема имеет четыре информационных входа DI1, DI2, DI4, DI8, два

инверсных входа стробирования Е1 и Е2, объединенных по логическому И, и 16

инверсных выходов DO0 – DO15. В зависимости от способа включения ИС может

работать как дешифратор и как демультиплексор.

Микросхема К155ИД4 (рис.3.1.2) содержит в одном корпусе два

23

22

21

20

18

19

1

2

3

4

5

6

7

8

9

10

11

13

14

15

16

17

DI

1

2

4

8

DO

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

&

E1

E2

DC/

DMX

ИД3

15

14

7

6

5

4

9

10

11

12

DI

1

2

DO

00

01

02

03

DO

10

11

12

13

&

G1

G2

DC/

DMX

ИД4

&

E1

E2

1

2

13

3

Рис.3.1.1 Рис.3.1.2

25

дешифратора–демультиплексора каждый размерностью 2*4. Каждая секция имеет

по два объединенных по логическому И входа стробирования и по четыре

инверсных выхода DO0 – DO3. Информационные входы DI1 и DI2 – общие для

обеих секций, т.е. объединены внутри микросхемы. Различие между секциями

состоит в том, что у одной из них оба стробирующих входа являются инверсными

(G1,G2), а у второй – один прямой (Е2), а другой инверсный (Е1). В зависимости

от схемы включения ИС может быть использована в следующих режимах: два

дешифратора 2*4, один дешифратор 3*8, два демультиплексора 1:4, один

демультиплексор 1:8. При использовании К155ИД4 следует обращать внимание

на то, что выходы у этой ИС с открытым коллектором.

3.1.2. Шифраторы

Шифраторы, выполненные в виде самостоятельных микросхем, чаще всего

бывают приоритетными и строятся по схемам, аналогичным рис.2.2.6 – 2.2.9,

отличаясь числом информационных входов, входов стробирования, наличием или

отсутствием помимо информационных дополнительных служебных выходов,

обеспечивающих возможность наращивания разрядности, а также характером

сигналов (прямые или инверсные) на всех названных входах и выходах.

Микросхема К155ИВ1 (рис.3.1.3) представляет собой приоритетный

шифратор 8:3, имеющий восемь инверсных информационных входов I0-I7;

инверсный вход стробирования E; три инверсных информационных выхода A0-

A2; инверсный выход G, сигнал на котором (0) свидетельствует о наличии хотя

бы на одном из информационных входов активного уровня (0) при наличии

разрешающего уровня (0) на входе стробирования E; инверсный выход EO,

сигнал на котором (0) свидетельствует об отсутствии хотя бы на одном из

информационных входов активного уровня (0) при наличии разрешающего

уровня (0) на входе стробирования E. Выход G может быть использован для

разрешения работы последующих узлов, для которых выходной код шифратора

является входным. Выход ЕО используется при наращивании разрядности

шифраторов, разрешая или запрещая работу младших микросхем и сохраняя тем

10

11

12

13

1

2

3

4

I

0

1

2

3

4

5

6

7

5

E

A

0

1

2

9

7

6

G

EO

14

15

PR

CD

ИВ1

Рис.3.1.3

26

самым приоритетность схемы. Эти свойства ИС К155ИВ1 отражены в таблице

истинности (табл.3.1.1).

Таблица 3.1.1

E I7 I6 I5 I4 I3 I2 I1 I0 A2 A1 A0 G EO

1 * * * * * * * * 1 1 1 1 1

0 1 1 1 1 1 1 1 1 1 1 1 1 0

0 1 1 1 1 1 1 1 0 1 1 1 0 1

0 1 1 1 1 1 1 0 * 1 1 0 0 1

0 1 1 1 1 1 0 * * 1 0 1 0 1

0 1 1 1 1 0 * * * 1 0 0 0 1

0 1 1 1 0 * * * * 0 1 1 0 1

0 1 1 0 * * * * * 0 1 0 0 1

0 1 0 * * * * * * 0 0 1 0 1

0 0 * * * * * * * 0 0 0 0 1

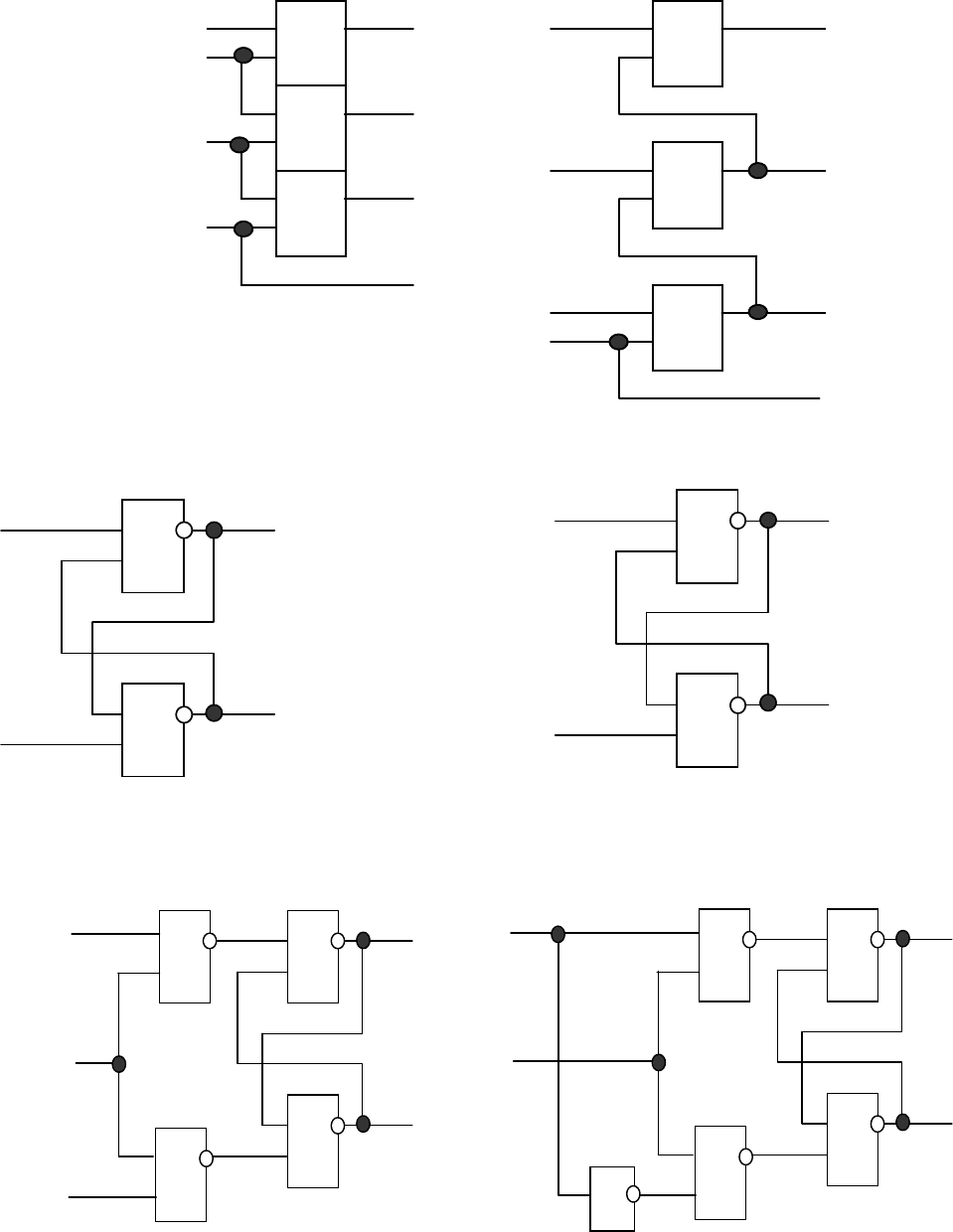

3.1.3. Мультиплексоры

Мультиплексоры, выполненные в виде самостоятельных микросхем, строятся

аналогично схемам, показанным на рис.2.1.10 – 2.1.12, и различаются числом

информационных и селектирующих входов, наличием или отсутствием входа

(входов) стробирования, а также характером выходных сигналов, которые могут

быть прямыми или (и) инверсными относительно входных информационных.

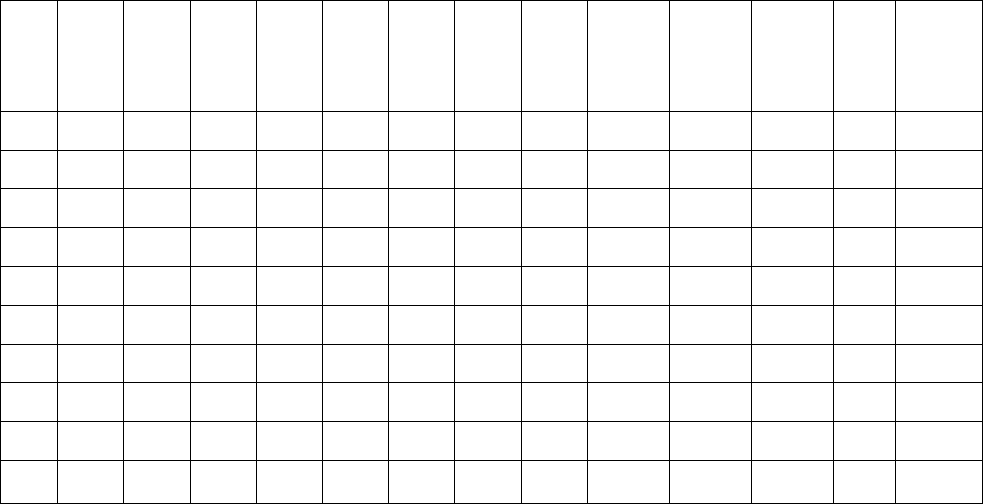

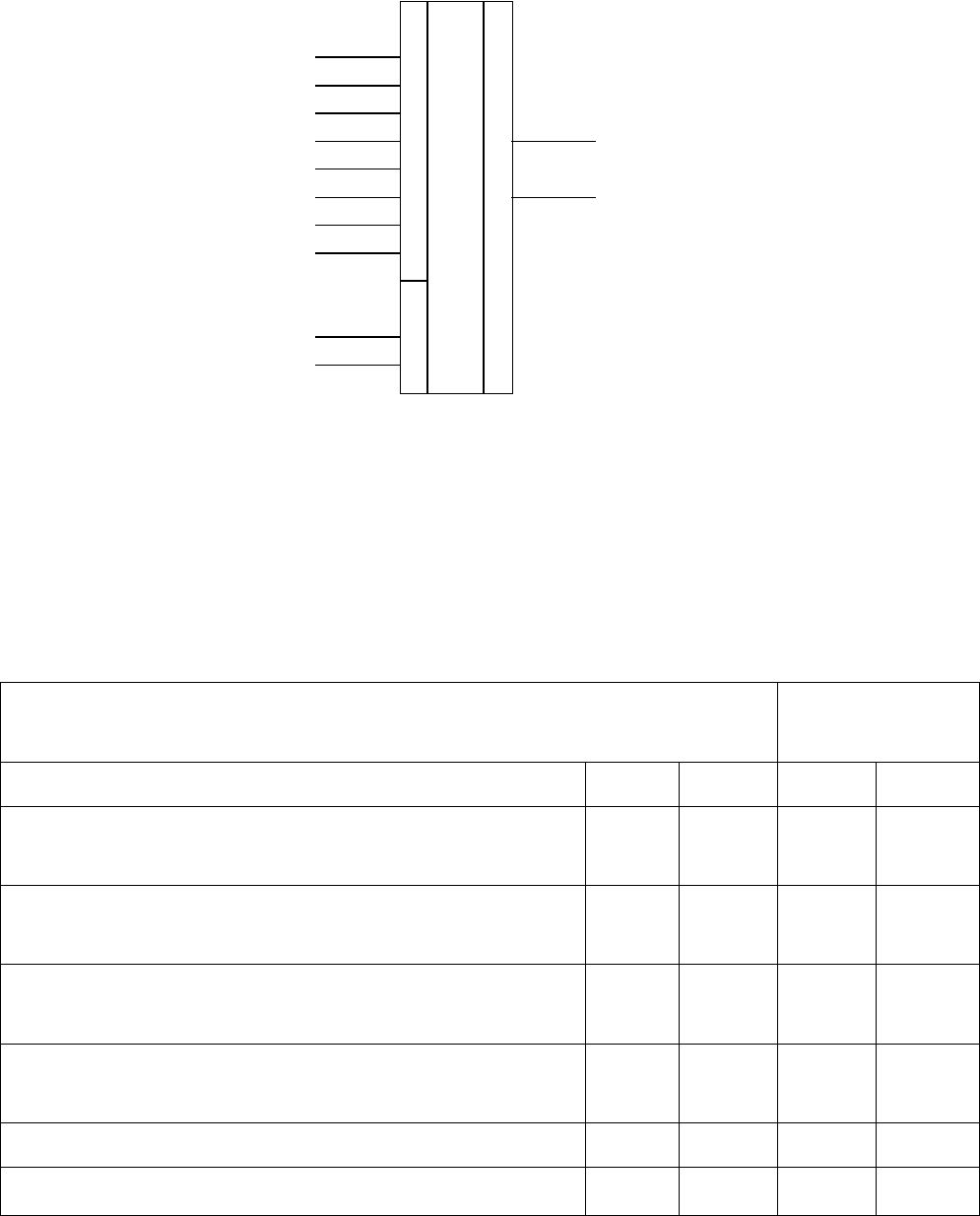

Микросхема К155КП1 (рис.3.1.4) имеет 16 информационных входов (DI0-

DI15), четыре селектирующих входа (А1, А2, А4, А8), один инверсный вход

стробирования Е и один инверсный выход.

Микросхема К155КП2 (рис.3.1.5) содержит в одном корпусе два

мультиплексора вида 4:1. Каждая секция имеет четыре информационных входа

DI0 -DI3, инверсный вход стробирования Е и прямой выход. Два селектирующих

входа А1 и А2 – общие для обеих секций.

Микросхемы К155КП7 (рис.3.1.6) и К155КП5 (рис.3.1.7) представляют собой

мультиплексоры вида 8:1. Они близки по логической структуре и принципу

действия. Различие состоит в том, что К155КП7 имеет инверсный вход

стробирования Е и два выхода – прямой и инверсный, тогда как в К155КП5 вход

стробирования и прямой выход отсутствуют.

27

8

7

6

5

4

3

2

1

23

22

21

20

19

18

17

16

15

14

13

11

9

DI

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

A

1

2

4

8

E

MUX

10

155

КП1

1

6

5

4

3

2

14

10

11

12

13

15

E

O

DI

0

0

01

0

2

03

A1

A

2

DI

1

0

11

1

2

13

E1

MUX

9

155

КП2

7

4

3

2

1

15

14

13

12

11

10

9

7

DI

0

1

2

3

4

5

6

7

A

1

2

4

E

MUX

5

155

КП7

6

5

4

3

2

1

13

12

11

10

9

8

DI

0

1

2

3

4

5

6

7

A

1

2

4

MUX

155

КП5

6

Рис.3.1.4 Рис.3.1.5 Рис.3.1.6 Рис.3.1.7

3.1.4. Сумматоры

Сумматоры, выполненные в виде самостоятельных микросхем, различаются в

основном разрядностью суммируемых двоичных чисел.

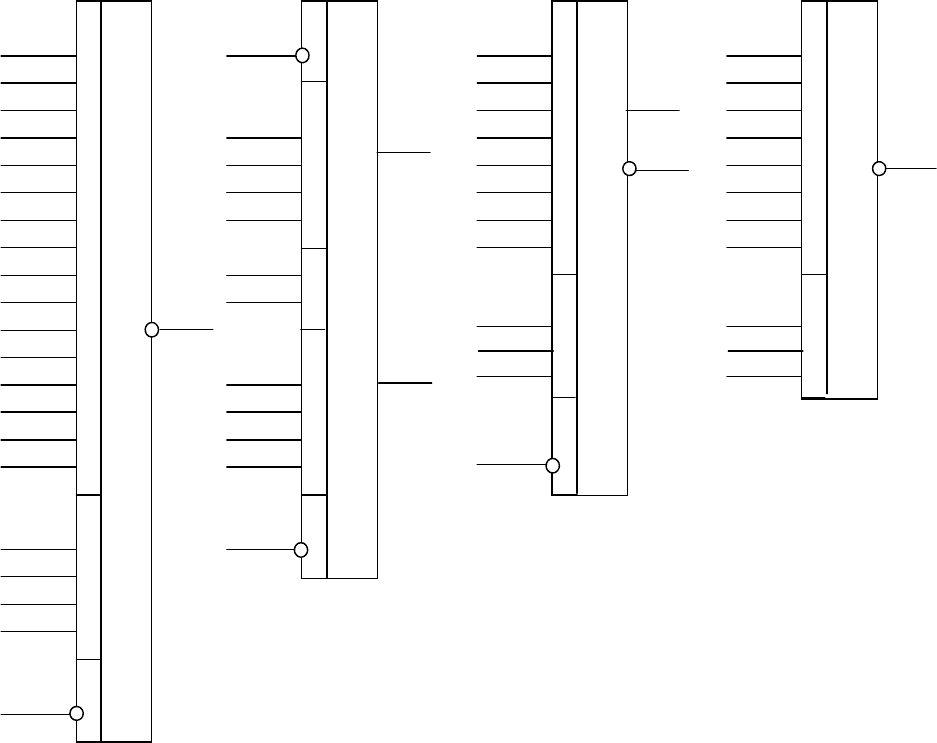

Микросхема К155ИМ2 (рис.3.1.8) представляет собой полный двухразрядный

сумматор, а микросхема К155ИМ3 (рис.3.1.9) – полный четырехразрядный

сумматор. Принцип их действия одинаков и основан на параллельном

суммировании данных в соответствующих разрядах операндов А и В с помощью

одноразрядного полного сумматора, построенного по схеме, аналогичной

рис.2.2.16, при последовательном переносе из разряда в разряд (рис.2.2.17). У

названных микросхем вход переноса есть только у младшего разряда (С0), а

выход – только у старшего (С2 – у ИМ2 и С4 – у ИМ3), что обеспечивает

возможность наращивания разрядности сумматоров. Для этого выход переноса

микросхемы, на которую подаются младшие разряды операндов А и В,

непосредственно соединяется со входом переноса микросхемы, обрабатывающей

старшие разряды операндов.

28

10

8

3

1

11

7

4

16

13

9

6

2

15

14

SM

ИМ3

А0

А1

А2

А3

В 0

В 1

В 2

В 3

С 0

S0

S1

S2

S3

C4

2

14

3

13

5

1

12

10

SM

ИМ2

А0

А1

В 0

В 1

С 0

S0

S1

C4

Рис.3.1.8 Рис.3.1.9

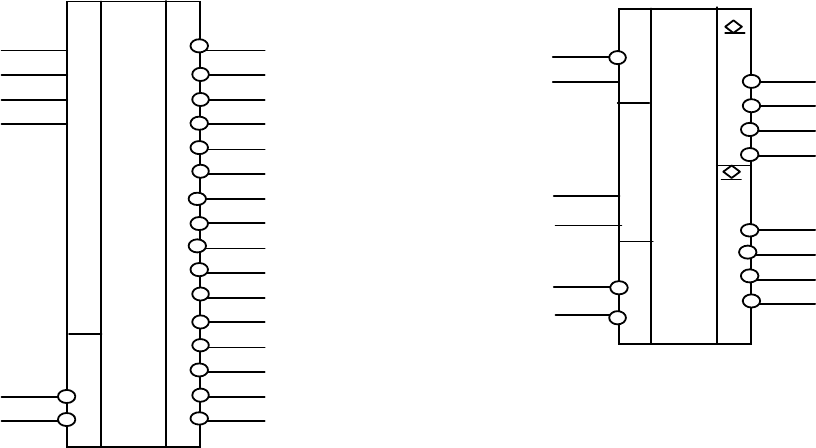

3.1.5. Цифровые компараторы

Цифровые компараторы осуществляют сравнение двух чисел, представленных

в двоичном коде. Многоразрядные компараторы, выполненные в виде

самостоятельных микросхем, строятся на основе схемы одноразрядного

компаратора, аналогичной рис.2.2.14. Два n-разрядных двоичных числа равны,

если попарно равны между собой все разряды этих чисел. Если, например, числа

А и В – четырехразрядные, то признаком их равенства будет А3=В3, А2=В2,

А1=В1, А0=В0. Применяя элемент сравнения для каждого разряда, факт

равенства чисел А=В имеет место в случае F=F3*F2*F1*F0=1. Если F=0, то А

≠

В.

Неравенство А>В обеспечивается в четырех случаях: 1) А3>В3 (А3 и В3 –

старшие разряды чисел А и В); 2) А3=В3 и А2>В2; 3) А3=В3, А2=В2, А1>В1; 4)

А3=В3, А2=В2, А1=В1, А0>В0. Очевидно, что для выполнения условия A<B

достаточно поменять местами А и В.

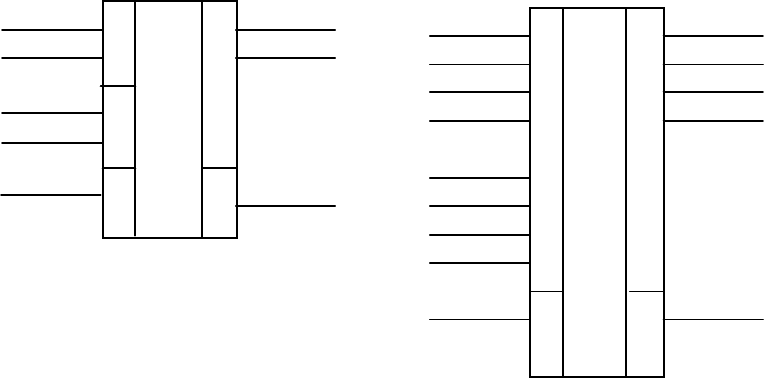

Микросхема К555СП1 (рис.3.1.10) выполняет поразрядное сравнение двух

четырехразрядных двоичных чисел, для подачи которых у нее имеется две группы

входов X0-X3 и Y0-Y3. Результаты сравнения отображаются в виде

соответствующих уровней на выходах >, =, <. Микросхема имеет три

расширяющих входа I(>), I(=), I(<), предназначенные для обеспечения

возможности наращивания разрядности сравниваемых чисел за счет

использования соответствующего количества микросхем без дополнительных

логических элементов. Зависимость логических уровней на выходах компаратора

от соотношения сравниваемых чисел и логических уровней на расширяющих

входах приведена в табл.3.1.2. Для увеличения разрядности компараторы можно

соединять каскадно и параллельно. При каскадном соединении выходы < и =

предыдущей микросхемы (младшие разряды) соединяются с соответствующими

входами расширения последующей. При этом способе соединения компараторов

задержки микросхем суммируются. При параллельном (пирамидальном)

соединении одноименные входы расширения компараторов, лежащих в

основании пирамиды, объединяются, а их выходы подаются на информационные

29

входы компаратора следующей ступени, который осуществляет сравнение

результатов сравнения в группах разрядов операндов. Параллельное соединение

обеспечивает большее быстродействие.

10

12

13

15

9

11

14

1

4

3

2

X

0

1

2

3

Y

0

1

2

3

I

>

=

<

5

6

7

>

=

<

= =

СП1

Рис.3.1.10

Таблица 3.1.2

X,Y

I(X>Y) I(X=Y I(X<Y) X>Y X=Y X<Y

X3>Y3 * * * * * * 1 0 0

X3<Y3 * * * * * * 0 0 1

X3=Y3 X2>Y2 * * * * * 1 0 0

X3=Y3 X2<Y2 * * * * * 0 0 1

X3=Y3 X2=Y2 X1>Y1 * * * * 1 0 0

X3=Y3 X2=Y2 X1<Y1 * * * * 0 0 1

X3=Y3 X2=Y2 X1=Y1 X0>Y0 * * * 1 0 0

X3=Y3 X2=Y2 X1=Y1 X0<Y0 * * * 0 0 1

X3=Y3 X2=Y2 X1=Y1 X0=Y0 1 0 0 1 0 0

X3=Y3 X2=Y2 X1=Y1 X0=Y0 0 0 1 0 0 1

X3=Y3 X2=Y2 X1=Y1 X0=Y0 * 1 * 0 1 0

X3=Y3 X2=Y2 X1=Y1 X0=Y0 1 0 1 0 0 0

X3=Y3 X2=Y2 X1=Y1 X0=Y0 0 0 0 1 0 1

3.1.6. Схемы формирования и контроля паритета

Эти схемы используются для получения простейшего помехоустойчивого

кода с проверкой паритета. При кодировании к n-разрядному кодируемому слову

добавляется один контрольный разряд с таким значением (0 или 1), чтобы сумма

единиц в (n+1)-разрядном слове всегда была четной (четный паритет) или всегда

30

нечетной (нечетный паритет). При декодировании слово контролируется по

выбранному типу паритета и при отклонении от него фиксируется ошибка.

Микросхема К155ИП2 (рис.3.1.11) построена аналогично схеме на рис.2.2.18,

отличаясь от нее разрядностью и дополнительными возможностями.

8

9

10

11

12

13

1

2

3

4

DI

0

1

2

3

4

5

6

7

EE

OE

M2

ИП2

РЕ

РО

5

6

Рис.3.1.11

Она имеет восемь информационных входов DI0-DI7, два входа задания типа

паритета ЕЕ и ОЕ и два взаимодополняющих выхода РЕ и РО. Сигналами на

входах ЕЕ и ОЕ можно обеспечить разные режимы работы микросхемы:

управление уровнями выходных сигналов, создание девятого информационного

входа, каскадирование микросхем с целью повышения разрядности кодируемых

слов. Функциональные свойства микросхемы характеризуются табл.3.1.3.

Таблица 3.1.3

Входы

Выходы

Число единиц на входах DI ЕЕ ОЕ РЕ РО

Четное

1 0 1 0

Нечетное

1 0 0 1

Четное

0 1 0 1

Нечетное

0 1 1 0

* 1 1 0 0

* 0 0 1 1