Базарова И.А. Архитектура процессорных систем

Подождите немного. Документ загружается.

11

нескольких, как при прямом отображении или наборно-ассоциативной

архитектуре. Естественно, последовательный перебор ячеек памяти тегов

отпадает — на это может уйти слишком много времени. Остается

параллельный анализ всех ячеек, что является сложной аппаратной задачей,

которая пока решена только для небольших объемов первичного кэша в

некоторых процессорах. Применение полностью ассоциативной архитектуры

во вторичном

кэше пока не предвидится.

Практика.

Вариант 1.

Построить кэш прямого отображения: строка 20 страницы 5 имеет

следующие признаки М=0, V=0. Объясните состояние строки.

Вариант 2.

Построить наборно-ассоциативный кэш: банк А, строка 38 страницы 9

имеет следующие признаки М=1, V=0. Банк В строка 17 страницы 22 имеет

следующие признаки М=0, V=0. Объясните состояние строки.

Вариант 3.

Построить кэш прямого отображения: строка

12 страницы 55 имеет

следующие признаки М=0, V=1. Объясните состояние строки.

Вариант 4.

Построить наборно-ассоциативный кэш: банк А, строка 38 страницы 9

имеет следующие признаки М=1, V=0. Банк В строка 26 страницы 212 имеет

следующие признаки М=0, V=0. Объясните состояние строки.

Вариант 5.

Построить кэш прямого отображения: строка 50 страницы 15 имеет

следующие признаки М=0, V=1. Объясните состояние строки.

Вариант 6.

Построить наборно-ассоциативный кэш: банк А, строка 48 страницы 59

имеет следующие признаки М=1, V=0. Банк В строка 7 страницы 100 имеет

следующие признаки М=0, V=0. Объясните состояние строки.

Вариант 7.

Построить кэш прямого отображения: строка 25 страницы 25 имеет

следующие признаки М=1, V=0. Объясните состояние строки.

Вариант 8.

Построить наборно-ассоциативный кэш: банк А, строка 7 страницы 9

имеет следующие признаки М=1, V=0. Банк В строка 39 страницы 78 имеет

следующие признаки М=0, V=0. Объясните состояние строки.

12

Вариант 9.

Построить кэш прямого отображения: строка 31 страницы 64 имеет

следующие признаки М=0, V=1. Объясните состояние строки.

Вариант 10.

Построить наборно-ассоциативный кэш: банк А, строка 80 страницы 5

имеет следующие признаки М=1, V=0. Банк В строка 117 страницы 106 имеет

следующие признаки М=0, V=0. Объясните состояние строки.

Контрольный тест 1.

1. Если процессор запрашивает процедуру обращения к памяти (чтение) при

кэш-промахе, то:

1) данный запрос не обслуживается

2) данный запрос обслуживается в любом случае

3) данный запрос обслуживается, если относится к кэшируемой области

4) данный запрос обслуживается без выхода на внешнюю шину

2. Для управления физической памятью используется:

1) сегментация

2) виртуализация

3) переадресация

4) страничное управление

3. В защищённом режиме сегменты распределяет:

1) BIOS

2) операционная система

3) служебное программное обеспечение

4) прикладное программное обеспечение

4. Дескрипторы, доступные всем задачам, хранятся в:

1) локальной DT

2) глобальной DT

3) DT прерываний

5. При обращении процессора к выгруженной странице программный

обработчик организует:

1) передачу сообщений МП кэш-памяти

2) управление кэшированием

3) свопинг

4) исключение

PF

6. Признак модифицированности строки не требует:

1) политика WT (сквозная запись)

2) политика WB (обратная запись)

13

7. Проблема интенсивной холостой работы кэш-памяти при затребовании

блоков памяти, кратных размеру страницы, присуща:

1) наборно-ассоциативной архитектуре кэш

2) полностью ассоциативной архитектуре кэш

3) кэш прямого отображения

8. Принцип параллельной работы присущ:

1) кэш-памяти прямого отображения

2) секторированной кэш-памяти

3) наборно-ассоциативной памяти

Контрольная работа

№ 2.

Взаимодействие процессора с компонентами системы и периферийными

устройствами.

Теория.

Каждый процессор имеет свою систему команд. Команда представляет

собой определенную последовательность двоичных разрядов и содержит код

операции и информацию об операндах.

Формат команды – это совокупность сведений, которые для каждой

команды процессора задают: ее длину, состав, назначение.

В системе команд любого

процессора можно выделить следующие

основные группы команд:

1. пересылка данных между RAM и регистром процессора (

RGRAM ↔ ).

2. Арифметико-логические операции.

3. Управление ходом выполнения программы

4. Связь с подпрограммами

5. Операции над регистровыми структурами (сдвиг данных в регистрах,

очистка регистров и т.д.).

6. Группа команд, управляющих I/O (вводом/выводом).

7. Специальные системные команды.

Устройство управления процессора в строгой последовательности в

рамках тактовых и цикловых временных интервалов

осуществляет:

1. Выборку команды

2. Её интерпретацию с целью анализа формата, служебных признаков и

вычисления адреса операнда (операндов).

3. Установление временной последовательности всех функциональных

управляющих сигналов.

4. Генерацию управляющих импульсов и передачу их на управляющие

шины функциональных частей ПК.

5. Анализ результата операции и изменение своего состояния для

определения адреса

следующей команды.

14

Рассмотрим процесс выполнения команд МП на примере структурной

схемы (без устройств ввода-вывода):

Рис. 3. Структурная схема взаимодействия МП с компонентами системы.

На данной схеме толстая линия – это магистраль адреса и магистраль

данных, тонкие стрелки – сигналы от шины управления, пунктирные линии –

непосредственное воздействие электрического сигнала на соответствующий

компонент. Связи РОН и генератора не показаны.

Предположим, что управляющие сигналы устройств управления

соответствуют таблице:

Таблица 1. Управляющие сигналы устройств управления.

№

линии

Назначение линии

1 Наращивание содержимого программного счетчика

2 Чтение информации из программного счетчика и выдача ее на МА

3 Запись информации с МД в регистр команд

4

Чтение адреса операции из регистра команд и выдача этого адреса на

МА

15

5 Запись информации с МА в регистр адреса памяти

6 Чтение содержимого ячейки памяти и выдача его на МД

7 Запись информации с МД в ячейку памяти

8 Запись информации с МД в операционный блок

9 Прибавление 1 к содержимому в операционном блоке

10 Инвертирование содержимого операционного блока

11

Суммирование содержимого операционного блока с содержимым

аккумулятора

12 Запись информации из операционного блока в аккумулятор

13 Чтение информации из аккумулятора и выдача её на МД

Пример 1: выполнить команду чтения числа из заданной ячейки,

прибавить к нему единицу и сохранить результат в аккумуляторе.

Таблица 3. Решение примера 1.

Цикл генератора

тактовой частоты,

F

Выполняемая микрооперация

Активны

е линии

МУ

1. Адрес команды из программного

счетчика пересылается в регистр

адреса памяти

2, 5

I –cycle

2. Код команды пересылается из

ячейки памяти по МД в регистр

команд. Наращивание содержимого

программного счетчика

3, 6

3. Пересылка адреса операнда из

регистра команд в регистр адреса

памяти

4, 5

4. Пересылка операнда из ячейки

памяти в операционный блок

6,8

5. Выполнение заданной операции –

прибавление 1.

9

Общее время выполнения команд

E –cycle

6. Запись результата операции в

аккумулятор (АС), наращивание PC

12,1

После запуска программы, МП выполняет следующие циклические

действия:

1. Извлекает из основной памяти команду, адрес которой находится в

счетчике команд. Код команды помещается МП в регистр команд.

2. Декодирование извлеченной команды, определение ее кода и адресов

операндов. Если операнды отсутствуют или находятся в МП, то МП

16

переходит к действию 4. Если операнды находятся в памяти, то к

действию 3.

3. МП извлекает из основной памяти необходимые операнды и

запоминает их в регистрах.

4. Процессор выполняет операцию по заданному коду. Если результат

операции не нужно помещать в основную память, то процессор

переходит к действию 6, если нужно, то к действию 5.

5.

Сохранение результата операции в основной памяти.

6. Вычисляет адрес следующей команды программы и запоминает его в

регистре счетчика команд.

Существуют два метода выработки управляющих сигналов:

- Программный метод. Жесткая логика управления, каждой операции

соответствует свой набор логических схем, вырабатывающих

определенные функциональные сигналы для выполнения

микроопераций.

- Микропрограммный способ. Гибкая логика

управления. В состав УУ

вводится запоминающее устройство, которое содержит

микрокоманды. Каждой микрокоманде соответствует свой

функциональный сигнал, по которому выполняется микрооперация. В

качестве ЗУ для УУ используется ПЛМ.

Взаимодействие с внешними устройствами.

Архитектура ПК определяется свойствами, которые обеспечивают

возможность функционирования ПО управляющего периферийным

оборудованием. Программы могут взаимодействовать с устройствами 3

способами

:

1. Используя вызовы функций ОС

2. Используя вызовы функций BIOS

3. Непосредственно взаимодействуя с регистрами периферийных

устройств или контроллерами интерфейса.

Процессоры класса 8086 имеют раздельную адресацию памяти и портов

ввода-вывода, за счет сигналов чтения ввод-вывод и запись ввод-вывод (

и

) на шинах ввода-вывода, которые порождаются инструкциями ввода-

вывода.

Сигналы

и вырабатываются также в циклах DMA (прямого

доступа в память), однако в этом случае на шине адреса будет присутствовать

адрес памяти, в который производится доступ, а не адрес порта.

Инструкции ввода-вывода предусматривают:

1. Непосредственная адресация порта

2. Косвенное обращение через регистр

17

В реальном режиме МП программе доступно все пространство адресов

ввода-вывода. В защищенном режиме, возможно, программно ограничить

доступное пространство ввода-вывода, а внутри этой области можно также

программно разрешить или запретить доступ к конкретному устройству. Размер

выделяемой области и карта разрешенных портов (IO Permission Bitmap)

задаются ОС в дескрипторе сегмента состояния задачи (TSS).

Порты

ввода-вывода (ПВВ) – это модули для реализации взаимодействия

между МПС и внешней средой.

ПВВ – это адресуемые одно- или двунаправленные буферные регистры,

предназначенные для построения программного интерфейса.

Для адресации портов используется шина адреса или ее часть.

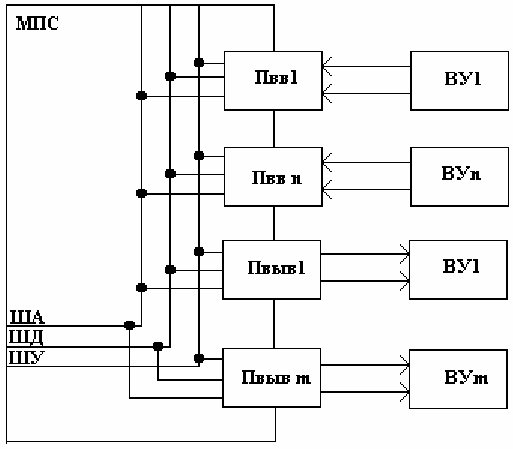

Рис. 4. Общая структурная схема портов ввода-вывода.

Несколько портов вывода могут иметь совпадающие адреса, при этом

операции записи будут нормально отработаны.

Если порты ввода имеют совпадающие адреса, то при операции

считывания будет происходить конфликт на шине.

Если такие порты будут находится на разных физических шинах, то

конфликт исключается за счет буфера данных.

Существует три типа обмена между МПС и внешними устройствами:

1. Программно-управляемый обмен

2. Обмен данными по прерываниям

3. Прямой доступ к памяти

18

Аппаратные прерывания.

Аппаратные прерывания обеспечивают реакцию МП на события,

происходящие асинхронно по отношению к исполняемому программному коду.

Существует 4 источника прерываний:

1. Внутренние прерывания процессора и сопроцессора (исключения)

2. Немаскируемые внешние прерывания

3. Маскируемые внешние прерывания

4. Программно вызываемые прерывания (не относятся к прерываниям,

специфический вызов процедуры)

Условие возникновения прерываний

проверяется процессором на границе

инструкций – все шинные операции текущей инструкции будут завершены до

начала обработки прерывания.

При обработке прерывания МП сохраняет в стеке слово состояния (PSW),

сбрасывает флаг разрешения прерываний (IF) и вызывает процедуру

обслуживания, точка входа в которую описана в таблице прерываний, которая

хранится в RAM. Процедура обработки прерывания завершается по инструкции

IRET, по которой из стека восстанавливается содержимое сохранённых

регистров.

Если во время обслуживания прерывания случайно изменить состояние

указателя или содержимого стека, то PC «зависнет».

Причиной «зависания» может также являться переполнение стека. Это

возникает в случае вложенных прерываний.

Внутренние прерывания процессора генерируются при возникновении

особых условий выполнения текущей инструкции. Под такие прерывания

отведены

первые 32 вектора в таблице прерываний, однако некоторые из них

«пересекаются» с внешними и программными прерываниями, что является

причиной возникновения некоторых проблем при программировании.

Контекстное переключение – это процесс сбора и записи содержимого

регистров процессора в основную память.

Немаскируемые прерывания.

Обладают наивысшим приоритетом независимо от состояния флага

разрешения прерываний: IF

Источники немаскируемых

прерываний:

1. NMI# (# инверсный)

2.SMI#

NMI# - схемы контроля памяти. Когда выполняется обработка

прерываний по сигналу NMI#, то вложенные прерывания запрещены.

SMI# - прерывание SMI возникает от схем CHIPSET, участвующих в

управлении энергопотреблением. Это прерывание обладает наивысшим

приоритетом.

19

В случае прерывания SMI процессор не обращается к таблице прерываний, а

переходит в специальный режим SMM (System Management Mode) – режим

системного управления. Таким режимом обладают только процессоры

последнего поколения. Этот режим использует отдельное адресное

пространство, которое является параллельным основному пространству памяти

SMRAM. Память SMRAM реализуется как часть физической оперативной

памяти (DRAM) или отдельная микросхема энергонезависимой памяти.

Размеры SMRAM: min – 32Кб

max – 4 Гб

Сначала в памяти SMRAM автоматически сохраняется контекст процессора,

после этого выполняется код по определенному адресу в памяти SMRAM.

Обычные прерывания запрещены, обычная память процессору недоступна.

Выход из режима SMM происходит по инструкции RSM. По этой инструкции

автоматически восстанавливается сохраненный контекст процессора, процессор

входит в обычное адресное пространство и выполняет прерванную программу.

Маскируемые прерывания.

Такие прерывания обслуживает контроллер программно совместимый с

процессором, имеющий 8 входов запросов на прерывания (IRQх) от внешних

устройств, по которым запросы обрабатываются, и один выход запроса

(INTR), по которому запрос поступает на одноименный вход процессора.

Сигнал INTR с выхода контроллера поступает на одноимённый вход

процессора и процессор, обрабатывая это запрос,

формирует шинный цикл

подтверждения прерывания INTR. В этом цикле контроллер передаёт по шине

данных восьмиразрядный вектор прерывания. Этот вектор является номером в

таблице прерываний.

Контроллеры, совместимые с процессорами Intel, могут подключаться

каскадно (можно подключить 64 внешних устройства).

Линии прерывания являются самым дефицитным ресурсом для

компьютерной системы, поэтому, желательно использовать эти линии

разделяемо, между

несколькими устройствами. Этот способ для шин ISA

невозможен, но этот способ реализован для шин PCI.

Для шины PCI используются 4 линии запроса: A, B, C, D. Срабатывание

идет по низкому уровню. Этим разделение линий управляют опции BIOS, а

также PnP.

В мультипроцессорных системах система аппаратных прерываний более

сложная. Для реализации такой системы процессоры класса Pentium имеют

встроенные контроллеры прерываний (APIC), которые

соединяются шиной

APIC.

20

Режим прямого доступа к памяти.

ПДП (DMA) – это метод обмена данными периферийного устройства с

памятью без участия процессора.

При обычном программном обмене (PIO) для пересылки данных,

например, из порта в память выполняются следующие шаги:

1. Процессор генерирует цикл чтения порта, выставляя адрес порта и

формируя сигнал (IORD#). Данные из порта считываются

процессором

во внутренний шинный буфер.

2. Процессор генерирует шинный цикл записей в память, выставляя

адрес ячейки памяти, и формируя сигнал MEMWR#. Данные из

внутреннего шинного буфера записываются в память.

3. Эти шаги автоматически повторяются с изменением адреса памяти. Во

время PIO процессор занят.

Недостаток этого метода: во время PIO процессор постоянно занят.

В режиме DMA

процессор инициализирует контроллер DMA.

Основные функции контроллера DMA:

1. Определяет приоритет запроса на прерывание.

2. Прерывает рабочую программу процессора.

3. Прерывает программы обслуживания обмена информацией внешних

устройств с младшим приоритетом.

4. Вырабатывает сигнал «Разрешение обмена» и адресует внешние

устройства.

5. Определяет режим записи или чтения.

6. Восстанавливает ход рабочей программы процессора по

окончанию

обмена.

Для интерфейса периферийного устройства каждый канал DMA

представляется как сигналы:

1. Запрос обмена (DRQх)

2. Подтверждение обмена (

DACK х)