НУК, 10 стр. Дисципліна - "Комп'ютеризоване проектування цифрових

електронних схем".

У архіві знаходяться як звіт з лабораторної, так і ісходники зі схемами та часовими діаграмами.

Дослідження принципу роботи суматора та помножувача чисел в прямому та додатковому кодах. Розробка цих об’єктів за допомогою мови VHDL. Лабораторна виконана у САПР Active-HDL.

Завдання:

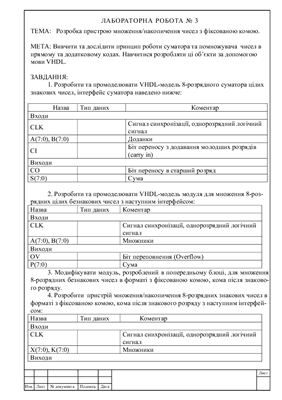

Розробити та промоделювати VHDL-модель 8-розрядного суматора цілих знакових чисел.

Розробити та промоделювати VHDL-модель модуля для множення 8-розрядних цілих беззнакових чисел.

Модифікувати модуль, розроблений в попередньому блоці, для множення 8-розрядних беззнакових чисел в форматі з фіксованою комою, кома після знакового розряду.

Розробити пристрій множення/накопичення 8-розрядних знакових чисел в форматі з фіксованою комою, кома після знакового розряду

У архіві знаходяться як звіт з лабораторної, так і ісходники зі схемами та часовими діаграмами.

Дослідження принципу роботи суматора та помножувача чисел в прямому та додатковому кодах. Розробка цих об’єктів за допомогою мови VHDL. Лабораторна виконана у САПР Active-HDL.

Завдання:

Розробити та промоделювати VHDL-модель 8-розрядного суматора цілих знакових чисел.

Розробити та промоделювати VHDL-модель модуля для множення 8-розрядних цілих беззнакових чисел.

Модифікувати модуль, розроблений в попередньому блоці, для множення 8-розрядних беззнакових чисел в форматі з фіксованою комою, кома після знакового розряду.

Розробити пристрій множення/накопичення 8-розрядних знакових чисел в форматі з фіксованою комою, кома після знакового розряду