НУК, дисциплина - "Автоматизированное проектирование цифровых

устройств".

Имеются как отчёты по лабораторным, так и исходники с временными диаграммами. Задания: Использование Active-HDL: моделирование:

Приобретение навыков создания и компилирования VHDL-модели устройства, моделирования его, а также изучение применения стимуляторов для моделирования устройств в среде Active-HDL. Разработка программы и моделирование декодера для жидкокристаллического индикатора:

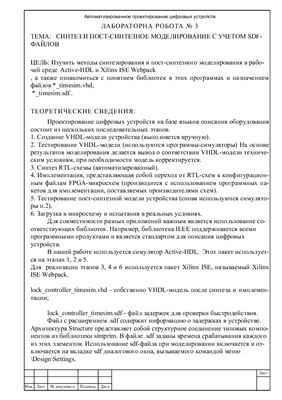

Изучение методов описания поведения объектов с помощью архитектур и процессов, методов применения оператора выбора case. Усвоение методики моделирования поведения объектов в САПР Active-HDL. Синтез и пост-синтезное моделирование с учетом sdf-файлов:

Изучение методов синтезирования и пост-синтезного моделирования в рабочей среде Active-HDL и Xilinx ISE Webpack, а также ознакомление с понятием библиотек в этих программах и назначением файлов *_timesim.vhd, *_timesim.sdf. Моделирование транспортной и инерциальной задержек времени:

Описание транспортной и инерциальной задержки времени с помощью Active-HDL, выяснение принципиального отличия между ними. Моделирование режима ожидания в цифровых устройствах с помощью оператора wait:

Получение практических навыков применения оператора wait при моделировании разнообразных режимов ожидания в Active-HDL. Использование сравнения временных диаграмм. Разработка программы и моделирование параллельного и последовательного регистров:

Усвоение принципов работы параллельного и последовательного регистров. Описание синхронизированных процессов и использование циклических операторов при описании поведения объектов при помощи VHDL. Проектирование сканера клавиатуры применяя диаграммы конечных автоматов для описания оьъектов в САПР Active-HDL:

Описание принципа работы сканера клавиатуры. Проектирование цифровых устройств с помощью конечных автоматов средствами Active-HDL. З Ы. Отчёты по 2й и 7й лабе написаны на украинском языке.

Имеются как отчёты по лабораторным, так и исходники с временными диаграммами. Задания: Использование Active-HDL: моделирование:

Приобретение навыков создания и компилирования VHDL-модели устройства, моделирования его, а также изучение применения стимуляторов для моделирования устройств в среде Active-HDL. Разработка программы и моделирование декодера для жидкокристаллического индикатора:

Изучение методов описания поведения объектов с помощью архитектур и процессов, методов применения оператора выбора case. Усвоение методики моделирования поведения объектов в САПР Active-HDL. Синтез и пост-синтезное моделирование с учетом sdf-файлов:

Изучение методов синтезирования и пост-синтезного моделирования в рабочей среде Active-HDL и Xilinx ISE Webpack, а также ознакомление с понятием библиотек в этих программах и назначением файлов *_timesim.vhd, *_timesim.sdf. Моделирование транспортной и инерциальной задержек времени:

Описание транспортной и инерциальной задержки времени с помощью Active-HDL, выяснение принципиального отличия между ними. Моделирование режима ожидания в цифровых устройствах с помощью оператора wait:

Получение практических навыков применения оператора wait при моделировании разнообразных режимов ожидания в Active-HDL. Использование сравнения временных диаграмм. Разработка программы и моделирование параллельного и последовательного регистров:

Усвоение принципов работы параллельного и последовательного регистров. Описание синхронизированных процессов и использование циклических операторов при описании поведения объектов при помощи VHDL. Проектирование сканера клавиатуры применяя диаграммы конечных автоматов для описания оьъектов в САПР Active-HDL:

Описание принципа работы сканера клавиатуры. Проектирование цифровых устройств с помощью конечных автоматов средствами Active-HDL. З Ы. Отчёты по 2й и 7й лабе написаны на украинском языке.