НУК, дисциплина - Автоматизированное проектирование цифровых

устройств.

В архиве содержатся как отчёты по лабораторной, так и исходники со схемамами и временными диаграммами.

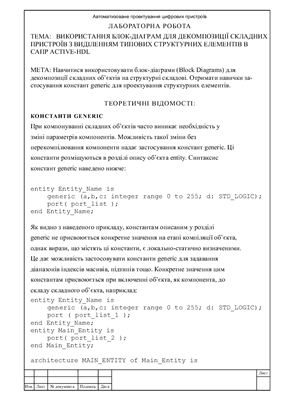

Тема: Використання блок-діаграм для декомпозиції складних пристроїв з виділенням типових структурних елементів в САПР Аctive-HDL.

Мета: Навчитися використовувати блок-діаграми (Block Diagrams) для декомпо-зиції складних об’єктів на структурні складові. Отримати навички застосування констант generic для проектування структурних елементів.

ЗАВДАННЯ: Створити блок – генератор сигналів для рідкокристалічного індикатора.

Інтерфейс об’єкта – генератора сигналів містить:

вхідний 16-розрядний порт Х типу std_logic_vector (15 downto 0), на який у двійково-десятковій формі подається 4-розрядне десяткове число (на кожний деся-тковий розряд по 4 двійкові розряди); вхідний сигнал синхронізації CLK; один 7-розрядний вихідний порт LED(6:0), що підключається безпосередньо до відповід-них розрядів чотирьох рідкокристалічних індикаторів; один вихідний порт AN(3:0), що безпосередньо підключається до всіх розрядів рідкокристалічних індикаторів.

Під час опису поведінки об’єкта на VHDL було використано Редактор Блок-схем (Block-diagram Editor), який значно полегшує роботу при описі складного об’єкта, представляючи його структуру спочатку у графічному виді, а потім генеруючи загальний код, ураховуючи туди опис та поведінку складових компонентів.

Був зроблений синтез та імплементація за допомогою Xilinx ISE Webpack і за допомогою якого програма була випробувана на програмованій FPGA мікросхемі Spartan-

3. У зв’язку з певними технічними вимогами до цієї схеми програма була відкоригована. А саме: вихідний сигнал LED(6:0), який подається безпосередньо на відповідні розряди рідкокристалічних індикаторів, був інвертований; частота робо-ти була знижена за допомогою перероблення принципу дії лічильника, тобто доба-вленням додаткових розрядів до внутрішнього сигналу лічильника з метою упові-льнення його роботи.

В архиве содержатся как отчёты по лабораторной, так и исходники со схемамами и временными диаграммами.

Тема: Використання блок-діаграм для декомпозиції складних пристроїв з виділенням типових структурних елементів в САПР Аctive-HDL.

Мета: Навчитися використовувати блок-діаграми (Block Diagrams) для декомпо-зиції складних об’єктів на структурні складові. Отримати навички застосування констант generic для проектування структурних елементів.

ЗАВДАННЯ: Створити блок – генератор сигналів для рідкокристалічного індикатора.

Інтерфейс об’єкта – генератора сигналів містить:

вхідний 16-розрядний порт Х типу std_logic_vector (15 downto 0), на який у двійково-десятковій формі подається 4-розрядне десяткове число (на кожний деся-тковий розряд по 4 двійкові розряди); вхідний сигнал синхронізації CLK; один 7-розрядний вихідний порт LED(6:0), що підключається безпосередньо до відповід-них розрядів чотирьох рідкокристалічних індикаторів; один вихідний порт AN(3:0), що безпосередньо підключається до всіх розрядів рідкокристалічних індикаторів.

Під час опису поведінки об’єкта на VHDL було використано Редактор Блок-схем (Block-diagram Editor), який значно полегшує роботу при описі складного об’єкта, представляючи його структуру спочатку у графічному виді, а потім генеруючи загальний код, ураховуючи туди опис та поведінку складових компонентів.

Був зроблений синтез та імплементація за допомогою Xilinx ISE Webpack і за допомогою якого програма була випробувана на програмованій FPGA мікросхемі Spartan-

3. У зв’язку з певними технічними вимогами до цієї схеми програма була відкоригована. А саме: вихідний сигнал LED(6:0), який подається безпосередньо на відповідні розряди рідкокристалічних індикаторів, був інвертований; частота робо-ти була знижена за допомогою перероблення принципу дії лічильника, тобто доба-вленням додаткових розрядів до внутрішнього сигналу лічильника з метою упові-льнення його роботи.